# IC600YB827 New In Stock! GE Fanuc

http://www.pdfsupply.com/automation/ge-fanuc/ge-series-six-6/IC600YB827

# Ge Series Six 6 1-919-535-3180

High Speed Counter Module IC600Y IC600YB

www.pdfsupply.com

Email:

sales@pdfsupply.com

#### TABLE 2. SPECIFICATIONS

Dimensions: Circuit Board 8.15 x 11.0 x 1.20 (inches) 208 x 280 x 31 (mm)15.0V Faceplate 12.46 x 1.175 (inches)0.2V 317 x 30 (mm) Power requirements 5 VDC, 1.1A maximum Supplied by I/O rack power supply Units of Load = 19User Supplied 1 o-3ov TTL Voltage 5V + 0.20 VDC 10-30V  $\pm$  .5 VDC Ripple 100mv Ιv Current 400ma 400ma Timing Characteristics Input Pulse Rate: DC to 50KHz (square wave) Input Pulse Rate with filter selected: DC to 100Hz (square wave) Marker Pulse Width: 5 usec (minimum) Response time for outputs 1-4 to incoming pulses: 500 usec (typ) TTL Single Ended Sink Input Characteristics Maximum Input Voltage: 5.5V Minimum Turn-On Voltage: 2.0V Minimum Input Voltage: -1.5V Maximum Turn-Off Voltage: 0.8V Input Impedance: 1000 ohms (TYP) Minimum Low Level Input Current: -6.0ma (sinking)

5 Volt Differential Input Characteristics Inputs are RS422 compatible Maximum Input Voltage:  $\pm$  15.0V Common Mode Voltage Range:  $\pm$  7.0V Threshold Sensitivity:  $\pm$  0.2V Input Impedance: 115 ohms (TYP.) Minimum Input Current:  $\pm$  3.0ma

10-30V single ended source input characteristics.

Maximum Input Voltage: 33V Minimum Turn-On Voltage: 9V Minimum Input Voltage: -20V Maximum Turn-off Voltage: 2V Input Impedance: 3800 ohms (TYP)

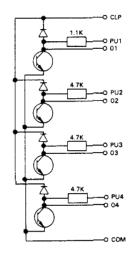

Output Characteristics Outputs are open collector with a common clamp diode (CLP) provided for optional connection to positive source.

Pull-up resistors provided for outputs. PUl - 1100 ohm. PU2, PU3, outputs. PU4 = 4700 ohm

Maximum Supply Voltage: 30 VDC

Maximum On-State Voltage Drop: 0.4V for: I 50ma 0.70 for: 1250ma

Maximum Output Current: 250ma continuous 500ma peak for 1 second

- Operating Temperature: 0-60°C (at outside of rack)

- Storage Temperature: -20° to + 80°C

- Humidity: 5-95% (non-condensing)

- Altitude: Up to 10,000 feet above sea level

# INSTALLATION

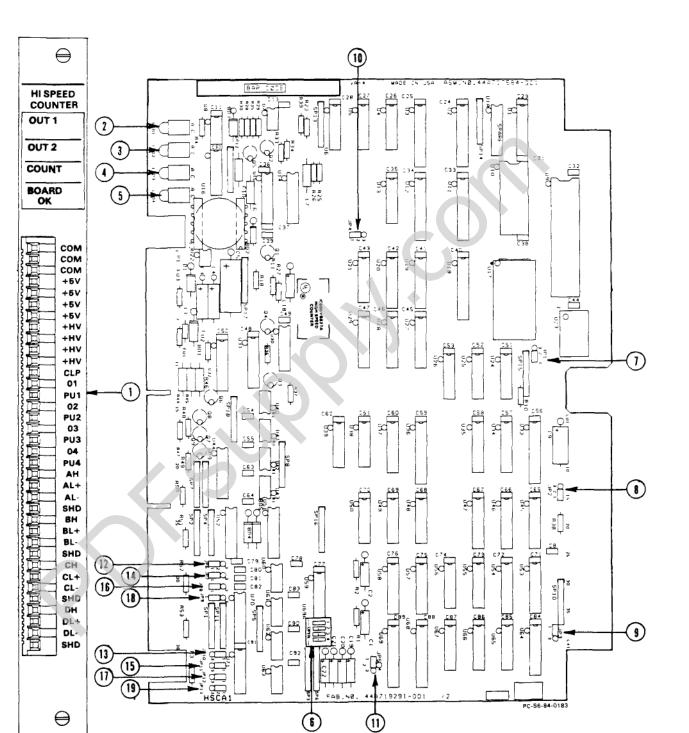

The High Speed Counter module can be installed in an I/O rack or in a Model 60 CPU rack. Before installing the module, the dual-in-line-package (DIP) switches immediately behind the card slot on the rack backplane should be set to reserve a group of 32 consecutive bits in the appropriate Input AND Output Status Tables of the CPU. For specific DIP switch settings, refer to Figure 1.

You should also set the circuit board jumpers and dip switch to configure the module for your particular application. Refer to Figure 2 for description of all user settings.

We recommend that you use the extraction/insertion tool furnished with your CPU to remove or install the circuit board. With the board in place in the rack, the edge connector on the faceplate should be slipped over the circuit board so that proper contact is made. You can then secure the faceplate to the rack using the thumbscrews at the top and bottom. Refer to Figure 3 and 4 for typical user output connections to this module. Figure 7 shows the general internal design for the four output circuits, while Figures 5 and 6 contains the general internal design for the input circuits.

#### WARNING

Voltages from user field devices could be present on the faceplate terminals, even if the power supply in the I/O rack is off. Care should be taken when handling the faceplate of this module or any wires connected to it.

|   | OUTPUT<br>NUMBER |   |   |   | _ | ICH<br>ON | OUTPUT<br>NUMBER | OUTPUT DIP SWIT<br>NUMBER POSITIO |   |   |   |   |          |   |    |    |    |     |

|---|------------------|---|---|---|---|-----------|------------------|-----------------------------------|---|---|---|---|----------|---|----|----|----|-----|

| ſ |                  | 7 | 6 | 5 | 4 | 3         |                  | 7                                 | 6 | 5 | 4 | 3 |          | 7 | 6  | 5  | 4  | 3   |

|   | 1- 32            |   |   |   |   |           | 353-384          |                                   | x |   | x | x | 705-736  | x |    | x  | x  |     |

|   | 33- 64           |   |   |   |   | x         | 385-416          |                                   | x | x |   |   | 737-768  | X |    | x  | x  | x   |

|   | 65-96            |   |   |   | x |           | 417-448          |                                   | x | x |   | х | 769-800  | X | х  |    |    |     |

|   | 97-128           |   |   |   | X | X         | 449-480          |                                   | Х | X | x |   | 801-832  | X | X  |    |    | X   |

| ſ | 129-160          |   |   | X |   |           | 481-512          |                                   | X | X | X | X | 833-864  | X | x  |    | x  |     |

| I | 161-192          |   |   | x |   | X         | 513-544          | X                                 |   |   |   |   | 865-896  | X | x  |    | x  | х   |

| ſ | 193-224          |   |   | X | X |           | 545-576          | X                                 |   |   |   | X | 897-928  | X | X  | X  |    |     |

| ſ | 225-256          |   |   | X | X | X         | 577-608          | X                                 |   |   | X |   | 929-960  | X | x  | X  |    | X   |

|   | 257-288          |   | X |   |   |           | 609-640          | X                                 |   |   | X | X | 961-992  | X | X  | X  | X  |     |

|   | 289-320          |   | x |   |   | x         | 641-672          | x                                 |   | x |   |   | 993-1024 | X | х  | х  | х  | х   |

| ſ | 321-352          |   | x |   | X |           | 673-704          | x                                 |   | x |   | x | 5        |   | (N | ΟT | US | ED) |

X = Switch in OPEN Position (Depressed to the Left) Switches No. 1 and No. 2 should be in CLOSED Position

FIGURE 1. DIP SWITCH SETTINGS FOR I/O RACK

### Figure 2. CONFIGURABLE USER SETTINGS (Part 1 of 3)

5

| ITEM                  | FUNCTION FOR USER SE                                  | ETTINGS                                                                                                                                                                                                                                                                                                                                                 |

|-----------------------|-------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0<br>0<br>0<br>4<br>0 | LED for OUT 2; when ON,<br>LED for count; when blinki | point connector.<br>indicates output 1 is energized.<br>indicates output 2 is energized.<br>ng, indicates pulses are being received.<br>DN, Board passed diagnostic test.                                                                                                                                                                               |

| ITEM                  | DIP SWITCH                                            | FUNCTION                                                                                                                                                                                                                                                                                                                                                |

| 6                     | SW1 Open*<br>SW2 Open*<br>SW3 Open*<br>SW4 Closed     | Input A Filter<br>Input B Filter<br>Input C Filter<br>Input D Filter                                                                                                                                                                                                                                                                                    |

|                       |                                                       | Set to Closed position if input is connected to a device using dry contacts, or other non-solid state device.                                                                                                                                                                                                                                           |

| ITEM                  | JUMPERS                                               | FUNCTION FOR USER SETTINGS                                                                                                                                                                                                                                                                                                                              |

| 7                     | JP1                                                   |                                                                                                                                                                                                                                                                                                                                                         |

|                       | 1-2*<br>2-3                                           | Run - Normal Use<br>Factory Test                                                                                                                                                                                                                                                                                                                        |

| 8                     | JP2                                                   |                                                                                                                                                                                                                                                                                                                                                         |

|                       | 1-2*                                                  | If the CPU RESET signal is high, the counter will continue to function, except outputs 1 thru 4 will be forced off regardless of their previous state. When the CPU once again becomes operational, the four outputs will return to their conditional state as determined by the enable/disable and latch/unlatch bits and the preset comparison state. |

|                       | 2-3                                                   | If the CPU RESET signal is high, the counter will continue to function, and will retain full control over its four outputs.                                                                                                                                                                                                                             |

| 9                     | JP3                                                   |                                                                                                                                                                                                                                                                                                                                                         |

|                       | 1-2*<br>2-3                                           | Not Used<br>Not Used                                                                                                                                                                                                                                                                                                                                    |

\* Factory Setting

FIGURE 2. CONFIGURABLE USER SETTINGS (PART 2 OF 3)

| ITEM     | DIP SWITCH                                            | FUNCTION                                                                                              |

|----------|-------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

| (10)     | JP4                                                   |                                                                                                       |

| 0        | 1-2*                                                  | Encoder mode - Quadrature Encoder with optional marker                                                |

|          | 2-3                                                   | Counter mode - Square wave pulse input                                                                |

| (11)     | JP5                                                   |                                                                                                       |

|          | 1-2*<br>2-4<br>2-3                                    | X1 for quadrature encoder input<br>X2 for quadrature encoder input<br>X4 for quadrature encoder input |

|          |                                                       | Must be set to X1 when in counter mode                                                                |

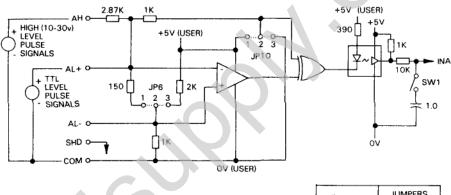

| 12(13)   | JP6 JP10                                              |                                                                                                       |

|          | 1-2* 1-2*<br>1-2 2-3                                  | Input A - 5V differential<br>Input A - TTL single ended                                               |

|          | 2-3 2-3                                               | Input A - 10-30V single ended                                                                         |

| (14)(15) | JP7 JP11                                              |                                                                                                       |

|          | 1-2* 1-2*<br>1-2 2-3                                  | Input B - 5V differential<br>Input B - TTL single ended                                               |

|          | 2-3 2-3                                               | Input B - 10-30V single ended                                                                         |

| (16)(17) | JP8 JP12                                              |                                                                                                       |

|          | 1-2* 1-2*<br>1-2 2-3                                  | Input C - 5V differential<br>Input C - TTL single ended                                               |

|          | 2-3 2-3                                               | Input C - 10-30V single ended                                                                         |

| 18(19)   | JP9 JP13                                              |                                                                                                       |

|          | $ \begin{array}{cccccccccccccccccccccccccccccccccccc$ | Input D - 5V differential<br>Input D - TTL single ended                                               |

|          | 2-3 2-3                                               | Input D - 10-30V single ended                                                                         |

\* Factory Setting

FIGURE 2. CONFIGURABLE USER SETTINGS (PART 3 OF 3)

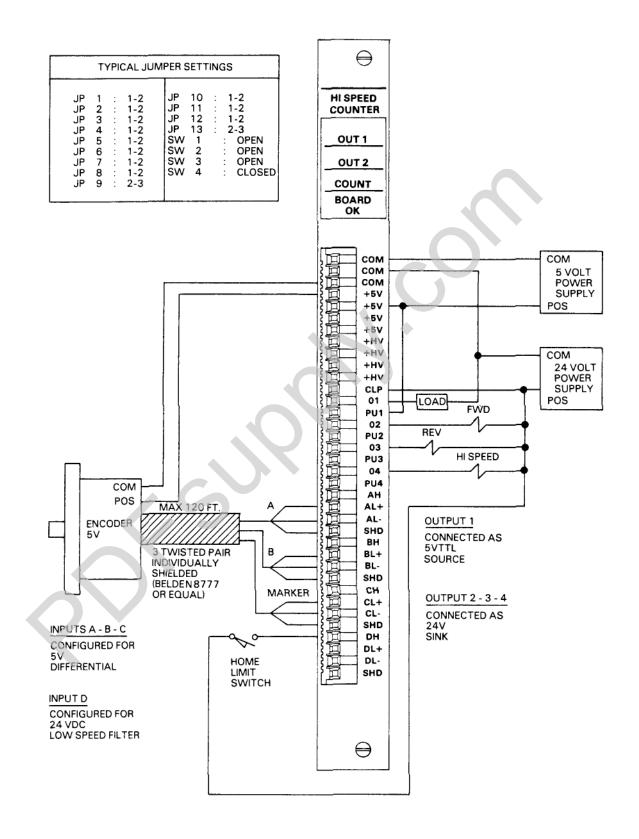

#### Figure 3. HIGH SPEED COUNTER - ENCODER MODE APPLIED TO CARRIAGE POSITION CONTROL

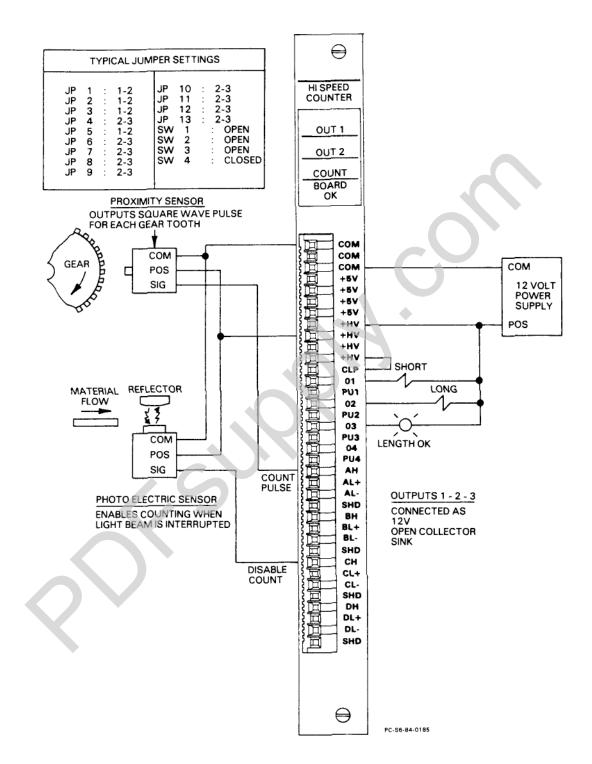

Figure 4. HIGH SPEED COUNTER - COUNTER MODE APPLIED TO LENGTH MEASUREMENT CONTROL

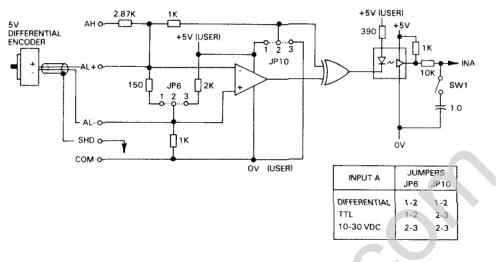

Figure 5. TYPICAL DIFFERENTIAL INPUT LOGIC DIAGRAM

| INPUT A      | JUMPERS<br>JP6 JP10 |     |  |  |  |  |  |  |

|--------------|---------------------|-----|--|--|--|--|--|--|

| DIFFERENTIAL | 1-2                 | 1-2 |  |  |  |  |  |  |

| TTL          | 1-2                 | 2-3 |  |  |  |  |  |  |

| 10-30 VDC    | 2-3                 | 2-3 |  |  |  |  |  |  |

# Figure 6. TYPICAL PULSE INPUT LOGIC DIAGRAM

Figure 7. OUTPUT LOGIC DIAGRAM

# HARDWARE INTERFACE

All external wiring connections to the High Speed counter module are made via the 36point terminal connector on the module faceplate. Table 3 details the function of each terminal point. Please note that all terminals with the same name (i.e. COM, + 5V, +HV, SHD) are internally

connected when the terminal strip is connected to the printed circuit board, If shielded cable is used, system earth ground is provided via faceplate to chassis connection and the grounding of the chassis enclosure. For typical wiring diagrams refer to Figure 3 and 4.

| TERMINAL<br>NUMBER | NAME      | FUNCTION                                                                                                                                                                                                                                                                                                                                                                       |

|--------------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1,2,3              | СОМ       | Common ground connection.                                                                                                                                                                                                                                                                                                                                                      |

| 4,5,6,7            | +5v       | User power supply positive connection for 5V operation.                                                                                                                                                                                                                                                                                                                        |

| 8, 9, 10, 11       | +HV       | User power supply positive connection for 10-30V operation.                                                                                                                                                                                                                                                                                                                    |

| 12                 | CLP       | Clamp diode connection. Protects outputs from inductive kick-back from<br>the load. The CLP terminal should be jumpered to the positive side of<br>the output power supply.                                                                                                                                                                                                    |

| 13<br>14           | 01<br>PUI | Open collector sink output. TTL compatible up to 50ma. Outputs can sink 250 ma. continuous, 500 ma. peak. The maximum supply voltage is 30V. If the PUI terminal is connected to the positive terminal of the output supply, the output will be pulled up through a 1100 ohm resistor. This output can drive the Series Six interrupt input board using a 24-30V power supply. |

| 15<br>16           | 02<br>PU2 | Open collector sink output. TTL compatible up to SOma. Outputs can sink 250 ma. continuous, 500 ma. peak. The maximum supply voltage is 30 V. If the PU2 terminal is connected to the positive terminal of the output supply, the output will be pulled up through a 4700 ohm pull-up resistor.                                                                                |

| 17<br>18           | 03<br>PU3 | Open collector sink output. TTL compatible up to 50 ma. Outputs can sink 250 ma. continuous, 500 ma. peak. The maximum supply voltage is 30V. If the PU3 terminal is connected to the positive terminal of the output supply, the output will be pulled up through a 4700 ohm pull-up resistor.                                                                                |

| 19<br>20           | 04<br>PU4 | Open collector sink output. TTL compatible up to 50 ma. Outputs can sink 250 ma, continuous, 500 ma. peak. The maximum supply voltage is 30V. If the PU4 terminal is connected to the positive terminal of the output supply, the output will be pulled up through a 4700 ohm pull-up resistor.                                                                                |

| 21<br>22           | AH<br>AL+ | These terminals form the IN A input. The settings of JP6 and JP10 determine the input type (see Figure 2).                                                                                                                                                                                                                                                                     |

| 2 3                | AL-       | In the COUNTER mode IN A is used for the incoming square wave pulses.                                                                                                                                                                                                                                                                                                          |

| 24                 | SHD       | In the ENCODER mode this input is used for quad A of the encoder.                                                                                                                                                                                                                                                                                                              |

|                    |           |                                                                                                                                                                                                                                                                                                                                                                                |

TABLE 3. TERMINAL WIRING DESCRIPTION

| TERMINAL<br>NUMBER | NAME | FUNCTION                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

|--------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 25                 | ВН   | These terminals form the IN B input. The settings of JP7 and JP1 1 deter-<br>mine the input type (see Figure 2).                                                                                                                                                                                                                                                  |  |  |  |  |  |

| 26                 | BL+  | In the COUNTER mode these terminals are used for the count direction                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

| 27                 | BL-  | control. With no signal applied the count direction is UP. If the direction                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

| 28                 | SHD  | is to be controlled via software, the input should be disabled, or not connected. Up.Down is controlled in software by bit 10 of the Discrete command (see Figure 9).                                                                                                                                                                                             |  |  |  |  |  |

|                    |      | In the ENCODER mode this input is used for quad B of the shaft encoder.                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

| 2 9                | СН   | These terminals form the IN C input. The settings of JP8 and JP12 determine the input type (see Figure 2).                                                                                                                                                                                                                                                        |  |  |  |  |  |

| 30                 | CL+  |                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| 31                 | CL-  | In the COUNTER mode these terminals are used as a counter enable<br>control. With no signal applied the counter is ENABLED. If the counter<br>enable is to be controlled by software command, IN C should be                                                                                                                                                      |  |  |  |  |  |

| 32                 | SHD  | disabled, or not connected. Enable/Disable is controlled in software by<br>Bit 9 of the Discrete Command (see Figure 9).                                                                                                                                                                                                                                          |  |  |  |  |  |

|                    |      | In the ENCODER mode this input is used for the marker pulse of the<br>shaft encoder. If there is no marker present then no connection should be<br>made to this input                                                                                                                                                                                             |  |  |  |  |  |

| 33                 | DH   | These terminals form the IN D input. The settings of JP9 and JP13 deter-<br>mine the input type (see Figure 2).                                                                                                                                                                                                                                                   |  |  |  |  |  |

| 34                 | DL+  | In the COUNTER mode the IN D input is used to reset the counter. The                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

| 3 5                | DL-  | reset function forces the accumulated count to the Lower Count Limit.<br>The reset condition will exist as long as the IN D signal is asserted. With                                                                                                                                                                                                              |  |  |  |  |  |

| 36                 | SHD  | no signal applied the counter is NOT RESET. The count can also be reset<br>by software command. IN D should be disabled or not connected if soft-<br>ware control is used. Reset is controlled in software by Bit 19 of the Dis-<br>crete Command (see Figure 9).                                                                                                 |  |  |  |  |  |

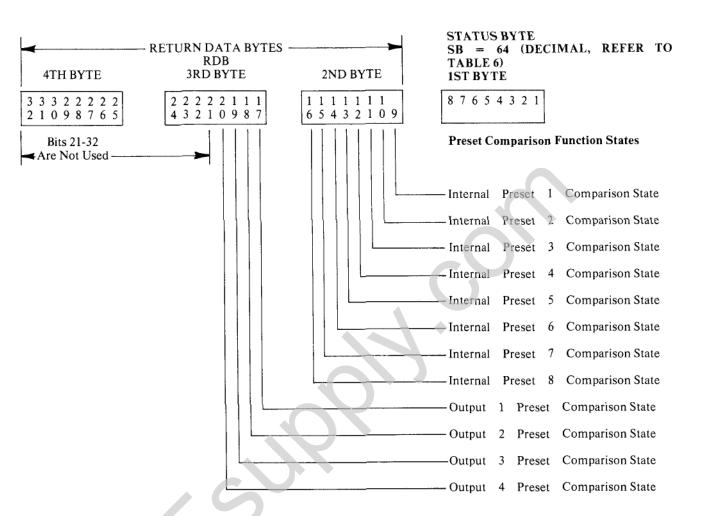

|                    |      | In the ENCODER mode the IN D input is used to establish home<br>position. When the HOME command is active and the IN D limit switch<br>is asserted, the next marker pulse will cause the accumulated count to be<br>set to the home position value. After the marker occurs, incoming pulses<br>will be counted, and will represent an offset from HOME position. |  |  |  |  |  |

TABLE 3. TERMINAL WIRING DESCRIPTION (CONTINUED)

#### GENERAL DESCRIPTION OF OPERATION

The intelligent High Speed Counter module receives cornmand data from the Series Six CPU logic program and returns count and status data to the CPU. These data transfers requires 32 input and 32 output points. There are also four input circuits and four output circuits for connection to field devices. Refer to Table 3 for a full description of each.

The High Speed Counter card has two basic modes of operation (counter or encoder) which are selectable by means of a jumper. The functions of the inputs depends on the mode of operation selected.

In the Counter mode the inputs are defined as follows:

- INA Pulse Input: connected to the pulses to be counted.

- INB Direction Input: controls the direction of counting.

- INC Enable/Disable Input: used to enable or disable counting.

- IND Reset Input: sets the Accumulate register to the Lower Count Limit and inhibits counting while active.

In the Encoder mode the inputs have the following meanings:

- INA Quad A Input: connected to channel A of the quadrature encoder.

- INB Quad B Input: connected to channel B of the quadrature encoder.

- INC Marker Input: connected to the marker channel of the encoder.

- IND Limit Switch Input: used to establish True Home Position.

Each input is provided with a selectable filtering network. When the filter is selected, the frequency response of the input is limited to 100Hz (square wave). The filter is normally used for debouncing mechanical contacts.

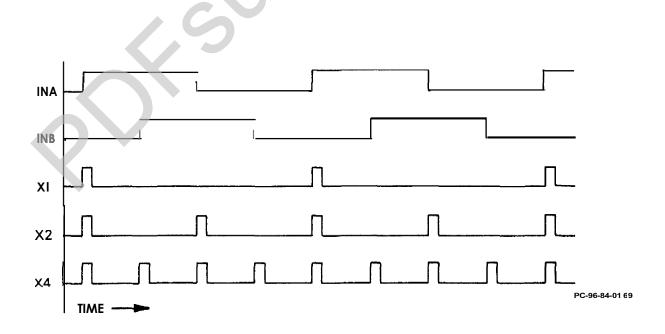

When the ENCODER mode is selected, one of three counting rates: XI, X2, or X4 can be jumper selected by the user. When the COUNTER mode is selected, the jumper must be placed in the XI position. Figure 8 shows the effect of this jumper selection for when quadrature encoders are used.

FIGURE 8. QUADRATURE PULSE COUNTING

The module contains an 8 bit counter which is read by the counter software and used to maintain a 24 bit Accumulate register. The counting range of this register is -8,388,608 to +8,388,607. Negative values are kept as 2's complement. The user can define the upper and lower counting limits anywhere within this range (the Upper Count Limit minus the Lower Count Limit must be greater than 128). When counting up, the Accumulate register will be set to the Lower Count Limit after reaching the Upper Count Limit plus one. When counting down, the Accumulate register will be set to the Upper Count Limit when reaching the Lower Count Limit minus one.

The four outputs are open collector transistors which can provide TTL compatible levels. Individual pull-up resistors are provided to allow outputs to drive TTL or CMOS logic without the use of external resistors. When used in the open collector configuration, the outputs can sink 250 ma. of current and can accept up to 30V. The output circuitry is optically isolated and detailed in Figure 7. The state of each of the four outputs is determined by a combination of five factors:

- 1. Preset/Accumulate Relationship ( < ,  $\geq$ )

- 2. Comparison Sense (Command # 35)

- 3. Disable/ Enable (Discrete Command)

- 4. Unlatch/Latch (Discrete Command)

- 5. Previous State of Output

How these factors control an output is shown in Table 4.

#### NOTE

Once an output has been turned on through the conditions described in Table 4, it can be latched on using discrete commands 15-18 (Refer to Figure 9). Once an output is latched on it will remain on regardless of changes in the Disable/Enable or Preset Comparison function. The output will not be turned off until it is unlatched, and the conditions in Table 4 are appropriate.

| Accumulate<br><, ≥<br>Preset | Comparison<br>Sense<br>(CMMD # 35) | Preset*<br>Comparison<br>Function | Disable/<br>Enable      | output<br>State  |

|------------------------------|------------------------------------|-----------------------------------|-------------------------|------------------|

| <                            | <b>0</b><br>0<br>0                 | 0<br>1<br>0<br>1                  | <b>0</b><br>0<br>1<br>1 | 0<br>0<br>0<br>1 |

| < M ∧ W                      |                                    | 1<br>0<br>1<br>0                  | 0<br>0<br>1<br>1        | 0<br>0<br>1<br>0 |

TABLE 4. OUTPUT STATE TABLE

Result of Preset Comparison is determined by the comparison sense (Command # 35), and the Preset/Accumulate relationship ( $<, \geq$ ).

When configured for open collector operation, outputs can be paralleled. In conjunction with the preset compare and enable/disable functions, custom ON/OFF switching patterns can be established. It should be noted that the counter does not monitor the state of the outputs. Therefore, if a failure in that circuitry should occur, the CPU delete "system" will not be aware of it.

In addition to the four outputs, the counter module provides eight programmable Internal Preset registers. CPU logic can download preset limits which are then compared to the accumulated count with the resultant state (true or false) returned to the CPU.

Because the counter is an intelligent module, it is capable of continued operation regardless of the operating state of the CPU. This feature is selectable via a jumper and is conditioned upon the module being previously downloaded with preset data from the CPU and the I/O rack and external power supplies being operational.

An external user-furnished power supply is required to support the delete "field" isolated Input and Output logic. The power supply may be 5 VDC or 10-30 VDC. If this, or the rack power supply should lose power, the module must be reloaded from the CPU. An appropriate status bit will be set.

#### CPU INTERFACE

Communications between the High Speed Counter module and the Central Processor Unit (CPU) is accomplished via 32 consecutive input and output bits. (I/O address selection is discussed under Installation.) Command and preset data is transferred from the CPU to the counter module, while board status, output status, accumulated count, or counts/time-base is returned from the counter to the CPU. A two way data transfer will occur with every CPU I/O scan.

Since data is only transferred between the CPU and the counter in the I/O scan, the user needs to consider carefully the use of the Suspend I/O instruction. The counter will continue operation without communication to the CPU when the I/O is suspended, but it will not be able to apprise the CPU of its status. In similar context, use of the DO I/O instruction, which could poll the counter too frequently, would tend to cause the module to respond slowly to the degree that it may miss a pulse. To prevent this, a minimum of 6 msec should elapse between I/O scans that use the I/O addresses of the counter.

# DATA SENT FROM SERIES SIX CPU

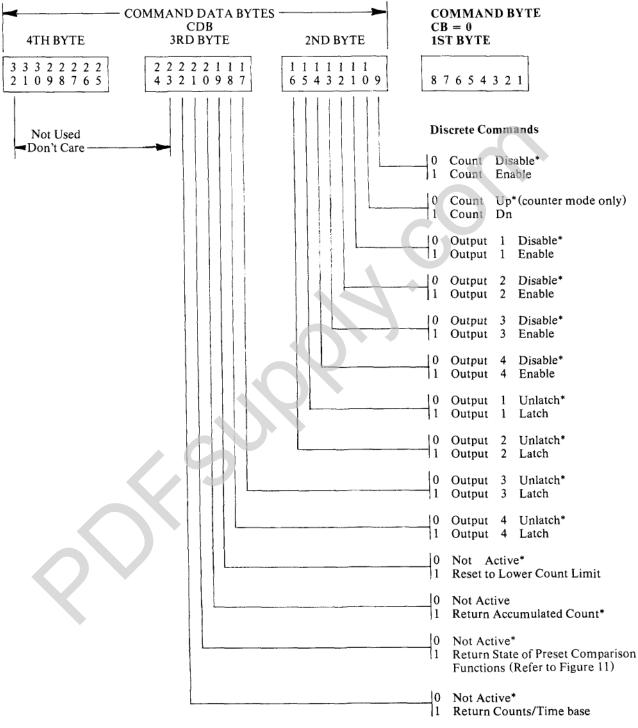

The first 8 bits or the first byte of data transferred from the CPU to the counter is referred to as the Command Byte (CB), while the remaining 24 bits or 3 bytes are referred to as the Command Data Bytes. This data uses 32 bits of the CPU output table.

|      | COMMAND DATA BYTES |        |        |        |        |        |        |           |                     |          |            |           | 1      |        | — c    | сом    | MAN<br>C | D E<br>B | ЗҮТЕ   | -      | -      |        |        |        |    |      |     |           |   |   |   |   |   |   |

|------|--------------------|--------|--------|--------|--------|--------|--------|-----------|---------------------|----------|------------|-----------|--------|--------|--------|--------|----------|----------|--------|--------|--------|--------|--------|--------|----|------|-----|-----------|---|---|---|---|---|---|

|      |                    |        | 4      | TH     | BYI    | ΤE     |        |           |                     | 3RD BYTE |            |           |        |        |        |        |          | 2ND BYTE |        |        |        |        |        |        |    |      |     | 1 ST BYTE |   |   |   |   |   |   |

|      | 3<br>2             | 3<br>1 | 3<br>0 | 2<br>9 | 2<br>8 | 2<br>7 | 2<br>6 | 2<br>5    |                     |          | 2 2        | 2 2 2 2 1 | 2<br>0 | 1<br>9 | 1<br>8 | 1<br>7 |          | 1<br>6   | 1<br>5 | 1<br>4 | 1<br>3 | 1<br>2 | 1<br>1 | 1<br>0 | 9  |      | 8   | 7         | 6 | 5 | 4 | 3 | 2 | 1 |

| terp | rete               | ed     | by     | the    | e c    | oun    | iter   | ba<br>Com | comm<br>sed<br>mand | up<br>B  | on<br>yte. | the       |        |        |        | d      | W        | EEP      | 2-     |        | -      |        |        | - sv   | VE | EP 3 |     |           | - |   |   |   |   |   |

|      |                    |        |        |        |        |        |        |           | LOC                 | SIC      |            | 1         | /0     |        | L      | .OGIC  | 2        |          |        | /0     |        |        | LO     | GIC    |    |      | I/C | )         | ] |   |   |   |   |   |

- If the CPU issues a command in Sweep 1 that requires a specific type of data to be returned, that data will be returned in Sweep 2, and be available for logic solutions in Sweep 3.

- If a command is issued that does not request return data, the previously requested data will continue to be returned.

- If a command generates an error, that Error Code will be returned in the next I/O sweep. Subsequent sweeps will return data that was previously requested.

- A CPU SUSPEND I/O function will stop all communications to the counter module while allowing it to continue in full operation.

- A CPU DO I/O function, which addresses a specific counter, can be used to download system parameters. However, communications with the counter must not occur more often than every 6 milliseconds.

# COMMAND BYTE (CB)

The Command Byte contains a Command Number that is used to set up the operational characteristics of the High Speed Counter. CPU logic selects the Command Number to be executed in the counter module and places that number in the Command Byte. One command is executed per I/O scan. Once card set up is complete, the Command Number is usually set to zero. The Command Data Bytes contain the information necessary to complete the execution of the command specified. Table 5 contains a list of all the commands along with a detailed description.

#### TABLE 5, COMMAND NUMBER

| COMMAND                | NUMBER           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|------------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DECIMAL<br>VALUE       | HEX<br>VALUE     | DEFINITION OF COMMAND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 0                      | 00               | DISCRETE COMMANDS · Interpret data bits (9-32) as discrete commands as detailed in Figure 9.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 1                      | 01               | RESET CARD · Accumulated count and preset register are set to zero; outputs<br>are turned off and board returned to initial default conditions, diagnostic tests are<br>run, if tests are passed, the heartbeat will toggle and the Power-Up Bit of the Status<br>Byte will be set; all commands except the Reset Card command will be ignored<br>until this Power-Up Bit is cleared by Command 6. If the diagnostic tests fail an<br>error code will be returned on the next I/O scan and the Board OK LED is turned<br>off.                                                                                                                                                                                                                                                                                                                                                                     |

| 2                      | 02               | CONTINUE · This is a null command and the counter will continue to operate in the previously commanded mode. When used, this command improves counter processing time.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 3                      | 03               | RETURN DISCRETE COMMAND · Return data bits (9-32) of Last Discrete Command (CB =0) sent as detailed in Figure 11.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 4                      | 04               | <b>HOME POSITION</b> · Used only in encoder mode. (Refer to Figure 13.) Data bytes will contain value of Home Position location, all outputs are disabled and unlatched, the Home Position Bit in the returned Status Byte is cleared and incoming count pulses are ignored, On first Marker Pulse (Input C) after Home Limit Switch signal (Input D) is received: Home Position value is loaded into accumulate register, incoming pulses will ADD/SUBTRACT from accumulate register to track offset from Home Position, Home Position bit (SB=5) is set, and outputs remain disabled. If, in Encoder Mode, Home Position Value is outside the Upper or Lower Count Limit, or if another command is issued while the Home Command Bit is set, an error code will be returned. This command is active until Home Position is found or Abort Home Position (CB=5) or Reset Card (CB= 1) is issued. |

| 5                      | 05               | ABORT HOME POSITION COMMAND $\cdot$ Used only in Encoder Mode; cancels Command 4; count pulses are again accepted while outputs are held disabled. Outputs must be re-enabled via the Discrete Command (CB =0). Since Home Position was not established and counting was disabled, the Accumulate Register value should be used with caution. If not in the Counter Mode or if the Home Position (Command 4) is not active, an error code will be returned.                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 6                      | 06               | CLEAR POWER-UP BIT $\cdot$ Sets Bit 2 of Status Byte to zero; this bit must equal zero for the counter module to accept any command other than Reset Card (CB= 1); bit will be set on power-up, external power supply failure, or after Reset Card command is issued.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 7<br><b>thru</b><br>15 | 07<br>thru<br>OF | Reserved for future use.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

# TABLE 5. COMMAND NUMBER (CONTINUED)

| COMMANL          |              |                                                                                                                                                                                                                                        |

|------------------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DECIMAL<br>VALUE | HEX<br>VALUE | DEFINITION OF COMMAND                                                                                                                                                                                                                  |

| 16               | 10           | LOAD OUTPUT 1 PRESET REGISTER from Command Data Bytes                                                                                                                                                                                  |

| 17               | 11           | LOAD OUTPUT 2 PRESET REGISTER from Command Data Bytes                                                                                                                                                                                  |

| 18               | 12           | LOAD OUTPUT 3 PRESET REGISTER from Command Data Bytes                                                                                                                                                                                  |

| 19               | 13           | LOAD OUTPUT 4 PRESET REGISTER from Command Data Bytes                                                                                                                                                                                  |

| 20               | 14           | LOAD INTERNAL PRESET REGISTER 1 from Command Data Bytes                                                                                                                                                                                |

| 21               | 15           | LOAD INTERNAL PRESET REGISTER 2 from Command Data Bytes                                                                                                                                                                                |

| 2 2              | 16           | LOAD INTERNAL PRESET REGISTER 3 from Command Data Bytes                                                                                                                                                                                |

| 2 3              | 17           | LOAD INTERNAL PRESET REGISTER 4 from Command Data Bytes                                                                                                                                                                                |

| 24               | 18           | LOAD INTERNAL PRESET REGISTER 5 from Command Data Bytes                                                                                                                                                                                |

| 2 5              | 19           | LOAD INTERNAL PRESET REGISTER 6 from Command Data Bytes                                                                                                                                                                                |

| 26               | 1A           | LOAD INTERNAL PRESET REGISTER 7 from Command Data Bytes                                                                                                                                                                                |

| 27               | 1B           | LOAD INTERNAL PRESET REGISTER 8 from Command Data Bytes                                                                                                                                                                                |

|                  |              | If Preset Value is above the Upper Count Limit or below the Lower Count Limit,<br>an error code will be returned and, the command will not be executed. Counter op-<br>eration remains unchanged. Default value upon power-up is zero. |

# TABLE 5.COMMANDNUMBERS (CONTINUED)

| COMMANC            |                  |                                                                                                                                                                                                                                                                                                                                          |

|--------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DECIMAL<br>VALUE   | HEX<br>VALUE     | DEFINITION OF COMMAND                                                                                                                                                                                                                                                                                                                    |

| 2 8<br>thru<br>3 1 | 1C<br>thru<br>1F | Reserved for future use.                                                                                                                                                                                                                                                                                                                 |

| 32                 | 20               | LOAD ACCUMULATE REGISTER from Command Data Bytes-If new Accu-<br>mulate Value is above the Upper Count Limit or below the Lower Count Limit, an<br>error code will be returned and, the command will not be executed. Counter oper-<br>ation remains unchanged, Default value upon power-up is zero.                                     |

| 3 3                | 21               | LOAD UPPER COUNT LIMIT from Command Data Bytes-If Upper Count<br>Limit minus the Lower Count Limit is less than 128, an error code will be returned<br>and, the command will not be executed. Counter operation remains unchanged.<br>Default value upon power-up is 8,388,607 or 7FFFF(HEX).                                            |

| 34                 | 22               | LOAD LOWER COUNT LIMIT from Command Data Bytes-If Upper Count<br>Limit minus the Lower Count Limit is less than 128, an error code will be returned<br>and, the command will not be executed. Counter operation remains unchanged.<br>Default value upon power-up is zero. Lower count limit is -8,388,608 or 800000<br>(HEX).           |

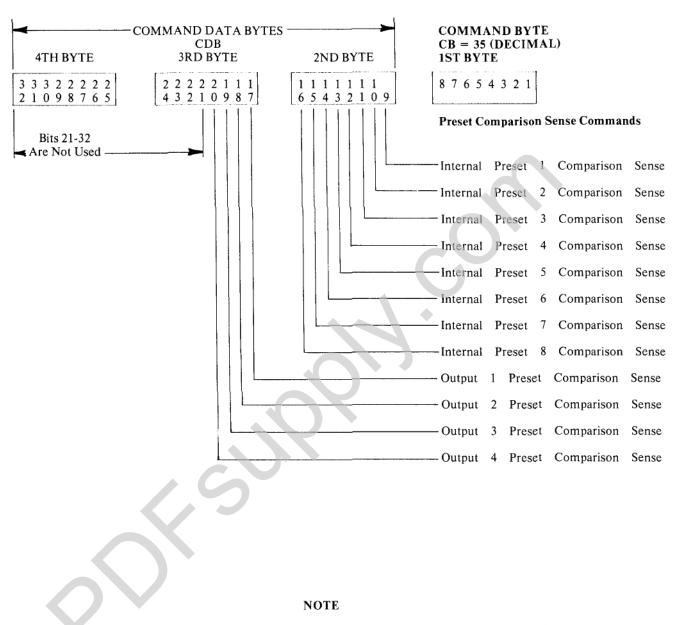

| 35                 | 23               | LOAD PRESET COMPARISON SENSE · Interpret Command Data Bytes (bits 9-32) as detailed in Figure 10.                                                                                                                                                                                                                                        |

| 36                 | 24               | LOAD TIME BASE from Command Data Bytes-Sets time base in milliseconds<br>for measurement of count pulses/ time base for use in velocity feedback. If time<br>base is set outside of range 1 to 65,535 (milliseconds), an error code will be re-<br>turned and, the command will not be executed. Counter operation remains<br>unchanged. |

| 37<br>thru<br>47   | 25<br>thru<br>2F | Reserved for future use.                                                                                                                                                                                                                                                                                                                 |

| 2                  |                  |                                                                                                                                                                                                                                                                                                                                          |

| COMMANL :<br>DECIMAL<br>VALUE | NUMBER<br>HEX<br>VALUE | DEFINITION OF COMMAND                                                  |

|-------------------------------|------------------------|------------------------------------------------------------------------|

| VALUE                         | VALUE                  |                                                                        |

| 48                            | 30                     | RETURN OUTPUT 1 PRESET REGISTER                                        |

| 49                            | 31                     | RETURN OUTPUT 2 PRESET REGISTER                                        |

| 50                            | 32                     | RETURN OUTPUT 3 PRESET REGISTER                                        |

| 51                            | 33                     | RETURN OUTPUT 4 PRESET REGISTER                                        |

| 52                            | 34                     | RETURN INTERNAL PRESET REGISTER 1                                      |

| 53                            | 35                     | RETURN INTERNAL PRESET REGISTER 2                                      |

| 54<br>55                      | 3 0 3 7                | RETURN INTERNAL PRESET REGISTER 3<br>RETURN INTERNAL PRESET REGISTER 4 |

| 56                            | 38                     | RETURN INTERNAL PRESET REGISTER 5                                      |

| 57                            | 39                     | RETURN INTERNAL PRESET REGISTER 6                                      |

| 58                            | 3 A                    | RETURN INTERNAL PRESET REGISTER 7                                      |

| 59                            | 3 B                    | RETURN INTERNAL PRESET REGISTER 8                                      |

| 60<br>thru<br>63              | 3c<br>thru<br>3F       | Reserved for Future Use                                                |

| 64                            | 40                     | RETURN ACCUMULATE REGISTER (CB = $32$ )                                |

| 6 5                           | 4 1                    | RETURN UPPER COUNT LIMIT (CB=33)                                       |

| 66                            | 42                     | RETURN LOWER COUNT LIMIT (CB=34)                                       |

| 67                            | 43                     | RETURN PRESET COMPARISON SENSE (CB=35)                                 |

| 68                            | 44                     | RETURN TIME BASE (CB=36)                                               |

| 69<br>thru<br>255             | 45<br>thru<br>7F       | Reserved for future use                                                |

# TABLE 5. COMMAND NUMBERS (CONTINUED)

\* Default conditions on power-up

#### NOTE

The High Speed Counter will interrupt and act upon each bit every time this data set is received from the CPU. The module will execute, for function bits 20, 21, 22 only, the lowest bit number function if more than one bit is set.

> Figure 9. DISCRETE COMMAND FORMAT COMMAND BYTE EQUALS ZERO (CB=0)

GEK-83545

The Load Preset Comparison Sense command (CB = 35) establishes the True. False (1/0) comparison sense between the accumulate and the twelve presents in the counter module. Output # 9 through # 20 set the sense for the eight internal and four output presets. If the output is off (0), the respective preset comparison function will be true (1) when the accumulated count is greater than or equal ( $\geq$ ) to the preset. If the output is on (1), the preset comparison function will be true when the accumulated count is less than (<) the preset. The following chart illustrates this concept.

Figure 10. PRESET COMPARISON SENSE

| ACCUMULATED COUNT<br><, ≥<br>PRESET | COMPARISON<br>SENSE | PRESET<br>COMPARISON<br>FUNCTION |

|-------------------------------------|---------------------|----------------------------------|

| <                                   | OFF (0)             | FALSE (0)                        |

| $\geq$                              | OFF (0)             | TRUE (1)                         |

| <                                   | ON (1)              | TRUE (1)                         |

| 3                                   | ON (1)              | FALSE (0)                        |

#### NOTE (Continued)

In the case of outputs, the output will be turned on when the Preset Comparison function is true if it has been enabled (Refer to Table 4, and Figure 9). When the Preset Comparison function is no longer true, the output will be turned off, unless it has been latched (Refer to Figure 9).

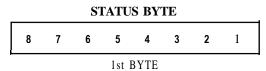

The state of all Preset Comparison functions (FALSE = 0, TRUE = 1), can be returned to CPU User Logic by giving the module discrete command # 21, return state of Preset Comparison functions (Refer to Figures 9, and 11).

Figure 10. PRESET COMPARISON SENSE (Continued)

#### DATA RETURNED TO SERIES SIX CPU

The first 8 bits, or the first byte of data, transferred to the CPU from the counter is referred to as the Status Byte, while the remaining 24 bits or 3 bytes are referred to as

the Returned Data Bytes. This data uses 32 bits of the CPU Input Table.

|                                      | RDB                                                   |                                                       | SB              |

|--------------------------------------|-------------------------------------------------------|-------------------------------------------------------|-----------------|

| 4TH BYTE                             | 3RD BYTE                                              | 2ND BYTE                                              | ISIBYIE         |

| 3 3 3 2 2 2 2 2 2<br>2 1 0 9 8 7 6 5 | $ \begin{array}{cccccccccccccccccccccccccccccccccccc$ | $ \begin{array}{cccccccccccccccccccccccccccccccccccc$ | 8 7 6 5 4 3 2 1 |

Information contained in the Returned Data Bytes is that data which was requested via the Command Number contained in the Command Byte issued during the previous I/O scan. The previously requested data type will be returned every I/O scan unless a new type of return data is requested. Default returned data on power-up is the accumulated count value.

The Status Byte (SB) contains information pertaining to the current operating status of the High Speed Counter. This byte is updated and returned to the CPU every I/O scan. Definition of the Status Byte bits is as follows.

Bit 1 - HEARTBEAT: This bit indicates if the board is functional. It is toggled every time an I/O scan occurs except during power-up diagnostics, Any failures of counter diagnostics will stop the heartbeat.

Bit 2 · POWER-UP: This bit is set by the module to a one (1) whenever rack or external power is applied, either for the first time or following a power dip. On power-up, the counter will run its diagnostic tests and reset all internal data registers to their default values.

A Reset Card Command (CB = 1) from the CPU will also cause diagnostics to be executed and the Power-Up bit to be set.

All commands (except Reset Card) will be ignored until this bit is reset to zero (0) by the Clear Power-up Bit Command (CB - 6).

Bit 3 · EXTERNAL POWER SUPPLY STATUS: This bit is set to a one (1) whenever the external (user) power supply is below 4.5V. When external power fails, the Power-Up bit is set and the counter will run its diagnostic tests and reset all data registers to their default values. All commands (except Reset Card) will be ignored until the Power-Up bit is reset to a zero (0) by the Clear Power-up Bit Command (CB = 6).

Bit 4  $\cdot$  COUNTING ENABLED: This bit, when set to a one (1) by the counter module, indicates that the counter is enabled. The Count Enable command (CB=0, bit 9) must be set to one (1) to enable counting. To Disable counting, set bit 9 to zero (0), or in the Count Mode, apply a signal to Input C.

Bit 5 HOME/DIRECTION: In the Encoder Mode this bit indicates that Home Position has been established, and is set to a one (1) when any of the following events occur:

- a. After the Home Command (CB=4) is issued, and the first Marker Pulse is received after the Home Limit Switch is reached. Refer to Figure 14.

- b. A load Accumulate command (CB=32) is issued.

- c. A Reset Accumulate to Lower Count Limit (CB=O, bit 19) is issued.

This bit is reset to zero (0) on Power-up, Reset Command (CB-O), or Home Command (CB=4).

In the Counter Mode this bit indicates the direction of count (0 = up, (1 = down). Direction is a function of Input B or the Up/Down Count command (CB=0, bit 10). Count direction is Up unless a signal is applied to Input B or CB=0, bit 10 is set to a one (1).

Bits 6, 7, 8  $\cdot$  Returned Data Type: Interpretation of these bits indicates the type of data being returned to the CPU in the Return Data Bytes 2, 3, and 4. If an error code is returned, the command that caused the error is ignored, and count operation remains unchanged. (Refer to Table 6)

| Bit 8 | Bit 7 | Bit 6 | Data Returned                                                                |

|-------|-------|-------|------------------------------------------------------------------------------|

| 0     | 0     | 0     | Accumulated Count (default on power-up)                                      |

| 0     | 0     | 1     | Counts/Time base                                                             |

| 0     | 1     | 0     | Comparison States for Presets (see Figure 12)                                |

| 0     | 1     | 1     | Returned Data as requested in previous I/O scan from commands 3,48-59, 65-68 |

| 1     | 0     | 0     | Error Code (see Figure 13)                                                   |

| 1     | 0     | 1     | Future Use                                                                   |

| 1     | 1     | 0     | Future Use                                                                   |

| 1     | 1     | 1     | Future Use                                                                   |

# TABLE 6. RETURNED DATA TYPE

#### NOTE

This discrete data is returned to the CPU Input Table two sweeps after discrete command # 21 has been issued (Refer to Figure 9). Inputs 9 through 20 reflect the state of all Preset Comparison functions (Refer to Figure 10). If the Input is on (1), the Preset Comparison function is True. Conversely, if the Input is off (0), the Preset Comparison Function is False.

The state (ON/OFF) of each of the four outputs does not necessarily match the state of the Preset Comparison function. The Enable/Disable Latch/Unlatch, along with the Preset Comparison Function determine the ON/OFF status of each output (Refer to Table 4, and Figure 9).

Figure 11. COMPARISON STATES FOR PRESETS

# ERROR CODES

|        |        |        |             |        |        |        |        | <br>   | RET    | URI    | N DA<br>RE |        | BY     | TES    |        |        |        | EF | ROF    |        | ODE    |        | - | 4 |   | STA | ATU<br>S |     | ΥTE |   | - |

|--------|--------|--------|-------------|--------|--------|--------|--------|--------|--------|--------|------------|--------|--------|--------|--------|--------|--------|----|--------|--------|--------|--------|---|---|---|-----|----------|-----|-----|---|---|

|        |        | 4      | <b>1</b> ТН | ΒY     | ΤE     |        |        |        |        | 3      | RD         | вүт    | E      |        |        |        |        | :  | 2ND    | BYI    | E      |        |   |   |   | 1   | STI      | вүт | E   |   |   |

| 3<br>2 | 3<br>1 | 3<br>0 | 2<br>9      | 2<br>8 | 2<br>7 | 2<br>6 | 2<br>5 | 2<br>4 | 2<br>3 | 2<br>2 | 2<br>1     | 2<br>0 | 1<br>9 | 1<br>8 | 1<br>7 | 1<br>6 | 1<br>5 | 1  | 1<br>3 | 1<br>2 | 1<br>1 | 1<br>0 | 9 | 8 | 7 | 6   | 5        | 4   | 3   | 2 | 1 |

When the Status Byte bits 6, 7, 8 indicate an error code is present (refer to Table 6), a binary number will be returned in the 2nd Byte indicating the particular Error Code. If a command generates an error, that command will be ignored and an Error Code will be present in the Return Data Bytes of the next I/O scan. Subsequent sweeps will return the previously requested data. Counter operation remains unchanged from its current operating mode whenever an error code is sensed. The data contained in the 3rd and 4th bytes is indeterminate. The Error Codes are as follows.

HIGH SPEED COUNTER ERROR CODES

| DECIMAL<br>VALUE | HEX<br>VALUE                        | DESCRIPTION OF ERROR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|------------------|-------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VALUE            | I<br>2<br>3<br>4<br>5<br>6<br>I - A | <ul> <li>Invalid Home Position value - The valid Home Position value should be: LCL &lt; = Home Position &lt; = UCL</li> <li>LCL - Lower Count Limit UCL = Upper Count Limit</li> <li>The command was not executed.</li> <li>Invalid Home Command - While in Home Position mode no commands are accepted. This error code will be generated if another Home command is issued before Home position is achieved.</li> <li>Invalid Home Command - Home command was issued while in counter mode.</li> <li>Invalid Abort Home Command - Abort Home command was not executed because card is not in Home Position Mode, or Home position has already been established.</li> <li>Invalid Abort Home Command - Abort Home command was issued while in counter mode.</li> <li>Invalid Abort Home Command - Abort Home command was issued while in counter mode.</li> <li>Invalid Abort Home Command - Abort Home command was issued while in counter mode.</li> </ul> |

|                  |                                     | LCL < - Output (l-4) Preset < = UCL<br>The command was not executed.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

FIGURE 12. ERROR CODES

| DECIMAL<br>VALUE | HEX<br>VALUE | DESCRIPTION OF ERROR                                                                                                                                                                                                                                                               |

|------------------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11-18            | B-12         | Invalid Internal Preset (I-8) Value - Internal Preset Value must lie between lower count limit and upper count limit,                                                                                                                                                              |

|                  |              | $LCL \leq Internal Preset \leq UCL$                                                                                                                                                                                                                                                |

|                  |              | The command was not executed.                                                                                                                                                                                                                                                      |

| 19               | 13           | Invalid Accumulate Value - Valid Accumulate values are:                                                                                                                                                                                                                            |

|                  |              | LCL < = Accumulate < - UCL                                                                                                                                                                                                                                                         |

|                  |              | The command was not executed.                                                                                                                                                                                                                                                      |

| 20               | 14           | Invalid Upper Count Limit · Upper Count Limit minus Lower Count Limit should be greater than or equal to 128. The command was not executed.                                                                                                                                        |

| 2 1              | 15           | Invalid Lower Count Limit - Upper Count Limit minus Lower Count Limit should be greater than or equal to 127. The command was not executed.                                                                                                                                        |

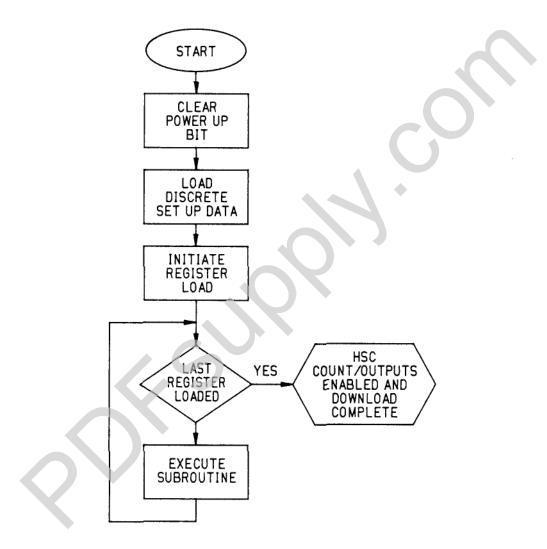

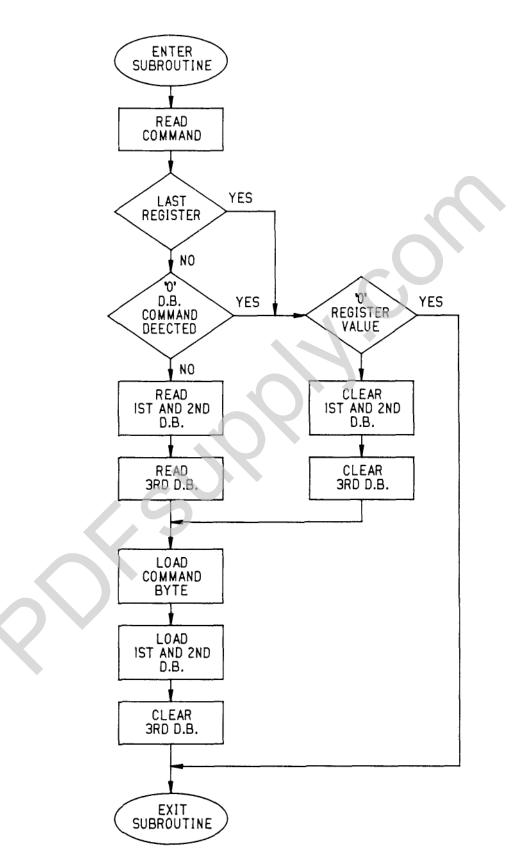

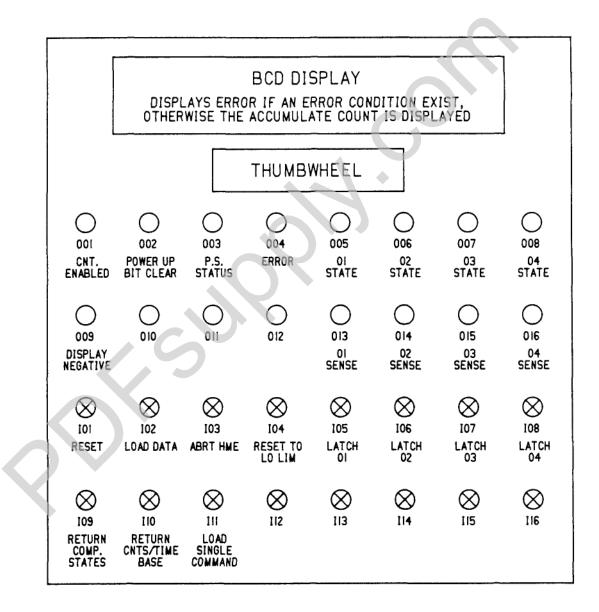

| 2 2              | 16           | Invalid Time Base Value · Valid Time Base values are:<br>1 < = Time Base $< = 65535$                                                                                                                                                                                               |