# **GFK-2222**

# New In Stock! GE Fanuc Manuals

http://www.pdfsupply.com/automation/ge-fanuc-manuals/rx7i-plc/GFK-2222

rx7i-plc 1-919-535-3180

PACSystems CPU Reference Manual, GFK-2222

www.pdfsupply.com

Email: sales@pdfsupply.com

# GFK-2222 New In Stock! GE Fanuc Manuals

http://www.pdfsupply.com/automation/ge-fanuc-manuals/rx7i-plc/GFK-2222

rx7i-plc 1-919-535-3180

PACSystems CPU Reference Manual, GFK-2222

www.pdfsupply.com

Email: sales@pdfsupply.com

# GE Fanuc Intelligent Platforms **Programmable Control Products**

# PACSystems™

CPU Reference Manual, GFK-2222M

March 2009

# Warnings, Cautions, and Notes as Used in this Publication

# Warning

Warning notices are used in this publication to emphasize that hazardous voltages, currents, temperatures, or other conditions that could cause personal injury exist in this equipment or may be associated with its use.

In situations where inattention could cause either personal injury or damage to equipment, a Warning notice is used.

Caution

Caution notices are used where equipment might be damaged if care is not taken.

**Note:** Notes merely call attention to information that is especially significant to understanding and operating the equipment.

This document is based on information available at the time of its publication. While efforts have been made to be accurate, the information contained herein does not purport to cover all details or variations in hardware or software, nor to provide for every possible contingency in connection with installation, operation, or maintenance. Features may be described herein which are not present in all hardware and software systems. GE Fanuc assumes no obligation of notice to holders of this document with respect to changes subsequently made.

GE Fanuc makes no representation or warranty, expressed, implied, or statutory with respect to, and assumes no responsibility for the accuracy, completeness, sufficiency, or usefulness of the information contained herein. No warranties of merchantability or fitness for purpose shall apply.

The following are trademarks of GE Fanuc Intelligent Platforms:

| Alarm Master      | Helpmate    | ProLoop     | Series Six   |

|-------------------|-------------|-------------|--------------|

| CIMPLICITY        | Logicmaster | PROMACRO    | Series Three |

| CIMPLICITY 90-ADS | Modelmaster | PowerMotion | VersaMax     |

| CIMSTAR           | Motion Mate | PowerTRAC   | VersaPoint   |

| Field Control     | PACMotion   | Series 90   | VersaPro     |

| GEnet             | PACSystems  | Series Five | VuMaster     |

| Genius            | Proficy     | Series One  | Workmaster   |

©Copyright 2003—2009 GE Fanuc Intelligent Platforms North America, Inc.

All Rights Reserved

| Introduction                                   | 1-1  |

|------------------------------------------------|------|

| New Features                                   | 1-2  |

| PACSystems Control System Overview             | 1-3  |

| Programming and Configuration                  |      |

| Process Systems                                | 1-3  |

| PACSystems CPU Models                          | 1-4  |

| RX3i Overview                                  | 1-5  |

| RX7i Overview                                  | 1-6  |

| Migrating Series 90 Applications to PACSystems | 1-7  |

| PACSystems Documentation                       | 1-8  |

| Technical Support                              | 1-9  |

| General Contact Information                    | 1-9  |

| Technical Support                              | 1-9  |

| Americas                                       | 1-9  |

| Europe, the Middle East, and Africa            | 1-9  |

| Asia Pacific                                   | 1-9  |

| CPU Features and Specifications                | 2-1  |

| Common CPU Features                            | 2-1  |

| Firmware Storage in Flash Memory               | 2-1  |

| Operation, Protection, and Module Status       | 2-1  |

| Ethernet Global Data                           | 2-1  |

| RX7i Features and Specifications               | 2-2  |

| CPE010, CPE020 and CRE020 Models               | 2-2  |

| CPE030/CRE030 and CPE040/CRE040 Models         | 2-5  |

| Embedded Ethernet Interface                    | 2-8  |

| RX3i Features and Specifications               | 2-12 |

| IC695CPU310                                    | 2-12 |

| IC695CPU320/CRU320 Models                      | 2-14 |

| CPU Configuration                              | 3-1  |

| Configuring the CPU                            | 3-1  |

| Configuration Parameters                       | 3-2  |

| Settings Parameters                            | 3-2  |

| Modbus TCP Address Map                         | 3-3  |

| Scan Parameters                                | 3-4  |

| Memory Parameters                              | 3-6  |

| Fault Parameters                               |      |

| Redundancy Parameters (Redundancy CPUs Only)   | 3-10 |

| Transfer List                                  |      |

| Port 1 and Port 2 Parameters                   |      |

| Scan Sets Parameters                           |      |

| Power Consumption Parameters                   | 3-15 |

| Setting a Temporary IP Address                                | 3-16 |

|---------------------------------------------------------------|------|

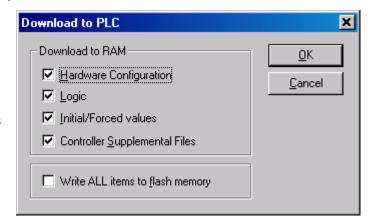

| Storing (Downloading) Hardware Configuration                  | 3-17 |

| Configuring the RX7i Embedded Ethernet Interface              | 3-18 |

| CPU Operation                                                 | 4-1  |

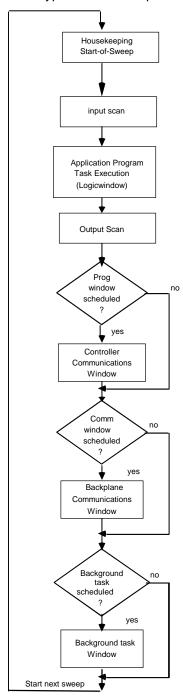

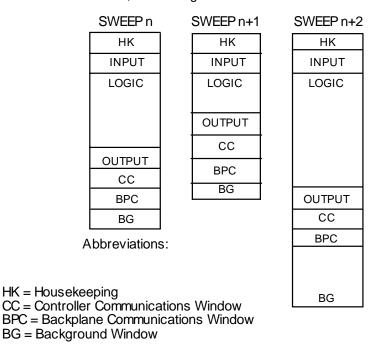

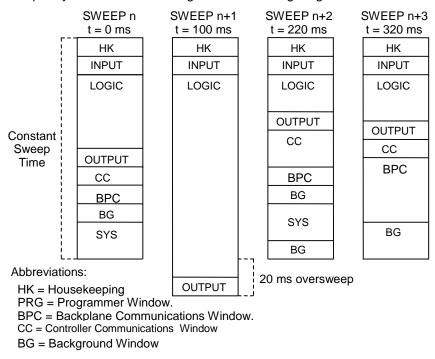

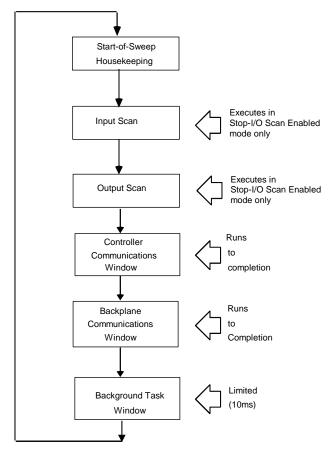

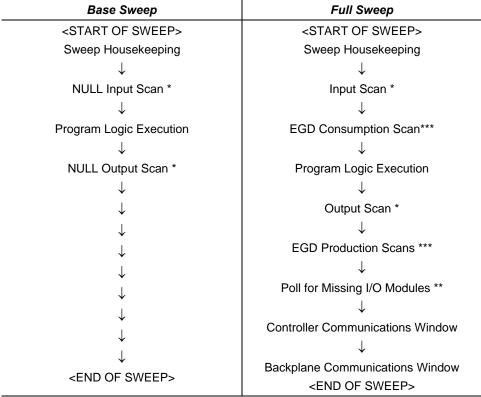

| CPU Sweep                                                     | 4-2  |

| Parts of the CPU Sweep                                        | 4-3  |

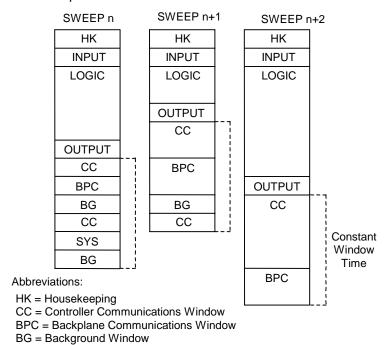

| CPU Sweep Modes                                               | 4-6  |

| Program Scheduling Modes                                      | 4-9  |

| Window Modes                                                  | 4-9  |

| Data Coherency in Communications Windows                      | 4-9  |

| Run/Stop Operations                                           | 4-10 |

| CPU Stop Modes                                                |      |

| Stop-to-Run Mode Transition                                   |      |

| Run/Stop Mode Switch Operation                                | 4-12 |

| Flash Memory Operation                                        | 4-13 |

| Logic/Configuration Source and CPU Operating Mode at Power-up | 4-14 |

| Clocks and Timers                                             | 4-16 |

| Elapsed Time Clock                                            | 4-16 |

| Time-of-Day Clock                                             | 4-16 |

| Watchdog Timer                                                | 4-18 |

| System Security                                               | 4-19 |

| Passwords and Privilege Levels                                | 4-19 |

| OEM Protection                                                | 4-20 |

| PACSystems I/O System                                         | 4-21 |

| I/O Configuration                                             |      |

| Genius I/O                                                    |      |

| Genius Global Data Communications                             |      |

| I/O System Diagnostic Data Collection                         |      |

| Power-Up and Power-Down Sequences                             |      |

| Power-Up Sequence                                             |      |

| Power-Down Sequence                                           |      |

| Retention of Data Memory Across Power Failure                 | 4-28 |

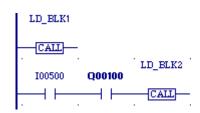

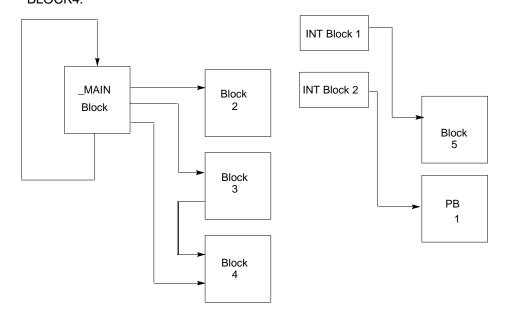

| Program Organization                                          | 5-1  |

| Structure of a PACSystems Application Program                 | 5-1  |

| Blocks                                                        | 5-1  |

| Functions and Function Blocks                                 |      |

| How Blocks Are Called                                         |      |

| Nested Calls                                                  |      |

| Types of Blocks                                               |      |

| Local Data                                                    |      |

| Parameter Passing Mechanisms                                  |      |

| Languages                                                     | 5-14 |

| Controlling Program Execution                | 5-16 |

|----------------------------------------------|------|

| Interrupt-Driven Blocks                      | 5-17 |

| Interrupt Handling                           | 5-17 |

| Timed Interrupts                             | 5-18 |

| I/O Interrupts                               | 5-19 |

| Module Interrupts                            | 5-19 |

| Interrupt Block Scheduling                   | 5-19 |

| Program Data                                 | 6-1  |

| Variables                                    | 6-2  |

| Mapped Variables                             | 6-2  |

| Symbolic Variables                           | 6-2  |

| I/O Variables                                | 6-3  |

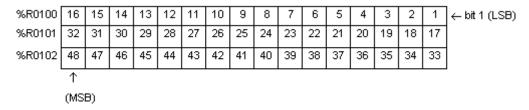

| Reference Memory                             | 6-6  |

| Word (Register) References                   | 6-6  |

| Bit (Discrete) References                    | 6-8  |

| User Reference Size and Default              | 6-9  |

| %G User References and CPU Memory Locations  | 6-9  |

| Genius Global Data                           | 6-10 |

| Transitions and Overrides                    | 6-11 |

| Retentiveness of Logic and Data              | 6-12 |

| Data Scope                                   |      |

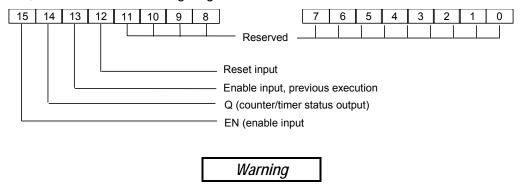

| System Status References                     |      |

| %S References                                |      |

| %SA, %SB, and %SC References                 |      |

| Fault References                             |      |

| How Program Functions Handle Numerical Data  |      |

| Data Types                                   |      |

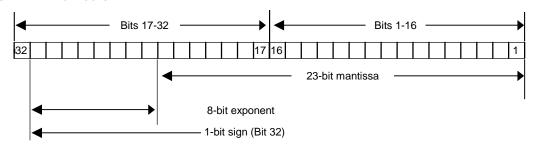

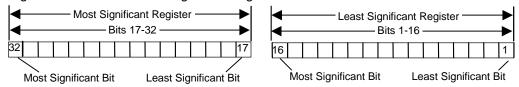

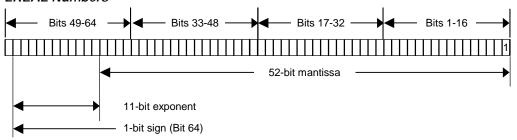

| Floating Point Numbers                       |      |

| Word-for-Word Changes                        |      |

| Operands for Instructions                    |      |

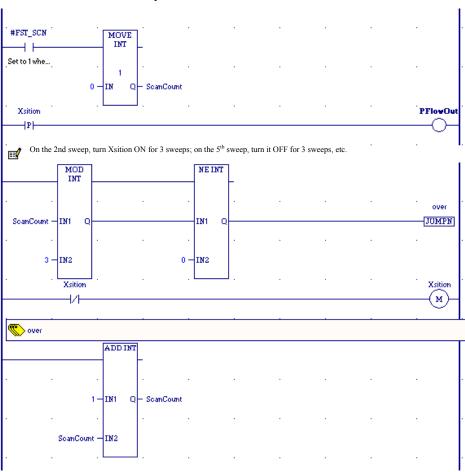

| Ladder Diagram Programming                   | 7-1  |

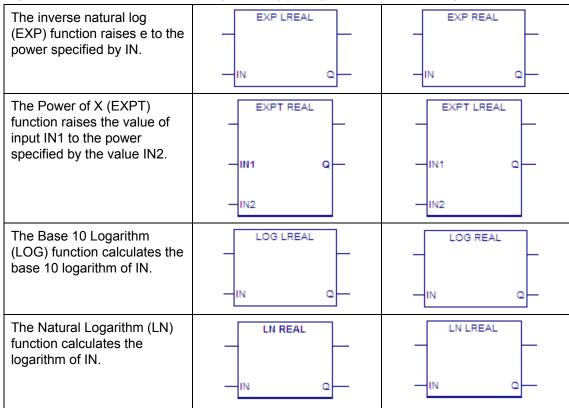

| Advanced Math Functions                      |      |

| Exponential/Logarithmic Functions            |      |

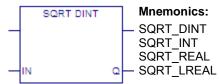

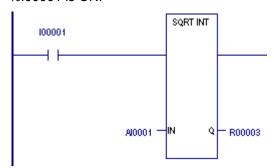

| Square Root                                  |      |

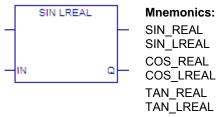

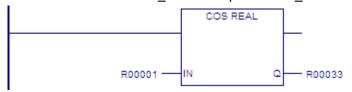

| Trig Functions                               |      |

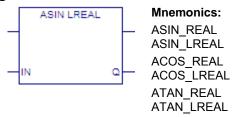

| Inverse Trig – ASIN, ACOS, and ATAN          |      |

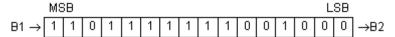

| Bit Operation Functions                      |      |

| Data Lengths for the Bit Operation Functions |      |

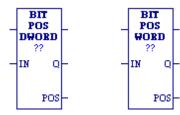

| Bit Position                                 |      |

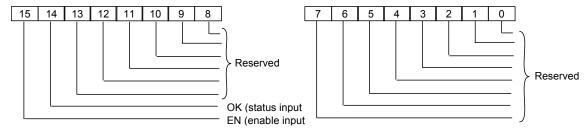

| Bit Sequencer                                |      |

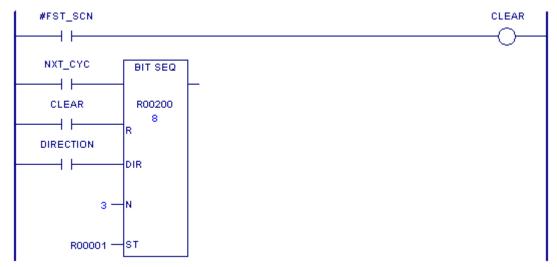

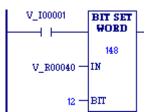

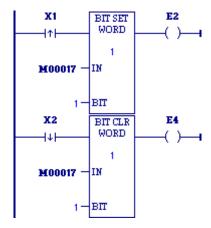

| Bit Set, Clear                               |      |

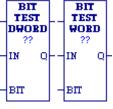

| Bit Test                                     |      |

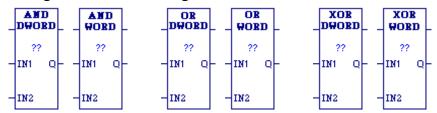

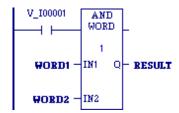

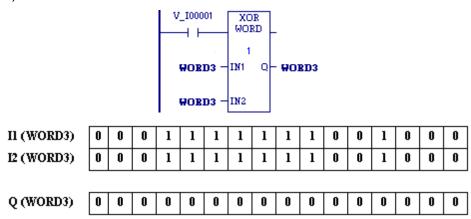

| Logical AND, Logical OR, and Logical XOR     |      |

|                                              |      |

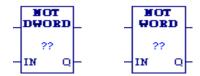

| Logical NOT                                         | 7-18 |

|-----------------------------------------------------|------|

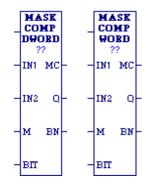

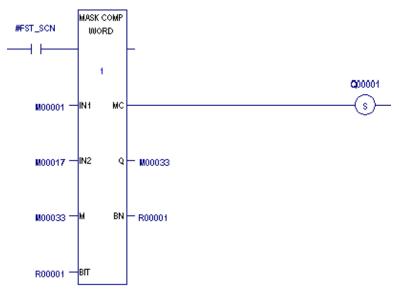

| Masked Compare                                      | 7-19 |

| Rotate Bits                                         | 7-22 |

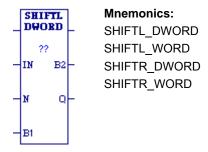

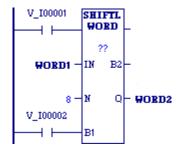

| Shift Bits                                          | 7-23 |

| Coils                                               | 7-25 |

| Coil Checking                                       | 7-25 |

| Graphical Representation of Coils                   | 7-25 |

| Set, Reset Coil                                     | 7-26 |

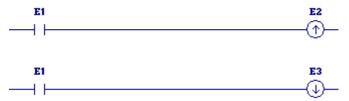

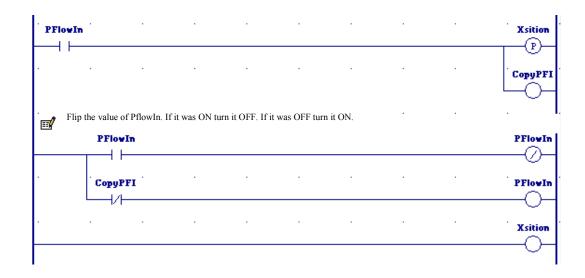

| Transition Coils                                    | 7-28 |

| Contacts                                            | 7-31 |

| Continuation Contact                                | 7-32 |

| Fault Contact                                       |      |

| High and Low Alarm Contacts                         | 7-33 |

| No Fault Contact                                    | 7-33 |

| Normally Closed and Normally Open Contacts          | 7-34 |

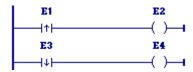

| Transition Contacts                                 | 7-35 |

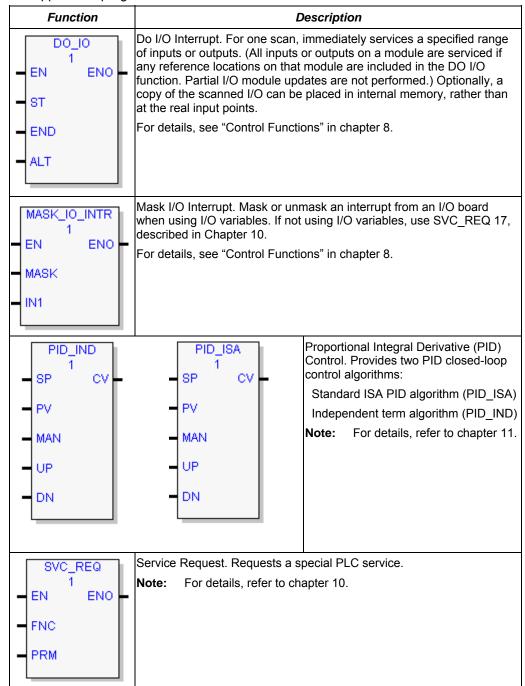

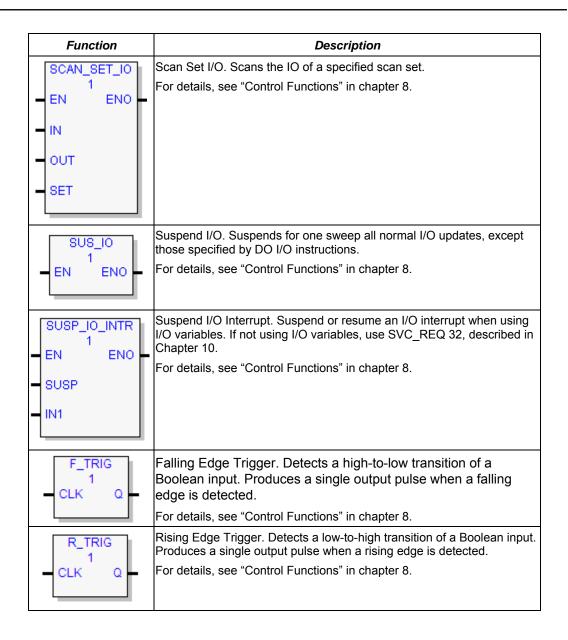

| Control Functions                                   | 7-39 |

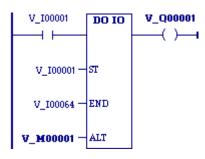

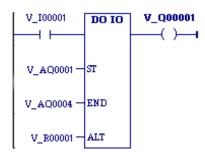

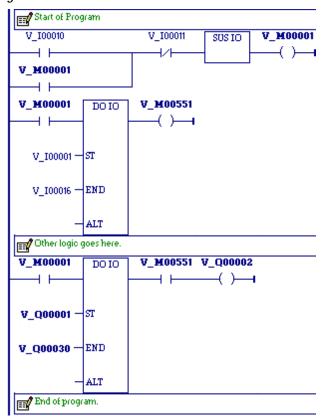

| Do I/O                                              | 7-40 |

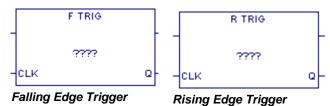

| Edge Detectors                                      | 7-43 |

| Drum                                                |      |

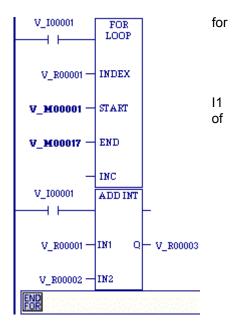

| For Loop                                            | 7-48 |

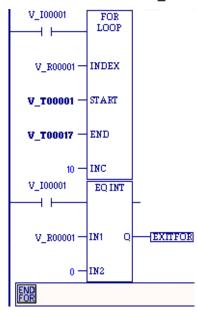

| Mask I/O Interrupt                                  | 7-51 |

| Read Switch Position                                | 7-52 |

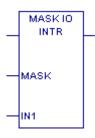

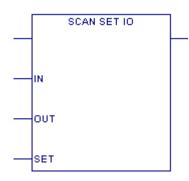

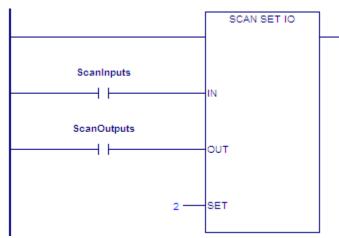

| Scan Set IO                                         | 7-53 |

| Suspend I/O                                         |      |

| Suspend or Resume I/O Interrupt                     | 7-57 |

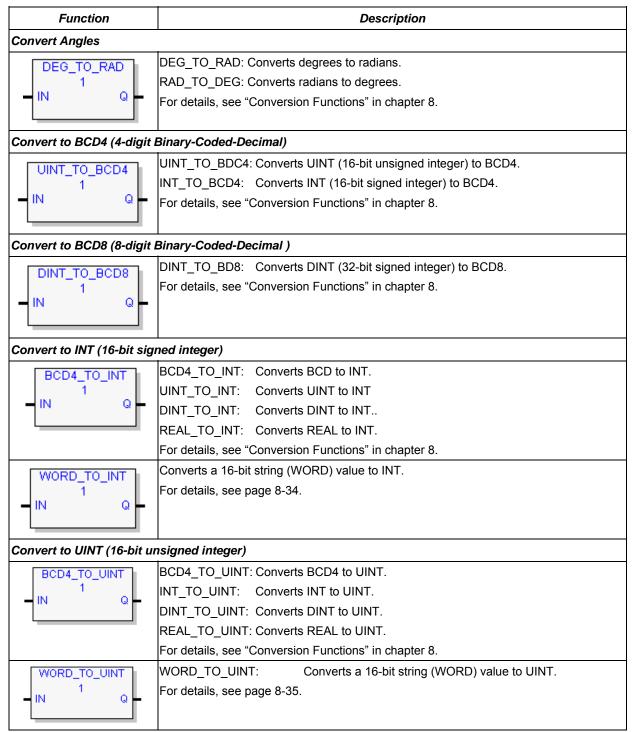

| Conversion Functions                                |      |

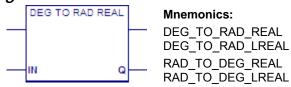

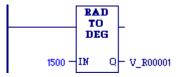

| Convert Angles                                      | 7-59 |

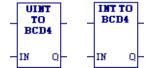

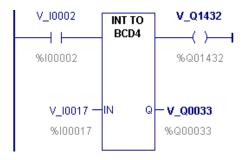

| Convert UINT or INT to BCD4                         |      |

| Convert DINT to BCD8                                |      |

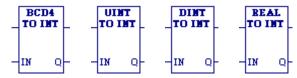

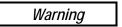

| Convert BCD4, UINT, DINT, or REAL to INT            |      |

| Convert BCD4, INT, DINT, or REAL to UINT            |      |

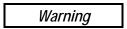

| Convert BCD8, UINT, INT, REAL or LREAL to DINT      |      |

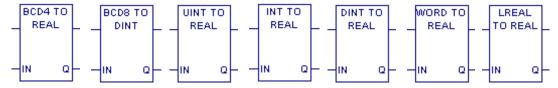

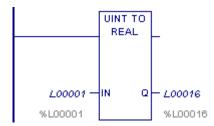

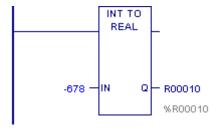

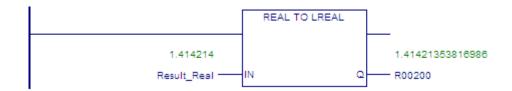

| Convert BCD4, BCD8, UINT, INT, DINT, and LREAL to F |      |

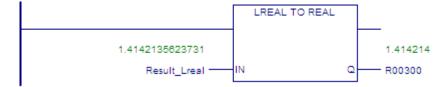

| Convert REAL to LREAL                               |      |

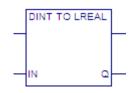

| Convert DINT to LREAL                               |      |

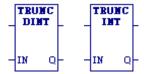

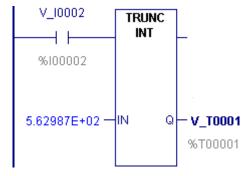

| Truncate                                            | 7-70 |

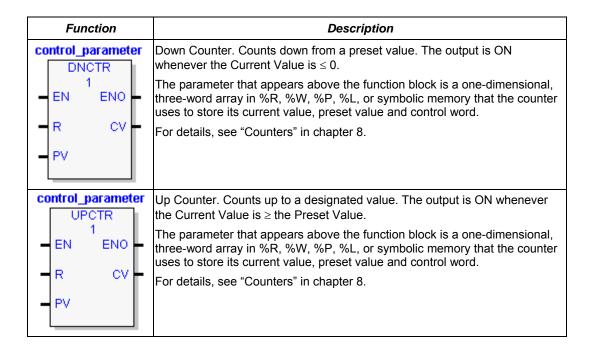

| Counters                                            |      |

| Down Counter                                        |      |

| Up Counter                                          |      |

| Data Move Functions                                 |      |

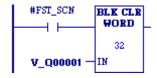

| Block Clear                                         |      |

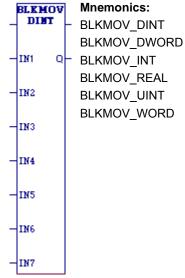

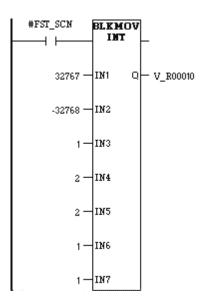

| Block Move                                          |      |

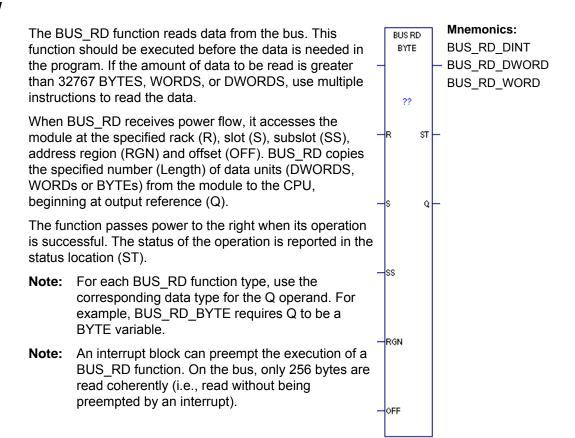

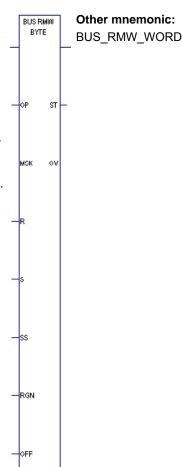

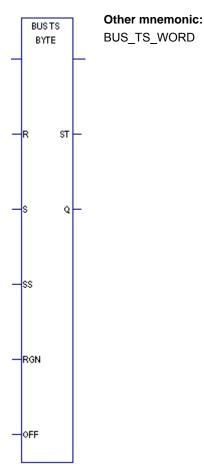

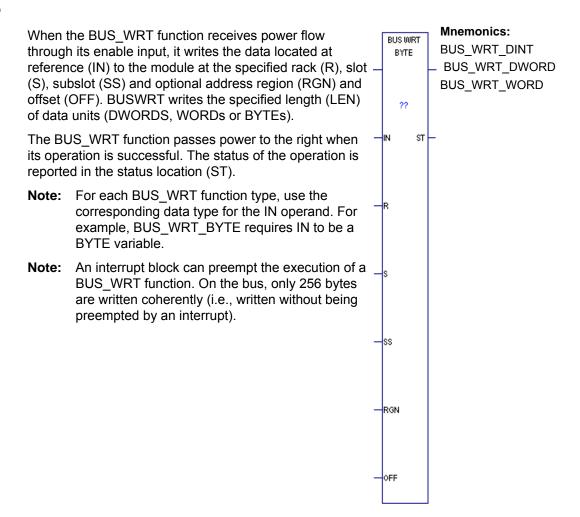

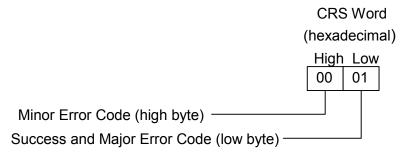

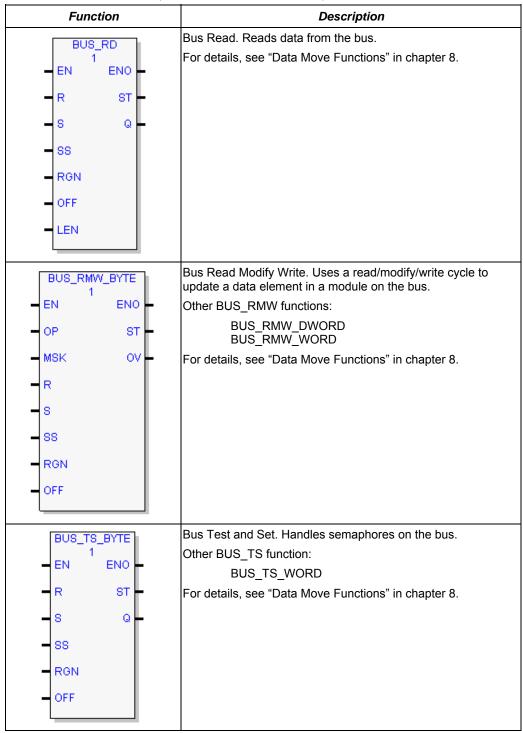

| BUS_ Functions                                      |      |

| Communication Request                               | 7-84 |

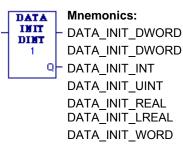

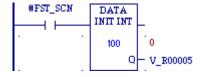

| Data Initialization                                                        | 7-89    |

|----------------------------------------------------------------------------|---------|

| Data Initialize ASCII                                                      | 7-90    |

| Data Initialize Communications Request                                     | 7-91    |

| Data Initialize DLAN                                                       | 7-91    |

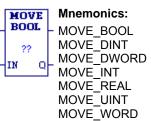

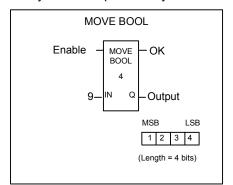

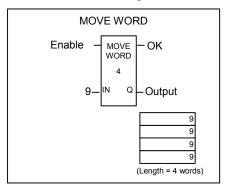

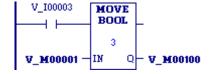

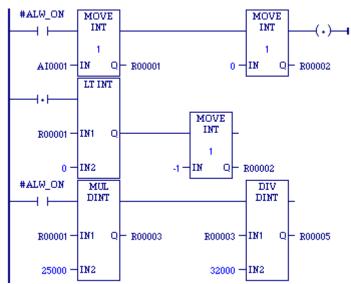

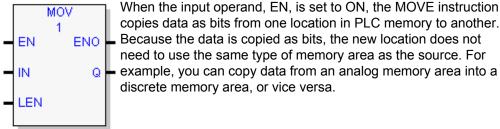

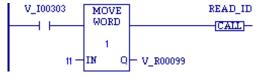

| Move                                                                       | 7-92    |

| Move_Data                                                                  | 7-94    |

| Shift Register                                                             | 7-95    |

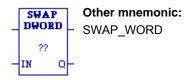

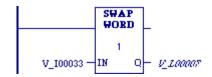

| Swap                                                                       | 7-97    |

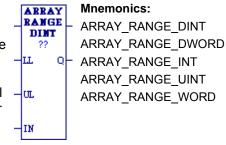

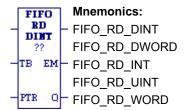

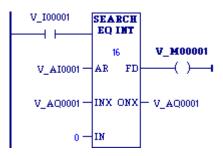

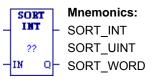

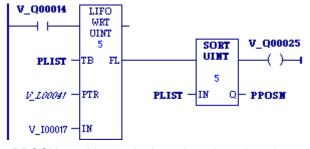

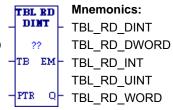

| Data Table Functions                                                       | 7-98    |

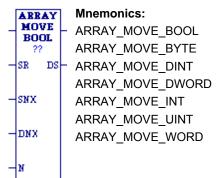

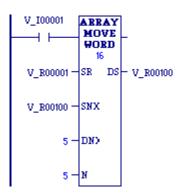

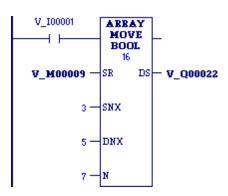

| Array Move                                                                 | 7-100   |

| Math Functions                                                             | 7-116   |

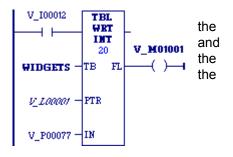

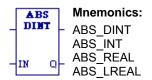

| Absolute Value                                                             | 7-117   |

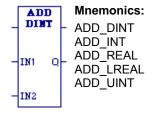

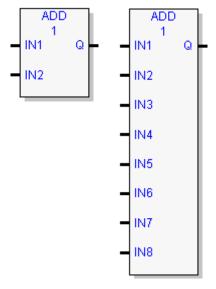

| Add                                                                        | 7-118   |

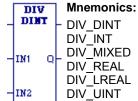

| Divide                                                                     | 7-120   |

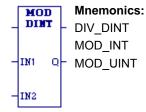

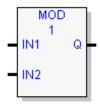

| Modulus                                                                    | 7-121   |

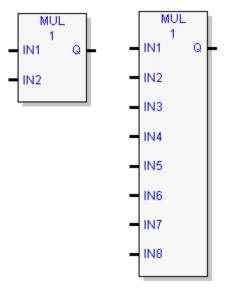

| Multiply                                                                   | 7-122   |

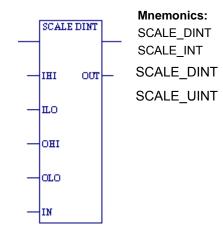

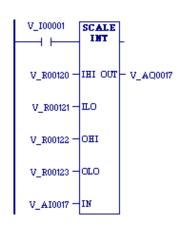

| Scale                                                                      | 7-124   |

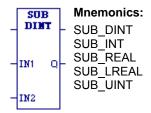

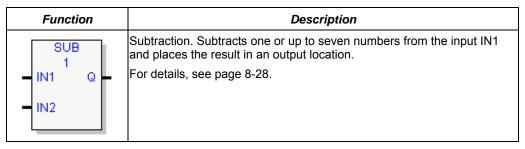

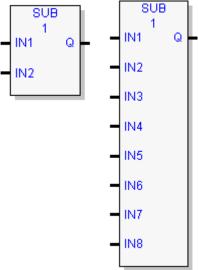

| Subtract                                                                   | 7-125   |

| Program Flow Functions                                                     | 7-126   |

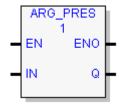

| Argument Present                                                           | 7-126   |

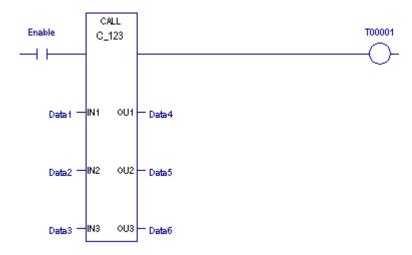

| Call                                                                       | 7-128   |

| Comment                                                                    | 7-131   |

| Jump                                                                       | 7-132   |

| Master Control Relay/End Master Control Relay                              | 7-133   |

| Wires                                                                      | 7-135   |

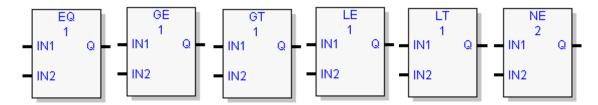

| Relational Functions                                                       | 7-136   |

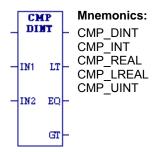

| Compare                                                                    | 7-137   |

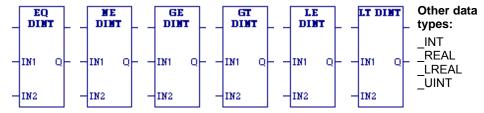

| Equal, Not Equal, Greater or Equal, Greater Than, Less or Equal, Less That | า 7-138 |

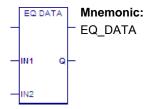

| EQ_DATA                                                                    | 7-139   |

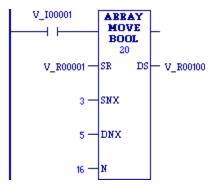

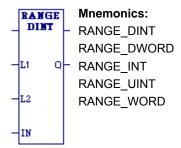

| Range                                                                      | 7-140   |

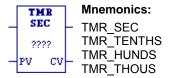

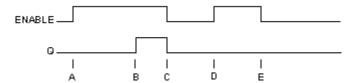

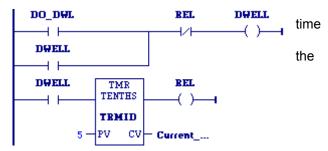

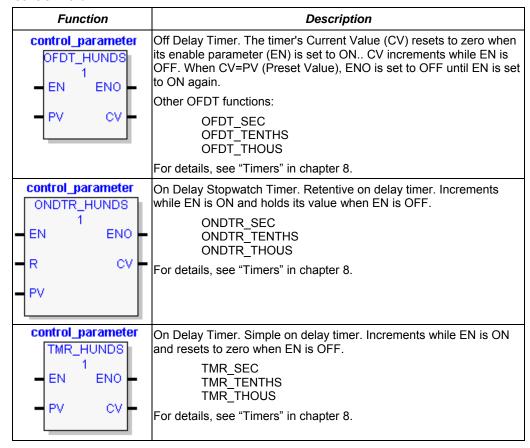

| Timers                                                                     | 7-141   |

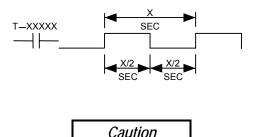

| Timed Contacts                                                             | 7-141   |

| Timer Function Blocks                                                      | 7-142   |

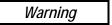

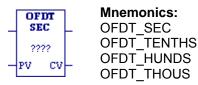

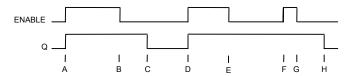

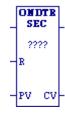

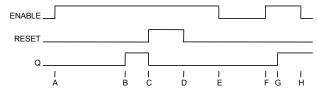

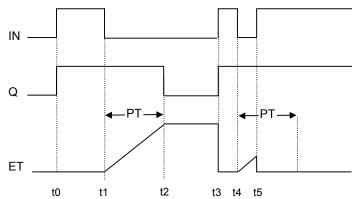

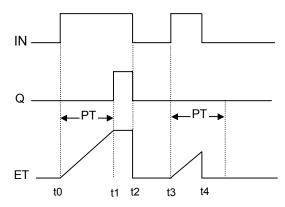

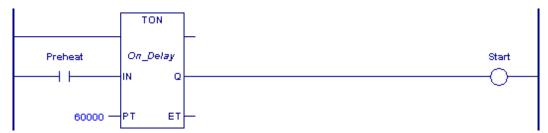

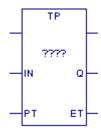

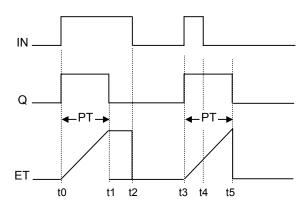

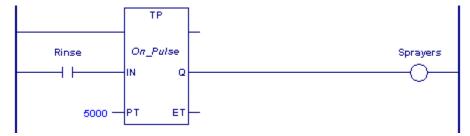

| Built-In Timer Function Blocks                                             | 7-142   |

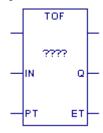

| Standard Timer Function Blocks                                             | 7-153   |

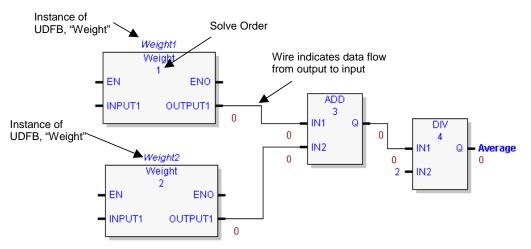

| Function Block Diagram                                                     | 8-1     |

| Advanced Math Functions                                                    | 8-2     |

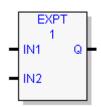

| EXPT Function                                                              |         |

| Bit Operation Functions                                                    |         |

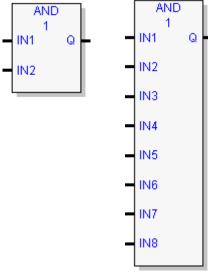

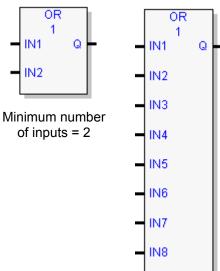

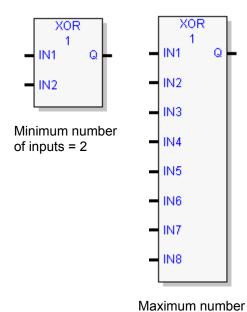

| Logical AND, Logical OR, and Logical XOR                                   |         |

| Logical NOT                                                                |         |

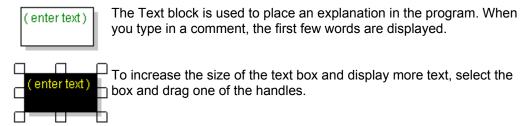

| Comments                                                                   |         |

| Text Block                                                                 |         |

|       | Comparison Functions                                                       |      |

|-------|----------------------------------------------------------------------------|------|

|       | Equal, Not Equal, Greater or Equal, Greater Than, Less or Equal, Less Than | 8-12 |

|       | Control Functions                                                          | 8-13 |

|       | Counters                                                                   | 8-15 |

|       | Data Move Functions                                                        | 8-16 |

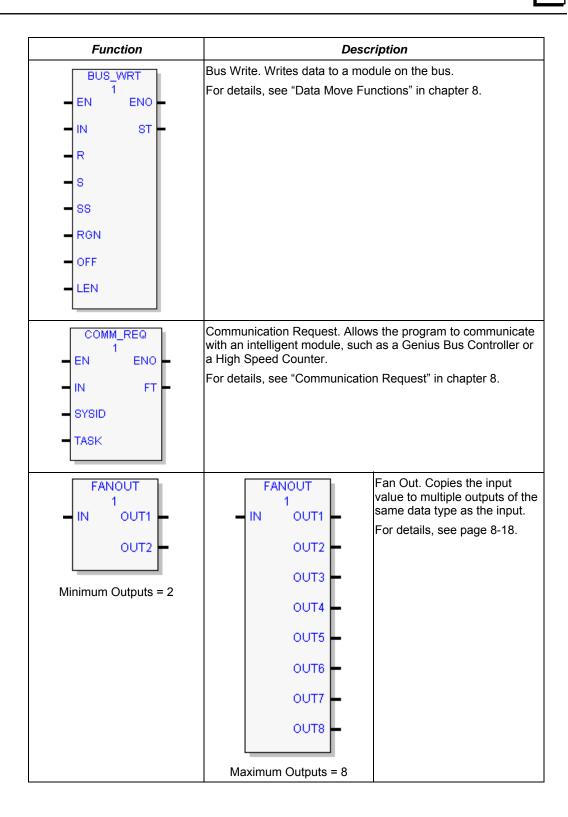

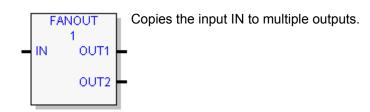

|       | Fan Out                                                                    | 8-18 |

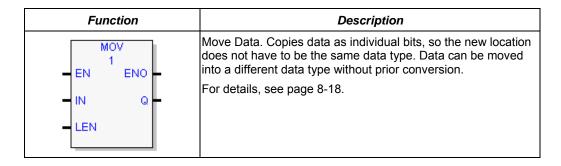

|       | Move Data                                                                  | 8-18 |

|       | Math Functions                                                             | 8-21 |

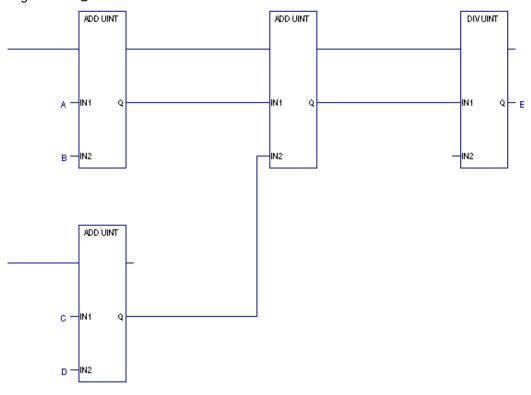

|       | Add                                                                        | 8-23 |

|       | Divide                                                                     |      |

|       | Modulus                                                                    |      |

|       | Multiply                                                                   |      |

|       | Negate                                                                     |      |

|       | Subtract                                                                   |      |

|       | Program Flow Functions                                                     |      |

|       | Timers                                                                     |      |

|       | Built-in Timer Function Blocks                                             |      |

|       | Standard Timer Function Blocks                                             |      |

|       | Type Conversion Functions                                                  |      |

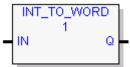

|       | Convert WORD to INT                                                        |      |

|       | Convert WORD to UINT                                                       |      |

|       | Convert DWORD to DINT                                                      |      |

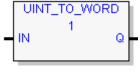

|       | Convert INT or UINT to WORD                                                |      |

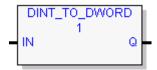

|       | Convert DINT to DWORD                                                      | 8-30 |

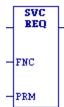

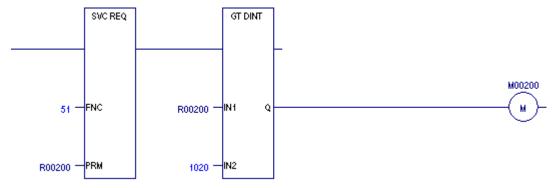

| Servi | ce Request Function                                                        | 9-1  |

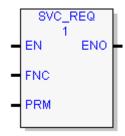

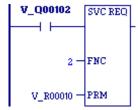

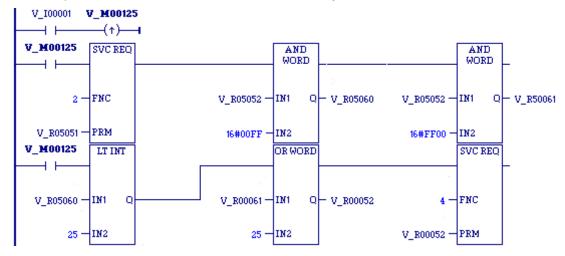

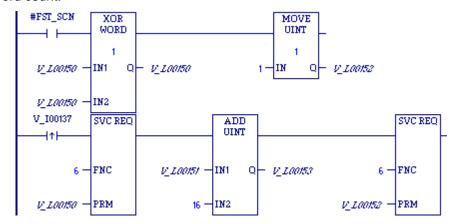

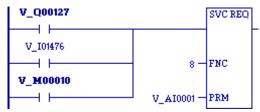

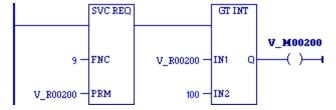

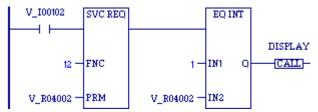

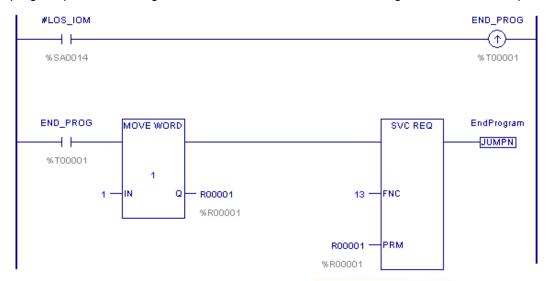

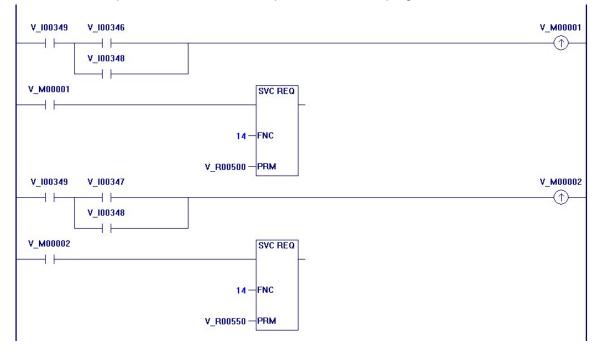

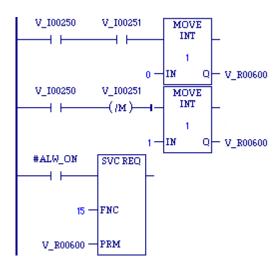

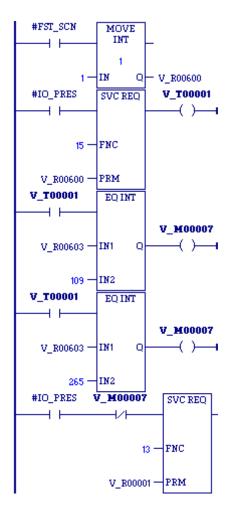

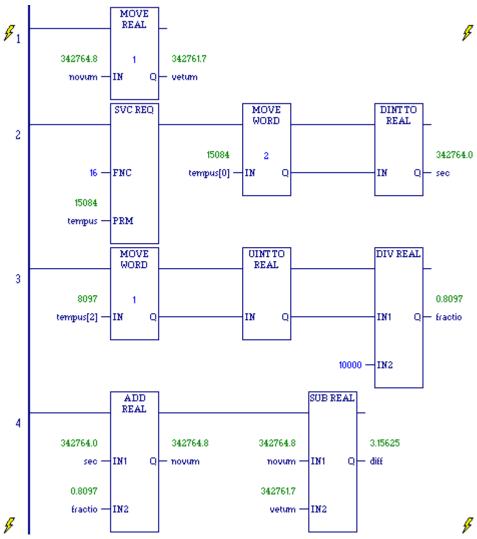

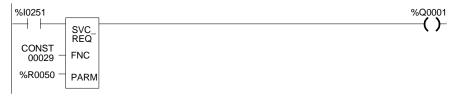

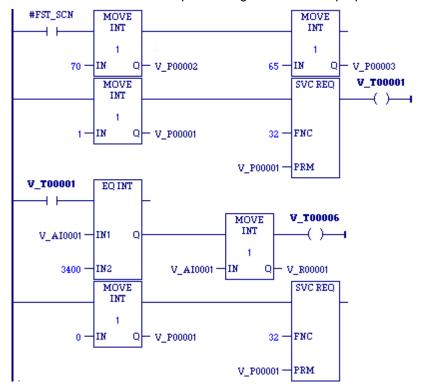

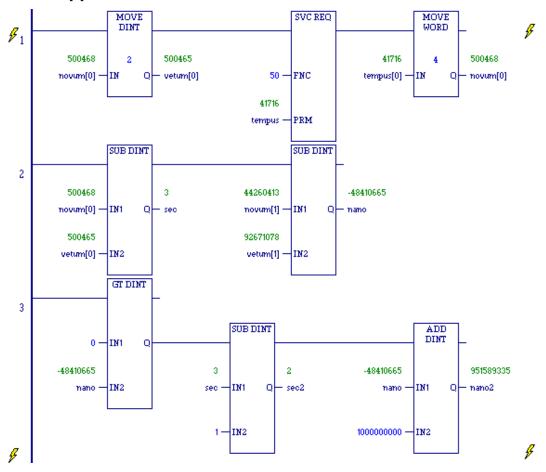

|       | Operation of SVC_REQ Function                                              | 9-2  |

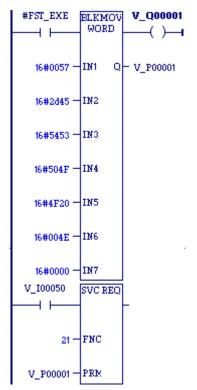

|       | Ladder Diagram                                                             |      |

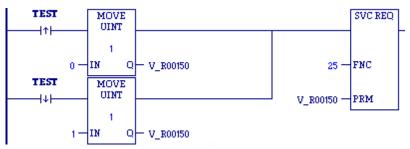

|       | Function Block Diagram                                                     | 9-3  |

|       | SVC_REQ 1: Change/Read Constant Sweep Timer                                | 9-4  |

|       | SVC_REQ 2: Read Window Modes and Times Values                              | 9-6  |

|       | SVC_REQ 3: Change Controller Communications Window Mode                    | 9-7  |

|       | SVC_REQ 4: Change Backplane Communications Window Mode and Timer Value.    | 9-8  |

|       | SVC_REQ 5: Change Background Task Window Mode and Timer Value              |      |

|       | SVC_REQ 6: Change/Read Number of Words to Checksum                         | 9-10 |

|       | SVC_REQ 7: Read or Change the Time-of-Day Clock                            |      |

|       | Parameter Block Formats                                                    |      |

|       | SVC_REQ 8: Reset Watchdog Timer                                            | 9-19 |

|       | SVC_REQ 9: Read Sweep Time from Beginning of Sweep                         |      |

|       | SVC REQ 10: Read Target Name                                               |      |

|       | SVC REQ 11: Read Controller ID                                             |      |

|       | SVC_REQ 12: Read Controller Run State                                      |      |

|       | SVC_REQ 13: Shut Down (Stop) CPU                                           |      |

|       | SVC_REQ 14: Clear PLC or I/O Fault Table                                   |      |

|       |                                                                            |      |

|       | SVC_REQ 15: Read Last-Logged Fault Table Entry                          | 9-25  |

|-------|-------------------------------------------------------------------------|-------|

|       | SVC_REQ 16: Read Elapsed Time Clock                                     | 9-27  |

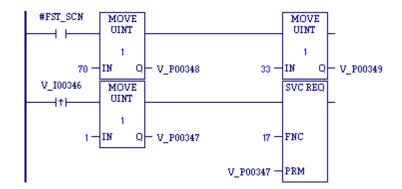

|       | SVC_REQ 17: Mask/Unmask I/O Interrupt                                   | 9-29  |

|       | Masking/Unmasking Module Interrupts                                     | 9-29  |

|       | SVC_REQ 18: Read I/O Forced Status                                      | 9-31  |

|       | SVC_REQ 19: Set Run Enable/Disable                                      | 9-32  |

|       | SVC_REQ 20: Read Fault Tables                                           | 9-33  |

|       | Non-Extended Formats                                                    | 9-33  |

|       | Extended Formats                                                        |       |

|       | SVC_REQ 20 Examples                                                     |       |

|       | SVC_REQ 21: User-Defined Fault Logging                                  |       |

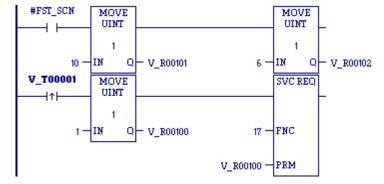

|       | SVC_REQ 22: Mask/Unmask Timed Interrupts                                | 9-40  |

|       | SVC_REQ 23: Read Master Checksum                                        | 9-41  |

|       | SVC_REQ 24: Reset Module                                                | 9-42  |

|       | SVC_REQ 25: Disable/Enable EXE Block and Standalone C Program Checksums | 9-43  |

|       | SVC_REQ 29: Read Elapsed Power Down Time                                | 9-44  |

|       | SVC_REQ 32: Suspend/Resume I/O Interrupt                                | 9-45  |

|       | SVC_REQ 45: Skip Next I/O Scan                                          | 9-47  |

|       | SVC_REQ 50: Read Elapsed Time Clock                                     | 9-48  |

|       | SVC_REQ 51: Read Sweep Time from Beginning of Sweep                     | 9-50  |

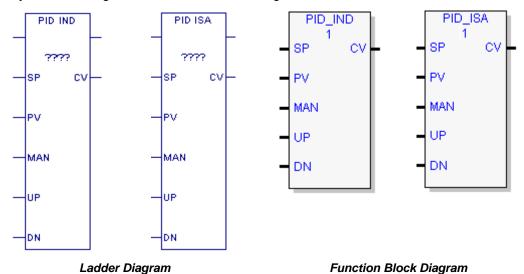

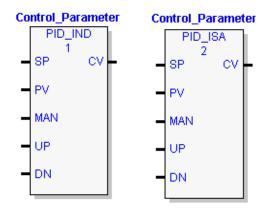

| PID E | Built-in Function Block                                                 | 10-1  |

|       | Operands of the PID Function                                            | 10-2  |

|       | Operands for LD Version of PID Function Block                           |       |

|       | Operands for FBD Version of PID Function Block                          |       |

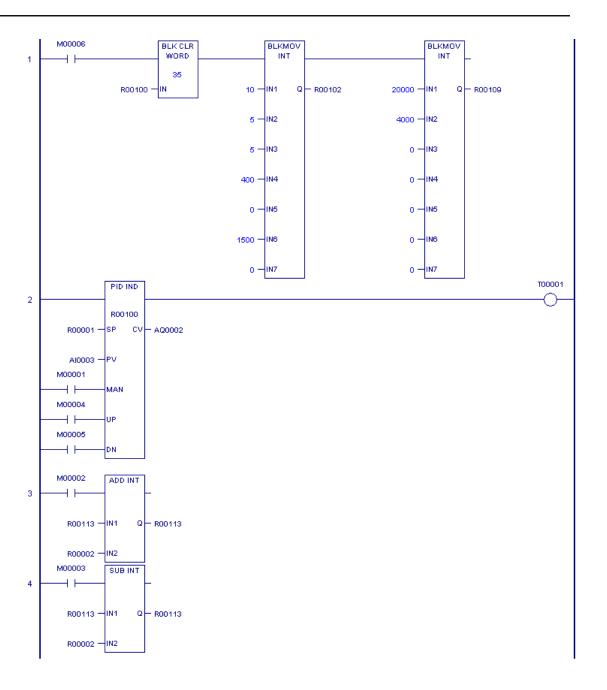

|       | Reference Array for the PID Function                                    | 10-4  |

|       | Scaling Input and Outputs                                               | 10-4  |

|       | Reference Array Parameters                                              | 10-5  |

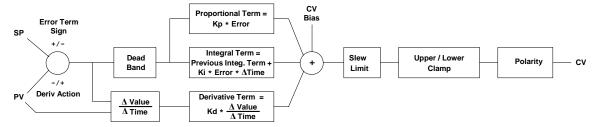

|       | Operation of the PID Function                                           | 10-10 |

|       | Automatic Operation                                                     | 10-10 |

|       | Manual Operation                                                        |       |

|       | Time Interval for the PID Function                                      |       |

|       | PID Algorithm Selection (PIDISA or PIDIND) and Gain Calculations        |       |

|       | Error Term                                                              |       |

|       | Derivative Term                                                         |       |

|       | CV Bias Term                                                            |       |

|       | CV Amplitude and Rate Limits                                            |       |

|       | Sample Period and PID Function Block Scheduling                         |       |

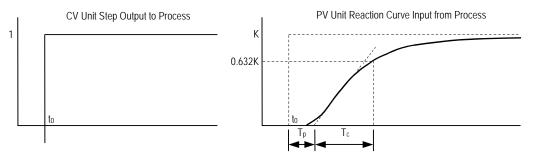

|       | Determining the Process Characteristics                                 |       |

|       | Setting Tuning Loop Gains                                               |       |

|       | Basic Iterative Tuning Approach                                         |       |

|       | Setting Loop Gains Using the Ziegler and Nichols Tuning Approach        |       |

|       | Ideal Tuning Method  Example                                            |       |

|       | LAQIIIVID                                                               | IU-IB |

| Structured Text Programming                                | 11-1  |

|------------------------------------------------------------|-------|

| Language Overview                                          | 11-1  |

| Statements                                                 | 11-1  |

| Expressions                                                | 11-1  |

| Operators                                                  | 11-2  |

| Structured Text Syntax                                     | 11-3  |

| Statement Types                                            | 11-4  |

| Assignment Statement                                       | 11-5  |

| Function Call                                              | 11-6  |

| RETURN Statement                                           | 11-10 |

| IF Statement                                               | 11-11 |

| CASE Statement                                             | 11-12 |

| FOR Statement                                              | 11-14 |

| WHILE Statement                                            | 11-16 |

| REPEAT Statement                                           |       |

| ARG_PRES Statement                                         | 11-18 |

| Exit Statement                                             | 11-19 |

| Communications                                             | 12-1  |

| Ethernet Communications                                    | 12-2  |

| Embedded Ethernet Interface                                | 12-2  |

| Ethernet Interface Modules                                 | 12-2  |

| Serial Communications                                      | 12-3  |

| Serial Port Communications Capabilities                    |       |

| Configurable Stop Mode Protocols                           | 12-4  |

| Serial Port Pin Assignments                                | 12-4  |

| Serial Port Baud Rates                                     | 12-7  |

| Series 90-70 Communications and Intelligent Option Modules | 12-8  |

| Communications Coprocessor Module (CMM)                    | 12-8  |

| Programmable Coprocessor Module (PCM)                      | 12-9  |

| DLAN/DLAN+ (Drives Local Area Network) Interface           | 12-10 |

| Serial I/O, SNP and RTU Protocols                          | 13-1  |

| Configuring Serial Ports Using the COMM_REQ Function       | 13-2  |

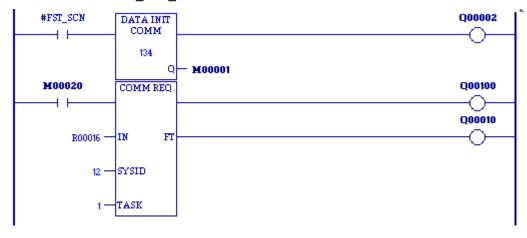

| COMM_REQ Function Example                                  |       |

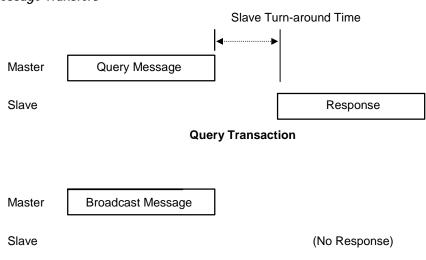

| Timing                                                     | 13-2  |

| Sending Another COMM_REQ to the Same Port                  | 13-2  |

| Invalid Port Configuration Combinations                    | 13-3  |

| COMM_REQ Command Block Parameter Values                    |       |

| Sample COMM_REQ Command Blocks                             |       |

| Calling Serial I/O COMM_REQs from the CPU Sweep            | 13-7  |

| Compatibility                                              |       |

| Status Word for Serial I/O COMM_REQs                       | 13-8  |

| Serial I/O COMM_REQ Commands                            | 13-9  |

|---------------------------------------------------------|-------|

| Overlapping COMM_REQs                                   | 13-9  |

| Initialize Port Function (4300)                         | 13-10 |

| Set Up Input Buffer Function (4301)                     | 13-11 |

| Flush Input Buffer Function (4302)                      | 13-11 |

| Read Port Status Function (4303)                        | 13-12 |

| Write Port Control Function (4304)                      | 13-14 |

| Cancel COMM_REQ Function (4399)                         | 13-15 |

| Autodial Function (4400)                                | 13-16 |

| Write Bytes Function (4401)                             | 13-18 |

| Read Bytes Function (4402)                              | 13-19 |

| Read String Function (4403)                             | 13-21 |

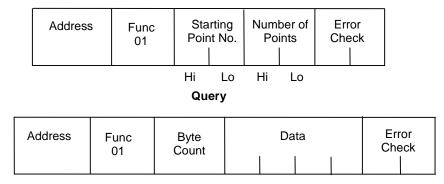

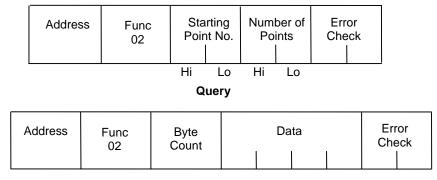

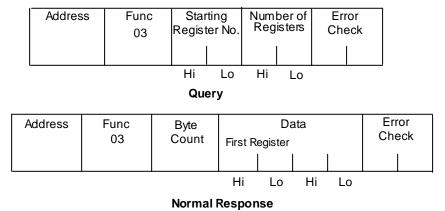

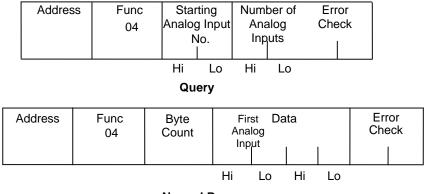

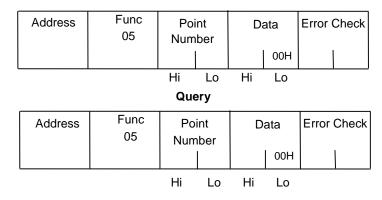

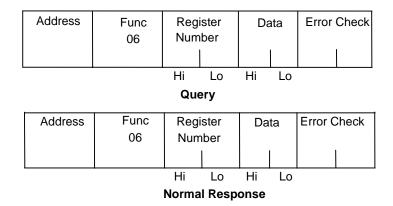

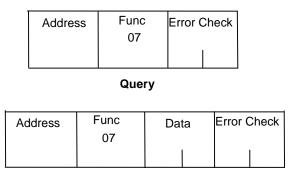

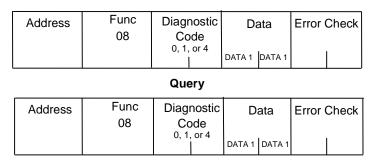

| RTU Slave Protocol                                      | 13-23 |

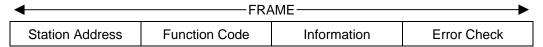

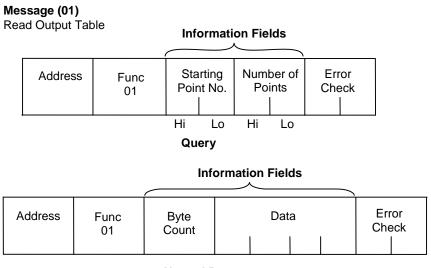

| Message Format                                          | 13-23 |

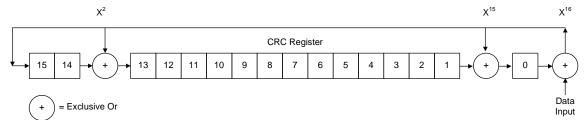

| Cyclic Redundancy Check (CRC)                           | 13-28 |

| Calculating the CRC-16                                  | 13-29 |

| Sample CRC-16 Calculation                               | 13-29 |

| Calculating the Length of Frame                         | 13-31 |

| RTU Message Descriptions                                | 13-32 |

| RTU Scratch Pad                                         | 13-48 |

| Communication Errors                                    | 13-49 |

| RTU Slave/SNP Slave Operation With Programmer Attached  | 13-51 |

| SNP Slave Protocol                                      | 13-52 |

| Permanent Datagrams                                     | 13-52 |

| Communication Requests (COMM_REQs) for SNP              | 13-52 |

| Disconnection                                           | 44.4  |

| Diagnostics                                             |       |

| Fault Handling Overview                                 |       |

| System Response to Faults                               |       |

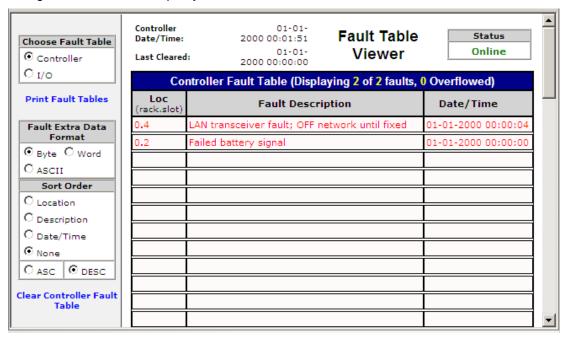

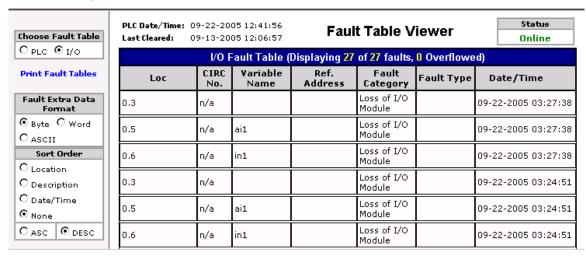

| Fault Tables                                            |       |

| Fault Actions and Fault Action Configuration            |       |

| Using the Fault Tables                                  |       |

| Controller Fault Table                                  |       |

| I/O Fault Table                                         | 14-6  |

| System Handling of Faults                               | 14-8  |

| System Fault References                                 | 14-8  |

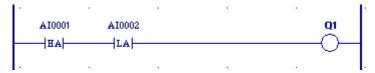

| Using Fault Contacts                                    | 14-11 |

| Using Point Faults                                      | 14-13 |

| Using Alarm Contacts                                    | 14-13 |

| Controller Fault Descriptions and Corrective Actions    | 14-14 |

| Loss of or Missing Rack (Group 1)                       | 14-15 |

| Loss of or Missing Option Module (Group 4)              | 14-16 |

| Addition of, or Extra Rack (Group 5)                    | 14-16 |

| Reset of, Addition of, or Extra Option Module (Group 8) | 14-17 |

| System Configuration Mismatch (Group 11)                | 14-18 |

|                                                         |       |

|       | System Bus Error (Group 12)                        | 14-23 |

|-------|----------------------------------------------------|-------|

|       | CPU Hardware Failure (Group 13)                    | 14-24 |

|       | Module Hardware Failure (Group 14)                 | 14-25 |

|       | Option Module Software Failure (Group 16)          | 14-25 |

|       | Program or Block Checksum Failure (Group 17)       | 14-27 |

|       | Battery Status (Group 18)                          | 14-28 |

|       | Constant Sweep Time Exceeded (Group 19)            | 14-28 |

|       | System Fault Table Full (Group 20)                 | 14-29 |

|       | I/O Fault Table Full (Group 21)                    | 14-29 |

|       | User Application Fault (Group 22)                  | 14-29 |

|       | CPU Over Temperature (Group 24)                    | 14-31 |

|       | Power Supply Fault (Group 25)                      | 14-32 |

|       | No User Program on Power-Up (Group 129)            | 14-32 |

|       | Corrupted User Program on Power-Up (Group 130)     | 14-33 |

|       | Window Completion Failure (Group 131)              |       |

|       | Password Access Failure (Group 132)                | 14-34 |

|       | Null System Configuration for Run Mode (Group 134) | 14-34 |

|       | CPU System Software Failure (Group 135)            |       |

|       | Communications Failure During Store (Group 137)    | 14-36 |

|       | Noncritical CPU Software Event (Group 140)         | 14-37 |

| I/O F | ault Descriptions and Corrective Actions           |       |

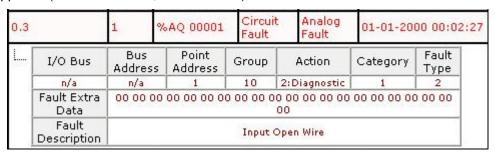

|       | Fault Extra Data                                   | 14-38 |

|       | I/O Fault Groups                                   | 14-38 |

|       | I/O Fault Categories                               | 14-39 |

|       | Circuit Faults (Category 1)                        | 14-41 |

|       | Loss of Block (Category 2)                         | 14-47 |

|       | Addition of Block (Category 3)                     | 14-48 |

|       | I/O Bus Fault (Category 6)                         |       |

|       | Module Fault (Category 8)                          | 14-50 |

|       | Addition of IOC (Category 9)                       | 14-51 |

|       | Loss of or Missing IOC (Category 10)               | 14-51 |

|       | IOC (I/O Controller) Software Fault (Category 11)  |       |

|       | Forced and Unforced Circuit (Categories 12 and 13) | 14-52 |

|       | Loss of or Missing I/O Module (Category 14)        | 14-53 |

|       | Addition of I/O Module (Category 15)               | 14-53 |

|       | Extra I/O Module (Category 16)                     | 14-53 |

|       | Extra Block (Category 17)                          | 14-54 |

|       | IOC Hardware Failure (Category 18)                 | 14-54 |

|       | GBC Stopped Reporting Faults (Category 19)         | 14-54 |

|       | GBC Software Exception (Category 21)               | 14-55 |

|       | Block Switch (Category 22)                         |       |

|       | Reset of IOC (Category 27)                         |       |

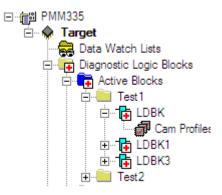

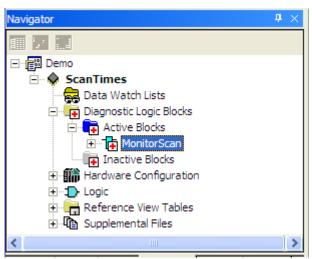

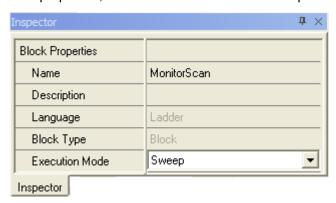

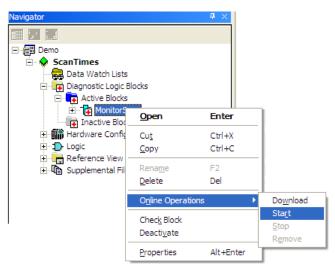

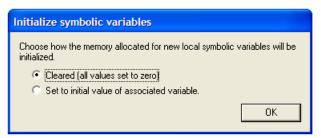

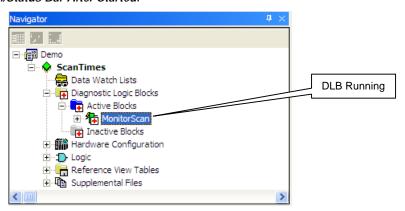

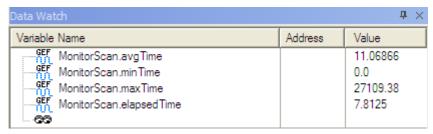

| Diagi | nostic Logic Blocks                                |       |

| 3     | DLB Operation                                      |       |

|       | Executing DLBs                                     |       |

|       | DLB Example                                        |       |

|       |                                                    |       |

| Performance Data                            | A-1  |

|---------------------------------------------|------|

| Boolean Execution Times                     | A-1  |

| Instruction Timing                          | A-2  |

| Function/Function Block Execution Times     | A-2  |

| Incremental Times                           | A-12 |

| Overhead Sweep Impact Times                 | A-15 |

| Base Sweep Times                            | A-15 |

| What the Sweep Impact Tables Contain        | A-17 |

| Programmer Sweep Impact Times               | A-17 |

| I/O Scan and I/O Fault Sweep Impact         | A-18 |

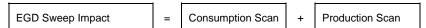

| Ethernet Global Data Sweep Impact           | A-24 |

| Sweep Impact of Intelligent Option Modules  | A-27 |

| I/O Interrupt Performance and Sweep Impact  | A-28 |

| Timed Interrupt Performance                 | A-29 |

| Example of Predicted Sweep Time Calculation | A-30 |

| User Memory Allocation                      | B-1  |

| Items that Count Against User Memory        | B-2  |

| User Program Memory Usage                   | B-3  |

| %L and %P Program Memory                    |      |

| Program Logic and Overhead                  | B-3  |

# Chapter

# Introduction

1

This manual contains general information about PACSystems CPU operation and program content. It also provides detailed descriptions of specific programming requirements.

Chapter 1 provides a **general introduction** to the PACSystems family of products, including new features, product overviews, and a list of related documentation.

CPU hardware features and specifications are provided in chapter 2.

**Installation procedures** are described in the *PACSystems RX7i Installation Manual,* GFK-2223 and the *PACSystems RX3i Installation Manual,* GFK-2314.

**CPU Configuration** is described in chapter 3. Configuration using the programming software determines characteristics of module operation and establishes the program references used by each module in the system. For details on configuration of the embedded RX7i Ethernet interface as well as the rack-based RX7i and RX3i Ethernet Interface modules, refer to *TCP/IP Ethernet Communications for PACSystems*, GFK-2224.

CPU Operation is described in chapter 4.

Programming Features are described in chapters 5 through 9 and Appendix A.

- Elements of an Application Program: chapter 5

- Program Data: chapter 6

- Ladder Diagram (LD) instruction set reference: chapter 7

- Function Block Diagram (FBD) instruction set reference: chapter 8

- The Service Request Function: chapter 9

- The PID Function: chapter 10

- Structured Text (ST): chapter 11

Ethernet and Serial Communications are described in chapter 12.

Serial I/O, SNP, and RTU Protocols are described in chapter 13.

**Diagnostics**, including Fault Handling and Diagnostic Logic Blocks are described in chapter 14.

**Instruction Timing** is provided in appendix A.

User Memory Allocation is described in Appendix B.

GFK-2222M 1-1

# New Features

**Note:** A given feature may not be implemented on all PACSystems CPUs. To determine whether a feature is available on a given CPU model and firmware version, please refer to the *Important Product Information* (IPI) document provided with the CPU.

This revision of the PACSystems CPU Reference Manual includes the following new features:

# RX3i High Availability Redundancy

Rx3i High Availability Redundancy uses CPU hot standby redundancy, in which the primary CPU controls the application and the secondary CPU takes over if the first controller fails. The controllers are synchronized so that control can transition to the secondary controller without a bump in the process. Hot standby redundancy requires a CRU320 Redundancy CPU and one or two RMX128 Redundancy Memory Xchange modules per controller. RX3i redundancy supports the RX3i ENIU I/O LAN.

For details on the operation of PACSystems CPU redundancy systems, refer to the *PACSystems Hot Standby CPU Redundancy User's Manual*, GFK-2308. For information on the ENIU LAN, refer to the *PACSystems RX3i Ethernet NIU User's Manual*, GFK-2439.

#### **PACMotion**

- Support for the Multi-Axis Motion Controller, IC695PMM335 and the Fiber I/O Terminal Block, IC695FTB001.

- The RX3i CPUs and PMM335 motion modules now support 56 PLCopen compliant motion functions and function blocks. Details of these function blocks can be found in the PACMotion Multi-Axis Motion Controller User's Manual, GFK-2448.

### Diagnostic Logic Blocks

To assist with commissioning and diagnostics, a diagnostic logic block can be downloaded to the RX3i CPU and executed without altering the main program logic. (DLBs are not supported on Redundancy CPUs.)

### MOVE\_DATA and EQ\_DATA Functions

These functions data are used to copy and compare data in structured variables.

# PACSystems Control System Overview

The PACSystems controller environment combines performance, productivity, openness and flexibility. The PACSystems control system integrates advanced technology with GE Fanuc's existing systems. The result is seamless migration that protects your investment in I/O and application development.

# Programming and Configuration

Proficy® Machine Edition programming software provides a universal engineering development environment for all programming, configuration and diagnostics of PACSystems. A PACSystems CPU is programmed and configured using the programming software to perform process and discrete automation for various applications. The CPU communicates with I/O and smart option modules through a rackmounted backplane. It communicates with the programmer and/or HMI devices via the Ethernet ports (may be embedded for RX7i) or via the serial ports 1 and 2 using GE Fanuc Serial I/O, or Modbus RTU slave protocols.

# Process Systems

PACSystems CPUs with firmware version 5.0 and later support Proficy Process Systems (PPS). PPS is a complete, tightly integrated, seamless process control system using PACSystems, Proficy HMI/SCADA, and Proficy Production Management Software to provide control, optimization, and performance management to manage and monitor batch or continuous manufacturing. It delivers the tools required to design, implement, document, and maintain an automated process. For information about purchasing PPS software, refer to <a href="http://www.gefanuc.com/">http://www.gefanuc.com/</a>.

GFK-2222M Chapter 1 Introduction 1-3

# PACSystems CPU Models

| Family                           | Catalog<br>Number | Description                                                                                             |

|----------------------------------|-------------------|---------------------------------------------------------------------------------------------------------|

| RX3i CPUs                        | IC695CPU310       | 300MHz Celeron CPU, 10 MB user memory                                                                   |

|                                  | IC695CPU320       | 1 GHz Celeron-M CPU, 64 MB user memory                                                                  |

|                                  | IC695NIU001       | 300MHz Celeron NIU. For information, see the<br>PACSystems RX3i Ethernet NIU User's Manual,<br>GFK-2439 |

| RX3i Redundancy CPU IC695CRU32   |                   | 1 GHz Celeron-M CPU, 64 MB user memory                                                                  |

| RX7i CPUs with embedded          | IC698CPE010       | 300MHz, Celeron CPU, 10MB user memory                                                                   |

| Ethernet Interface               | IC698CPE020       | 700MHz, Pentium CPU, 10 MB user memory,                                                                 |

|                                  | IC698CPE030       | 600MHz, Pentium-M CPU, 64MB user memory                                                                 |

|                                  | IC698CPE040       | 1800MHz, Pentium-M CPU, 64MB user memory                                                                |

| RX7i Redundancy CPUs             | IC698CRE020       | 700MHz, Pentium CPU, 10 MB user memory                                                                  |

| with embedded Ethernet Interface | IC698CRE030       | 600MHz, Pentium-M CPU, 64MB user memory                                                                 |

| Zuioniot intoriado               | IC698CRE040       | 1800MHz, Pentium-M CPU, 64MB user memory                                                                |

PACSystems CPU models have the following features in common:

- Programming in Ladder Diagram, Function Block Diagram, Structured Text and C.

- Floating point (real) data functions.

- Configurable data and program memory.

- Battery-backed RAM for user data (program, configuration, register data, and symbolic variable) storage

- Non-volatile built-in flash memory for user data (program, configuration, register data, and symbolic variable) storage. Use of this flash memory is optional.

- Battery backup for program, data, and time of day clock.

- Configurable Run/Stop mode switch.

- Embedded RS-232 and RS-485 communications.

- Up to 512 program blocks. Maximum size for a block is 128KB.

- Auto Located Symbolic Variables, which allows you to create a variable without specifying a reference address.

- Bulk memory area accessed via reference table %W. The upper limit of this memory area can be configured to the maximum available user RAM.

- Larger reference table sizes, compared to Series 90 CPUs: 32Kbits for discrete %l and %Q and up to 32K words each for analog %Al and %AQ.

- Online Editing mode that allows you to easily test modifications to a running program. (For details on using this feature, refer to the programming software online help and *Proficy™ Logic Developer Getting Started*, GFK-1918.)

- Bit in word referencing that allows you to specify individual bits in a WORD reference in retentive memory as inputs and outputs of Boolean expressions, function blocks, and calls that accept bit parameters.

- In-system upgradeable firmware.

### RX3i Overview

The RX3i control system hardware consists of an RX3i universal backplane and up to seven Series 90-30 expansion or remote racks. The CPU can be in any slot in the universal backplane except the last slot, which is reserved for the serial bus transmitter, IC695LRE001.

The RX3i supports user defined Function Blocks (LD logic only) and Structured Text programming.

The RX3i universal backplane uses a dual bus that provides both:

- High-speed, PCI for fast throughput of new advanced I/O.

- Serial backplane for easy migration of existing Series 90-30 I/O

The RX3i universal backplane and Series 90-30 expansion/remote racks support the Series 90-30 Genius Bus Controller and Motion Control modules, and most Series 90-30/RX3i discrete and analog I/O with catalog prefixes IC693 and IC694. RX3i modules with catalog prefixes IC695, including the Ethernet and other communications modules can only be installed in the universal backplane. See the *PACSystems RX3i System Manual*, GFK-2314 for a list of supported modules.

RX3i supports hot standby (HSB) CPU redundancy, which allows a critical application or process to continue operating if a failure occurs in any single component. A CPU redundancy system consists of an active unit that actively controls the process and a backup unit that is synchronized with the active unit and can take over the process if it becomes necessary. Each unit must have a redundancy CPU, (IC695CRU320). The redundancy communication path is provided by IC695RMX128 Redundancy Memory Xchange (RMX) modules set up as redundancy links. For details on the operation of PACSystems redundancy systems, refer to the *PACSystems Hot Standby CPU Redundancy User's Guide*, GFK-2308.

RX3i communications features include:

- Open communications support includes Ethernet, and serial protocols. The Ethernet Interface (resides in a backplane slot) has dual RJ-45 ports connected through an auto-sensing switch. This eliminates the need for rack-to-rack switches or hubs. The Ethernet Interface supports upload, download and online monitoring, and provides 32 SRTP channels and allows a maximum of 48 simultaneous SRTP server connections. For details on Ethernet Interface capabilities, refer to TCP/IP Ethernet Communications for PACSystems, GFK-2224.

- The RX3i supports PROFIBUS communications via the PROFIBUS Master module. For details, refer to the PACSystems RX3i PROFIBUS Modules User's Manual, GFK-2301.

- Two serial ports, one RS-232 and one RS-485.

GFK-2222M Chapter 1 Introduction 1-5

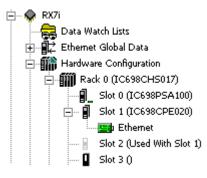

### RX7i Overview

The RX7i control system hardware consists of an RX7i rack and up to seven Series 90-70 expansion racks. The CPU resides in slot 1 of the main rack. RX7i racks use a VME64 backplane that provides up to four times the bandwidth of existing VME based systems, including the current Series 90-70 systems for faster I/O throughput. The VME64 base supports all standard VME modules including Series 90-70 I/O and VMIC modules.

Expansion racks support Series 90-70 discrete and analog I/O, the Genius Bus Controller, and the High Speed Counter. The CPU provides an embedded auto-sensing 10/100 Mbps half/full duplex Ethernet interface.

RX7i supports hot standby (HSB) CPU redundancy, which allows a critical application or process to continue operating if a failure occurs in any single component. A CPU redundancy system consists of an active unit that actively controls the process and a backup unit that is synchronized with the active unit and can take over the process if it becomes necessary. Each unit must have a redundancy CPU, (IC698CRE020, CRE030 or CRE040). The redundancy communication path is provided by IC698RMX016 Redundancy Memory Xchange (RMX) modules set up as redundancy links. For details on the operation of PACSystems redundancy systems, refer to the *PACSystems Hot Standby CPU Redundancy User's Guide*, GFK-2308.

**Note:** Extended operation with dissimilar CPU types is *not allowed*. During normal operation, the primary and secondary units in an HSB redundancy system must have the same CPU model type.

The primary and secondary units of an HSB redundancy system can have dissimilar model types for a limited time, for the purpose of system upgrade only. Fail wait times for the higher performance CPU in a dissimilar redundant pair may need to be increased to allow synchronization.

#### RX7i communications features include:

- Open communications support includes Ethernet, Genius, and serial protocols.

- A built-in 10/100mb Ethernet interface that has dual RJ-45 ports connected through an auto-sensing switch for upload, download and online monitoring. This eliminates the need for rack-to-rack switches or hubs. The CPU Ethernet Interface provides basic remote control system monitoring from a web browser and allows a combined total of up to 16 web server and FTP connections. For details on Ethernet Interface capabilities, refer to TCP/IP Ethernet Communications for PACSystems, GFK-2224.

- Two serial ports, one RS-232 and one RS-485.

- An RS-232 isolated Ethernet station manager serial port.

# Migrating Series 90 Applications to PACSystems

The PACSystems control system provides cost-effective expansion of existing systems. Support for existing Series 90 modules, expansion racks and remote racks protects your hardware investment. You can upgrade on your timetable without disturbing panel wiring.

- The RX3i supports most Series 90-30 modules, expansion racks, and remote racks. For a list of supported I/O, Communications, Motion, and Intelligent modules, see the *PACSystems RX3i Installation Manual*, GFK-2314.

- The RX7i supports most existing Series 90-70 modules, expansion racks and Genius networks. For a list of supported I/O, Communications, and Intelligent modules, see the *PACSystems RX7i Installation Manual*, GFK-2223.

- Conversion of Series 90-70 and Series 90-30 programs preserves existing development effort.

- Conversion of VersaPro and Logicmaster applications to Machine Edition allows smooth transition to PACSystems.

GFK-2222M Chapter 1 Introduction 1-7

# PACSystems Documentation

#### PACSystems Manuals

PACSystems CPU Reference Manual, GFK-2222

TCP/IP Ethernet Communications for PACSystems, GFK-2224

Station Manager for PACSystems, GFK-2225

PACSystems C Toolkit User's Guide, GFK-2259

PACSystems Memory Xchange Modules User's Manual, GFK-2300

PACSystems Hot Standby CPU Redundancy User's Manual, GFK-2308

Proficy Machine Edition Logic Developer Getting Started, GFK-1918

Proficy Process Systems Getting Started Guide, GFK-2487

#### RX3i Manuals

PACSystems RX3i Hardware and Installation Manual, GFK-2314 DSM324i Motion Controller for PACSystems RX3i and Series 90-30, GFK-2347 PACSystems RX3i PROFIBUS Modules User's Manual, GFK-2301 PACSystems RX3i MAXON Software User's Manual, GFK-2409 PACSystems RX3i Ethernet NIU User's Manual, GFK-2439 PACMotion Multi-Axis Motion Controller User's Manual, GFK-2448

#### RX7i Manuals

PACSystems RX7i Hardware and Installation Manual, GFK-2223

PACSystems RX7i User's Guide to Integration of VME Modules, GFK-2235

Genius Bus Controller User's Manual, GFK-2017

#### Series 90 Manuals

Series 90 Programmable Coprocessor Module and Support Software, GFK-0255 Series 90 PLC Serial Communications Driver User's Manual, GFK-0582 C Programmer's Toolkit for Series 90 PLCs User's Manual, GFK-0646 Installation Requirements for Conformance to Standards, GFK-1179

TCP/IP Ethernet Communications for the Series 90 PLC Station Manager Manual, GFK-1186

Series 90-70 Programmable Controller Installation Manual, GFK-0262 Series 90-70 CPU Instruction Set Reference Manual, GFK-0265

Series 90-30 Genius Bus Controller, GFK-1034

Series 90-30 System Manual, GFK-1411

Ethernet NIU User's Manual, GFK-2296

Genius I/O System User's Manual, GEK-90486-1

Genius I/O Analog and Discrete Blocks User's Manual, GEK-90486-2

In addition to these manuals, datasheets and product update documents describe individual modules and product revisions. The most recent PACSystems documentation is available on the GE Fanuc website: <a href="http://www.gefanuc.com/">http://www.gefanuc.com/</a>.

# Technical Support

If you purchased this product through a GE Fanuc Authorized Channel Partner, please contact them directly.

# General Contact Information

Online Technical Support and GlobalCare: http://www.gefanuc.com/support

Additional information: <a href="http://www.gefanuc.com/">http://www.gefanuc.com/</a>

# Technical Support

If you have technical problems that cannot be resolved with the information in this guide, please contact us by telephone or email, or on the web at <a href="http://www.gefanuc.com/support">http://www.gefanuc.com/support</a>.

# **Americas**

Online Technical Support: http://www.gefanuc.com/support

Phone: 1-800-GE FANUC (1-800-433-2682)

International Americas Direct Dial: 1-434-978-5100

Technical Support Email: <a href="mailto:support@gefanuc.com">mailto:support@gefanuc.com</a>

Customer Care Email: mailto:customer.care@gefanuc.com

Primary language of support: English

# Europe, the Middle East, and Africa

Online Technical Support: http://www.gefanuc.com/support

Phone: +800 1 GE FANUC (+800-1-433-2682)

Technical Support Email: mailto:support.emea@gefanuc.com

Customer Care Email: mailto:customercare.emea@gefanuc.com

Primary languages of support: English, French, German, Italian, Czech

#### Asia Pacific

Online Technical Support: http://www.gefanuc.com/support

Phone: +86-400-820-8208

+86-21-3217-4826 (India, Indonesia, and Pakistan)

Technical Support Email: <a href="mailto:support.cn@gefanuc.com">mailto:support.cn@gefanuc.com</a> (China)

mailto:support.jp@gefanuc.com (Japan)

mailto:support.in@gefanuc.com (remaining Asia customers)

Customer Care Email: mailto:customercare.apo@gefanuc.com

GFK-2222M Chapter 1 Introduction 1-9

# Chapter

# CPU Features and Specifications

2

This chapter provides details on the hardware features of the PACSystems CPUs and their specifications.

## Common CPU Features

# Firmware Storage in Flash Memory

The CPU uses non-volatile flash memory for storing the operating system firmware. This allows firmware to be updated without disassembling the module or replacing EPROMs. The operating system firmware is updated by connecting a PC compatible computer to the module's serial port and running the software included with the firmware upgrade kit.

# Operation, Protection, and Module Status

Operation of the CPU can be controlled by the three-position Run/Stop switch or remotely by an attached programmer and programming software. Program and configuration data can be locked through software passwords. The status of the CPU is indicated by the CPU LEDs on the front of the module. (On the RX7i CPUs, seven LEDs indicate the status of the Ethernet interface.) For details, see "Indicators" for each PACSystems family.

**Note:** The RESET pushbutton is provided to support future features and has no effect on CPU operation in the current version.

### Ethernet Global Data

Each PACSystems CPU supports up to 255 simultaneous EGD pages across all Ethernet interfaces in the PLC. EGD pages must be configured in the programming software and stored into the CPU. The EGD configuration can also be loaded from the CPU into the programming software. Both produced and consumed pages can be configured. PACSystems CPUs support the use of only part of a consumed EGD page, and EGD page production and consumption to the broadcast IP address of the local subnet.

The PACSystems CPU supports 2msec EGD page production and timeout resolution. EGD pages can be configured for a production period of 0, indicating the page is to be produced every output scan. The minimum period for these "as fast as possible" pages is 2msec.

During EGD configuration, PACSystems Ethernet interfaces are identified by their Rack/Slot location.

GFK-2222M 2-1

# RX7i Features and Specifications

# CPE010, CPE020 and CRE020 Models

- IC698CPE010: 300MHz CPU microprocessor

- IC698CPE020: 700MHz CPU microprocessor

- IC698CRE020: 700MHz CPU microprocessor with redundancy

For details on the operation of the embedded Ethernet interface, refer to page 2-8.

#### CPU Serial Ports

The CPU has three independent, on-board serial ports, accessed by connectors on the front of the module. Ports 1 and 2 provide serial interfaces to external devices. Port 1 or port 2 can be used for firmware upgrades. The third on-board serial port is used as the Ethernet Station Manager port. All serial ports are isolated. For serial port pin assignments and details on serial communications, refer to chapter 14.

#### CPU Indicators

Five CPU LEDs indicate the operating status of various CPU functions.

|    | LED State                             | ļ.                   | CPU Operating State                                                                                                                                                                                                                |

|----|---------------------------------------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| On | Blinking                              | OOff                 | , ,                                                                                                                                                                                                                                |

| •  | ОК                                    | On                   | CPU has passed its powerup diagnostics and is functioning properly.                                                                                                                                                                |

| 0  | ок                                    | Off                  | CPU problem. EN and RUN LEDs may be blinking in an error code pattern, which can be used by technical support for troubleshooting. This condition and any error codes should be reported to your technical support representative. |

| *  | OK, EN, RUI<br>Blinking in ur         |                      | CPU is in boot mode and is waiting for a firmware update through a serial port.                                                                                                                                                    |

| *  | OK Blin<br>Other LEDs                 | king<br>off.         | CPU in Stop/Halt state; possible watchdog timer fault. Refer to the fault tables. If the programmer cannot connect, cycle power with battery attached and refer to fault tables.                                                   |

| 0  | RUN                                   | On                   | CPU is in Run mode                                                                                                                                                                                                                 |

| O  | RUN                                   | Off                  | CPU is in Stop mode.                                                                                                                                                                                                               |

| 0  | EN                                    | On                   | Output scan is enabled.                                                                                                                                                                                                            |

| 0  | EN                                    | Off                  | Output scan is disabled.                                                                                                                                                                                                           |

| *  | <b>C1</b> (port 1) <b>C2</b> (port 2) | Blinking<br>Blinking | Signal activity on port.                                                                                                                                                                                                           |

# Specifications - CPE010, CPE020 and CRE020 Models

For environmental specifications, see "RX7i General Specifications" in Appendix A of the RX7i Installation Manual, GFK-2223.

| Battery Life: Memory retention                                       | For estimated battery life under various conditions, refer to page 2-4.                                                                                                                                                       |  |  |

|----------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Program storage                                                      | Up to 10 Mbytes of battery-backed RAM 10 Mbytes of non-volatile flash user memory                                                                                                                                             |  |  |

| Power requirements<br>CPE010                                         | +5 VDC: 3.2 Amps nominal<br>+12 VDC: 0.042 Amps nominal<br>-12 VDC: 0.008 Amps nominal                                                                                                                                        |  |  |

| CPE020, CRE020                                                       | +5 VDC: 4.5 Amps nominal<br>+12 VDC: 0.042 Amps nominal<br>-12 VDC: 0.008 Amps nominal                                                                                                                                        |  |  |

| Operating Temperature                                                | CPE010: 0 to 50°C (32°F to 122°F<br>0 to 60°C (32°F to 140°F) with fan tray                                                                                                                                                   |  |  |

|                                                                      | CPE020, CRE020: 0 to 60°C (32°F to 140°F), fan tray required                                                                                                                                                                  |  |  |

| Floating point                                                       | Yes                                                                                                                                                                                                                           |  |  |

| Boolean execution speed, typical<br>CPE010<br>CPE020, CRE020         | 0.195ms per 1000 Boolean instructions<br>0.14ms per 1000 Boolean instructions                                                                                                                                                 |  |  |

| Time of Day Clock accuracy                                           | Maximum drift of ±9 seconds per day.                                                                                                                                                                                          |  |  |

|                                                                      | Can be synchronized to an Ethernet time master within ±2ms of the SNTP time stamp.                                                                                                                                            |  |  |

| Elapsed Time Clock (internal timing) accuracy                        | ±0.01% maximum                                                                                                                                                                                                                |  |  |

| Embedded communications                                              | RS-232, RS-485, Ethernet interface                                                                                                                                                                                            |  |  |

| Serial Protocols supported                                           | Modbus RTU Slave, SNP, Serial I/O                                                                                                                                                                                             |  |  |

|                                                                      | To determine availability for a given firmware version, please refer to the <i>Important Product Information</i> document provided with the CPU.                                                                              |  |  |

| Ethernet Ports                                                       | Embedded auto-sensing 10/100 Mbps half/full duplex Ethernet interface                                                                                                                                                         |  |  |

| VME Compatibility                                                    | System designed to support the VME64 standard ANSI/VITA 1                                                                                                                                                                     |  |  |

| Program blocks                                                       | Up to 512 program blocks. Maximum size for a block is 128KB.                                                                                                                                                                  |  |  |

| Memory (For a detailed listing of memory areas, refer to chapter 7.) | %I and %Q: 32Kbits for discrete<br>%AI and %AQ: configurable up to 32Kwords<br>%W: configurable up to the maximum available user RAM<br>Managed memory (Symbolic and I/O variables combined): configurable<br>up to 10 Mbytes |  |  |

| Error Checking and Correction                                        | CRE020 only.                                                                                                                                                                                                                  |  |  |

| Ethernet Interface Specifications             |                                                    |

|-----------------------------------------------|----------------------------------------------------|

| Web-based data monitoring                     | Up to 16 web server and FTP connections (combined) |

| Ethernet data rate                            | 10Mb/sec and 100Mb/sec                             |

| Physical interface                            | 10BaseT RJ45                                       |

| WinLoader support                             | Yes                                                |

| Number of EGD configuration-based pages       | 255                                                |

| Time synchronization                          | SNTP                                               |

| Selective consumption of EGD                  | Yes                                                |

| Load EGD configuration from PLC to programmer | Yes                                                |

| Remote Station Manager over UDP               | Yes                                                |

| Local Station Manager (RS-232)                | Dedicated RS-232 port                              |

| Configurable Advanced User Parameters         | Yes                                                |

# Battery Life Estimates for CPE010 and CPE020/CRE020

To avoid loss of RAM memory contents, routine maintenance procedures should include scheduled replacement of the CPU's lithium battery pack, IC698ACC701. The following table lists estimates of battery life that can be used to develop a battery replacement schedule.

## Nominal IC698ACC701 Battery Pack Installed Life

| 0                                         | Nominal Life<br>with Applied Power ( |                  |                |

|-------------------------------------------|--------------------------------------|------------------|----------------|

| Controller                                | Average Temperature                  | 100% of the Time | 0% of the Time |

| IC698CPE010<br>IC698CPE020<br>IC698CRE020 | 20°C (68°F)                          | 5 years          | 40 days        |

The IC698ACC701 battery pack has a nominal shelf life of 5 years when stored at an average temperature of 20°C (68°F).

**Note:** An external Auxiliary Battery Module, IC693ACC302 can be used to provide long-term battery backup for any PACSystems CPU. For details, refer to the datasheet for the Auxiliary Battery Module, GFK-2124.

### Error Checking and Correction, IC698CRE020

Redundancy CPUs are shipped with error checking and correction (ECC) enabled. Enabling ECC results in slightly slower system performance, primarily during power-up, because it uses an extra 8 bits that must be initialized. If you upgrade the firmware on the non-redundancy CPU model IC698CPE020 to support redundancy, you must set the ECC jumper to the enabled state as described in the installation instructions provided with the upgrade kit.

The CRE020 performance measurements provided in appendix A were done with ECC enabled.

For details on ECC, refer to the *PACSystems Hot Standby CPU Redundancy User's Guide*, GFK-2308.

# CPE030/CRE030 and CPE040/CRE040 Models

- CPE030/CRE030: 600MHz Pentium-M microprocessor

- CPE040/CRE040: 1800MHz Pentium-M microprocessor

For details on the embedded Ethernet interface, refer to page 2-8.

# CPU Serial Ports

The CPU has three independent, isolated, on-board serial ports, accessed by connectors on the front of the module. Ports 1 and 2 provide serial interfaces to external devices and can be used for firmware upgrades. The third serial port is a dedicated Ethernet Station Manager port. For serial communications, see chapter 14.

### **CPU Indicators**

Seven CPU LEDs indicate CPU operating status.

|            | LED Ctata                               |      | 00110                                                                                                                                                                                                                                       |

|------------|-----------------------------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>O</b> O | LED State<br>n <b>∳</b> Blinking        | OOff | CPU Operating State                                                                                                                                                                                                                         |

| •          | CPU OK                                  | On   | CPU has passed its powerup diagnostics and is functioning properly.                                                                                                                                                                         |

| O          | СРИ ОК                                  | Off  | CPU problem. RUN and OUTPUTS ENABLED LEDs may be blinking in an error code pattern, which can be used by technical support for diagnostics. This condition and any error codes should be reported to your technical support representative. |

| *          | CPU OK, OUTS<br>RUN Blinkin<br>unison   |      | CPU is in boot mode and is waiting for a firmware update through a serial port.                                                                                                                                                             |

| 4          | OK Blinkir<br>Other LEDs off.           |      | CPU in Stop/Halt state; possible watchdog timer fault. Refer to the fault tables. If the programmer cannot connect, cycle power with battery attached and refer to fault tables.                                                            |

| 0          | RUN                                     | Off  | CPU is in Stop mode.                                                                                                                                                                                                                        |

| 0          | OUTS ENA                                | On   | Output scan is enabled.                                                                                                                                                                                                                     |

| 0          | OUTS ENA                                | Off  | Output scan is disabled.                                                                                                                                                                                                                    |

| 0          | I/O FORCE                               | On   | Override is active on a bit reference                                                                                                                                                                                                       |

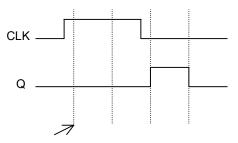

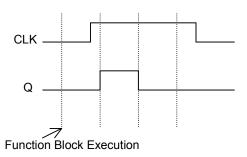

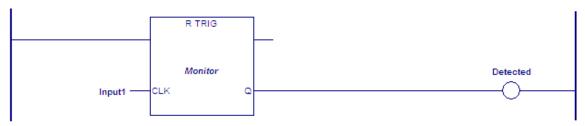

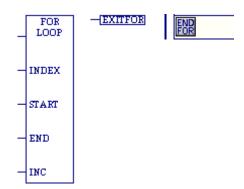

|            |                                         |      | (Not used by CRE030 and CRE040.)                                                                                                                                                                                                            |