# GFK-2122 New In Stock! GE Fanuc Manuals

http://www.pdfsupply.com/automation/ge-fanuc-manuals/series-90-70-9070/-GFK-2122

# series-90-70-9070 1-919-535-3180

Tundra Universe II Chip on IC697VSC096 Board

www.pdfsupply.com

Email:

sales@pdfsupply.com

# **GE Fanuc Automation**

Programmable Control Products

### GE Fanuc's Tundra Universe II™ Based VMEbus Interface

User's Manual

GFK-2122

514-000212-000

April 2002

#### GFL-002

### Warnings, Cautions, and Notes as Used in this Publication

#### Warning

Warning notices are used in this publication to emphasize that hazardous voltages, currents, temperatures, or other conditions that could cause personal injury exist in this equipment or may be associated with its use.

In situations where inattention could cause either personal injury or damage to equipment, a Warning notice is used.

Caution notices are used where equipment might be damaged if care is not taken.

#### Note

Notes merely call attention to information that is especially significant to understanding and operating the equipment.

This document is based on information available at the time of its publication. While efforts have been made to be accurate, the information contained herein does not purport to cover all details or variations in hardware or software, nor to provide for every possible contingency in connection with installation, operation, or maintenance. Features may be described herein which are not present in all hardware and software systems. GE Fanuc Automation assumes no obligation of notice to holders of this document with respect to changes subsequently made.

GE Fanuc Automation makes no representation or warranty, expressed, implied, or statutory with respect to, and assumes no responsibility for the accuracy, completeness, sufficiency, or usefulness of the information contained herein. No warranties of merchantability or fitness for purpose shall apply.

The following are trademarks of GE Fanuc Automation North America, Inc.

| Alarm Master      |

|-------------------|

| CIMPLICITY        |

| CIMPLICITY 90-ADS |

| CIMSTAR           |

| Field Control     |

| GEnet             |

Genius Helpmate Logicmaster Modelmaster Motion Mate ProLoop PROMACRO PowerMotion PowerTRAC Series 90 Series Five Series One

Series Six Series Three VersaMax VersaPro VuMaster Workmaster

©Copyright 2001 GE Fanuc Automation North America, Inc. All Rights Reserved

## Contents

| Chapter 1 | General Information                           | 1-1  |

|-----------|-----------------------------------------------|------|

|           | Reference Material and Other GE Fanuc Manuals | 1-1  |

|           | General Description                           | 1-2  |

|           | Programming the VMEbus Interface              | 1-3  |

|           | Tundra Corporation Reprinted Information      | 1-4  |

|           | Benefits of the Universe II                   | 1-5  |

|           | Past and Future of the Universe               | 1-7  |

| Chapter 2 | Functional Description                        | 2-1  |

|           | Architectural Overview                        | 2-1  |

|           | PCI-to-VMEbus Interface Jumpers               | 2-2  |

|           | Universe II Architectural Overview            |      |

|           | PCI Bus Interface                             |      |

|           | Universe as VMEbus Slave                      | 2-17 |

|           | PCI Bus Interface                             | 2-32 |

|           | Universe II as PCI Target                     | 2-39 |

|           | Slave Image Programming                       | 2-49 |

|           | Bus Error Handling                            | 2-57 |

|           | Interrupter                                   |      |

|           | Interrupt Handling                            |      |

|           | DMA Controller                                | 2-75 |

|           | Registers                                     | 2-96 |

|           | Universe II Registers                         | 2-98 |

|           | Utility Functions                             |      |

| Chapter 3 | Auxiliary Functions                           |      |

|           | Auxiliary Bus Timeout Timer                   |      |

|           | Auxiliary BERR Interrupt                      |      |

| Chapter 4 | Theory of Operation                           |      |

| •         | VMEbus Byte Lanes                             | 4-1  |

|           | Byte Ordering: Big Endian / Little Endian     |      |

|           | Endian Conversion Hardware                    |      |

|           | PCI Bus Data Combining: Byte Swap             |      |

| Chapter 5 | PCI/VMEbus Deadlock                           |      |

| -         | Scenario Overview                             | 5-1  |

| Chapter 6 | Universe II Errata and Notes                  | 6-1  |

| 1         | Introduction                                  | 6-1  |

|           |                                               |      |

### Contents

| Chapter 7  | Description of Signals                 | 7-1  |

|------------|----------------------------------------|------|

|            | Introduction                           |      |

| Chapter 8  | Signals and DC Characteristics         |      |

|            | Terminology                            |      |

|            | DC Characteristics and Pin Assignments |      |

| Appendix A | System Registers                       |      |

|            | Introduction                           | A-1  |

| Appendix B | Universe II Registers                  | B-1  |

| 11         | Introduction                           | B-1  |

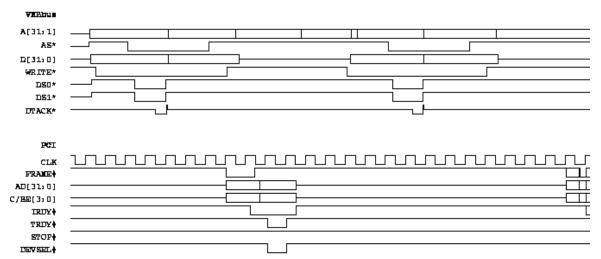

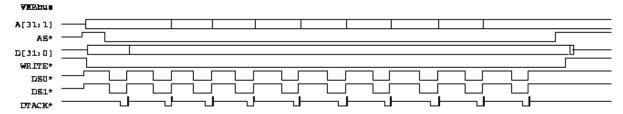

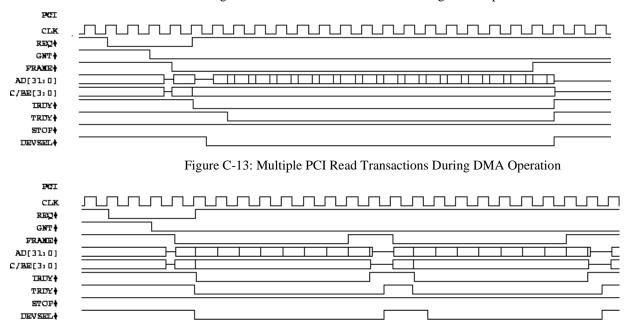

| Appendix C | Performance                            | C-1  |

|            | Introduction                           | C-1  |

|            | PCI Slave Channel                      | C-3  |

|            | VME Slave Channel                      | C-8  |

|            | DMA Channel                            | C-14 |

|            | Summary                                | C-17 |

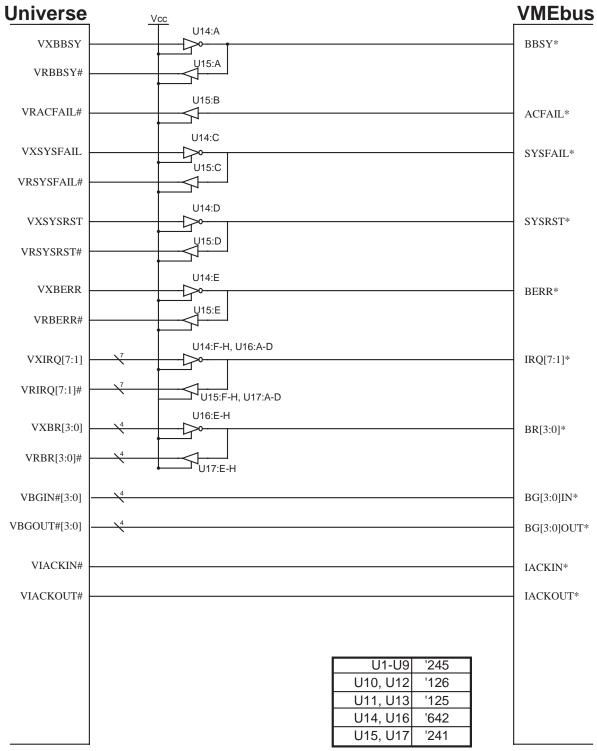

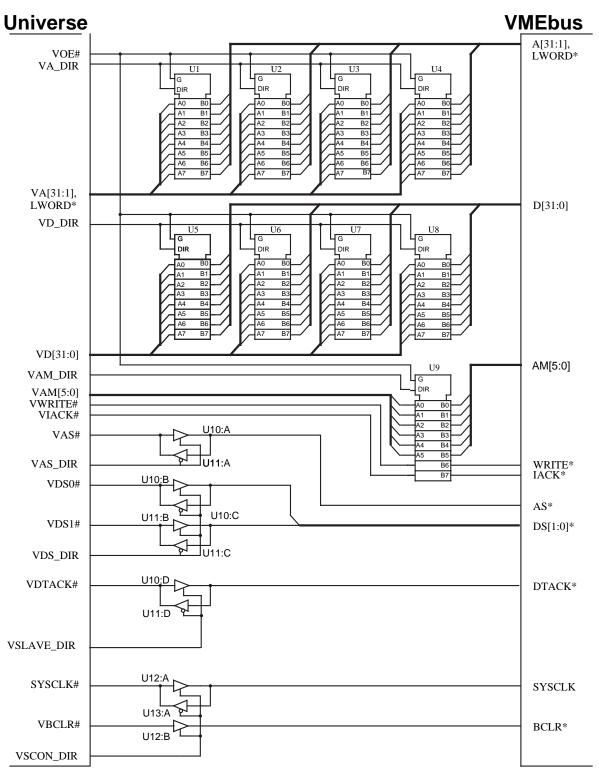

| Appendix D | Typical Applications                   | D-1  |

|            | VME Interface                          | D-1  |

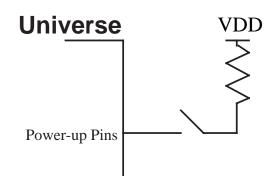

|            | PCI Bus Interface                      | D-8  |

|            | Manufacturing Test Pins                | D-11 |

| Appendix E | Reliability Prediction                 | E-1  |

|            | Introduction                           | E-1  |

|            | Physical Characteristics               | Е-2  |

| Appendix F | Cycle Mapping                          | F-1  |

|            | Introduction                           | F-1  |

|            | Little-endian Mode                     | F-2  |

| Appendix G | Operating and Storage Conditions       | G-1  |

|            | Introduction                           | G-1  |

Chapter ]

# Chapter | General Information

This manual describes the installation and operation of GE Fanuc's PCI-to-VMEbus interface that is built around the Tundra Universe II interface chip (CA91C142).

### Reference Material and Other GE Fanuc Manuals

For a detailed explanation of the VMEbus and its characteristics, "The VMEbus Specification" is available from:

VITA VMEbus International Trade Association 7825 East Gelding Dr., No. 104 Scottsdale, AZ 85260 (480) 951-8866 FAX: (480) 951-0720 Internet: www.vita.com

The following Application and Configuration Guides are available from GE Fanuc to assist in the selection, specification, and implementation of systems based upon GE Fanuc's products:

| Analog I/O Products (Built-in-Test)<br>Configuration Guide (catalog number<br>GFK-2084) | Provides assistance in configuring analog I/O<br>subsystems based on GE Fanuc's analog I/O<br>products, including common designs, which offer a<br>wide variety of solutions. |

|-----------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Connector and I/O Cable Application<br>Guide (catalog number GFK-2085)                  | Describes I/O connections that can be used with GE Fanuc's VMEbus products. Includes connector compatibility information and examples.                                        |

### General Description

The PCI-to-VMEbus interface is built around the Tundra Universe II interface chip (CA91C142) and provides the following features:

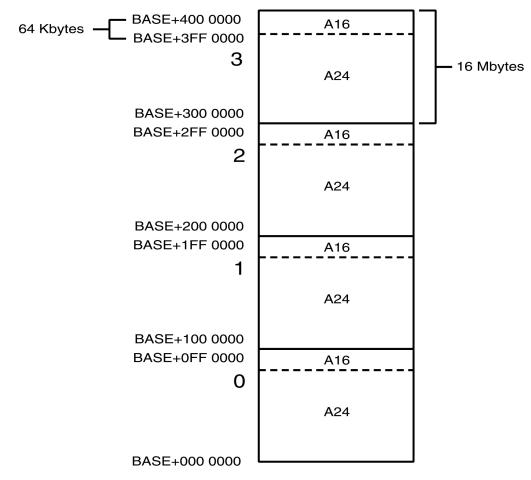

- 33 MHz PCI local bus interface with five separate PCI-to-VMEbus slave images (windows)

- High-performance 64-bit (multiplexed) VMEbus interface with four separate VMEbus-to-PCI slave images (windows)

- Programmable DMA controller with linked list support

- VMEbus system controller functionality

- Automatic slot 1 controller detection

- PCI and VMEbus interrupt generation

- VMEbus interrupt handler

- Communication support via four 32-bit mailbox registers with interrupt capabilities

- Real-time OS support with eight semaphores

- Master/Slave endian conversion hardware (Patent Pending)

- Non slot 1 bus timeout timer

- Auxiliary BERR VME address and Address Modifier capture with interrupt

Since the interface board is built around the Tundra Universe II chip, the majority of this documentation is extracted from the Universe II manual itself. However, there are features of the Universe II chip that are not supported at the board level, such as a 64-bit PCI interface, JTAG testability, and certain powerup options. These unsupported features are appropriately noted within the documentation.

In addition, auxiliary functionality has been added to provide various features such as master/slave endian conversion and a non slot 1 bus timeout timer.

### Programming the VMEbus Interface

The VMEbus Interface is configured by programming the auxiliary function global interrupt mask register, the external system registers, and the Universe II Control and Status Registers. In addition, the board has four jumpers which configure the board for generating/receiving VMEbus reset, asserting SYSFAIL on powerup, and mapping the Universe II registers in memory or I/O space. Refer to Chapter 2, *Functional Description*.

The base address of the various registers are located in either configuration space or memory and can be accessed using PCI BIOS calls, or GE Fanuc control function library software. Refer to Appendix A for a complete description of interface registers.

#### Note

In order to enable access to the VMEbus, both bits (11,10) must be set to high in the System COMM register located at \$D800E in memory.

### Tundra Corporation Reprinted Information

The information about the Tundra Universe II product is provided by Tundra Corporation and is reprinted here within with permission. This material is used extensively throughout this document. The only changes made to this text were made for section numbering purposes; GE Fanuc-specific information injected directly into the Tundra text is preceded by the GE Fanuc logo:

All of Chapter 2 is provided by Tundra except for the following GE Fanuc-generated sections: Architectural Overview of the VMEbus Interface on page 41, PCI-to-VMEbus Interface Jumpers on page 43, Linked-List Operation on page 131, FIFO Operation and Bus Ownership on page 137.

Chapters 3, 4, 5, and 6, are exclusively GE Fanuc.

Appendix A contains the following GE Fanuc information:

- The auxiliary function global interrupt mask register,

- The system register section, and

- The mailbox register section

The Universe Control and Status Register material in Appendix B is a direct reprint of the Tundraprovided information.

Appendixes B through G are reprinted information from Tundra.

### Benefits of the Universe II

Interfacing the VMEbus with PCI presents a number of opportunities and challenges. The Universe II solves the problems and allows you to benefit from the opportunities.

The opportunities involve merging the best of the VMEbus and PCI bus worlds. The VMEbus is a proven standard specifically designed to support embedded systems. The distributed environment of the VMEbus supports multiprocessing and real-time intensive applications. A large number of off-the-shelf boards, software, and chassis components are available. VMEbus supports 21-slot systems without bridging, and is continually evolving while providing backward compatibility. Hot swap solutions and higher performance protocols have been defined and will be incorporated in future revisions of VMEbus.

Meanwhile, PCI has become a standard local bus. As a result, the leading semiconductor vendors have built PCI support into their newest processor and peripheral families.

The challenges involved in interfacing VMEbus to PCI include: address mapping, byte-lane swapping, and cycle mapping.

To allow VMEbus single-board computer vendors to benefit from PCI components, while overcoming the challenges involved in merging PCI with VMEbus, Tundra has developed a PCI-to-VMEbus interface controller, the Universe II. The Universe II is the industry-proven, high-performance 64-bit VMEbus-to-PCI interface, fully compliant with VME64 and tailored for the new generation of high performance PCI processors and peripherals.

The availability of the Universe II eases the development of multimaster, multiprocessor architectures on VMEbus systems using PCI. The Universe II is ideally suited for CPU boards acting as both master and slave in the VMEbus system and that require access to PCI systems. With the Universe II, you know that as your system increases in complexity, you have silicon that continues to provide everything you need in a bridge. The elegant design of the Tundra Universe II, some of the best applications engineers in the industry, and this manual will make it as easy as possible for you to use the most sophisticated VMEbus interface.

### Features

The Universe II (CA91C142) is the *de facto* industry-standard PCI bus-to-VMEbus bridge, providing:

- 64-bit, 33 MHz PCI bus interface

- fully compliant, high-performance 64-bit VMEbus interface

- integral FIFOs buffer multiple transactions in both directions

- programmable DMA controller with linked-list support

- industry leading performance

- wide range of VMEbus address and data transfer modes

- A32/A24/A16 master and slave, (not A64 or A40)

- D64/D32/D16/D08 master and slave, (no MD32)

- MBLT, BLT, ADOH, RMW, LOCK, location monitors

- nine user-programmable slave images on VMEbus and PCI bus ports

- seven interrupt lines on either bus and flexible mapping of software and hardware sources of hardware interrupt

- automatic initialization for slave-only applications

- flexible register set, programmable from both the VMEbus and the PCI bus

- four mailboxes and location monitor for message-oriented system

- support for RMWs, lock cycles, and semaphores guarantee exclusive access

- bus isolation mode for board maintenance, diagnostics, and live fault recovery

- full VMEbus system controller functionality

- several powerup options

- IEEE 1149.1 JTAG testability support

- commercial (0° to 70° C), industrial (-40° to 85° C) and extended temperature (-55° to 125°C) options

- available in 313-pin Plastic BGA and 324-pin Ceramic BGA.

### Past and Future of the Universe

The Universe II (CA91C142) is a pin and software-compatible revision of the Universe (CA91C042). The Universe was developed subsequently to the SCV64, Tundra's VME interface for non-PCI applications. The Universe II is the next generation of the Universe, and has been designed to exceed new customer expectations and to correct errata in the original Universe. The rich set of feature and performance enhancements are based on extensive consultation with our customers.

The Universe II offers a low-risk, feature-rich, high-performance solution for VMEbus-based PCI applications. Some of the performance enhancements offered by the Universe II include:

- improved PCI bus bandwidth utilization

- improved register access performance

- improved VMEbus slave and VME master performance

- increased FIFO depth

- DMA improved to optimize transfer rate on each bus

- improved linked-list DMA performance

- significantly improved coupled transfer performance

- reduced power consumption

Additional features include:

- four mailbox registers

- eight semaphores

- four location monitors

- new software interrupts

- more slave images

The Universe II revision is another example of Tundra's commitment to supporting the VMEbus community. Tundra is actively participating in VMEbus, PCI bus, and Compact PCI bus standards and vendor associations, as well as related SIGs. Tundra will continue to propose and support enhancements to these specifications, while increasing both the range of options available to our customers and the compatibility between VME and PCI. Please visit our web site at www.tundra.com to keep abreast of these developments.

Chapter 2

## Functional Description

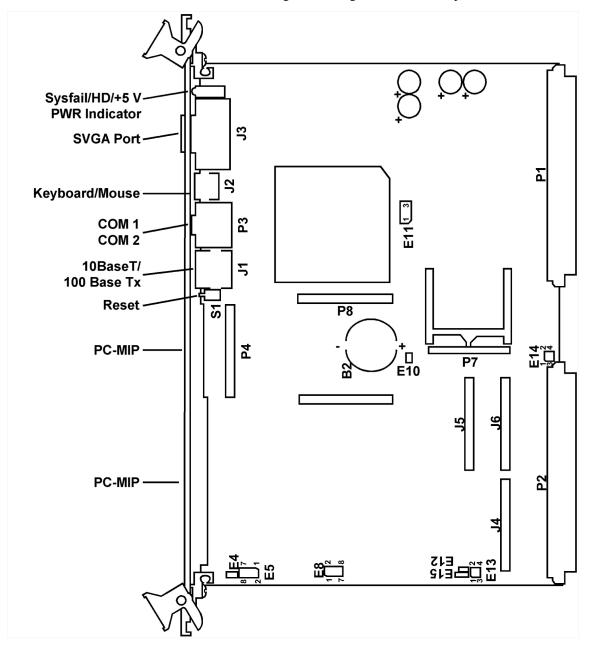

### Architectural Overview

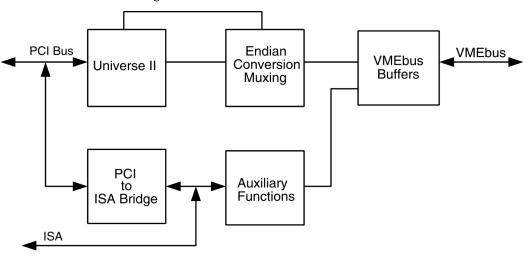

The VMEbus Interface consists of a Universe II chip, endian conversion muxing hardware, and miscellaneous auxiliary functions hardware. These components are graphically illustrated in Figure 2-1. The majority of the interface functionality including the basic PCI-to-VMEbus interface, DMA controller functionality, and VMEbus system controller functionality, is provided by the Universe II chip. The auxiliary functions hardware provides the system registers, the endian conversion control logic, the non-slot 1 bus timeout timer, the VME BERR address capture and interrupt logic, as well as various other miscellaneous logic.

### PCI-to-VMEbus Interface Jumpers

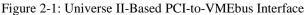

The VMEbus Interface is tested for system operation and shipped with factory-installed header jumpers. The interface is shipped with the VME board as part of the VMEbus Interface. Figure 2-2 illustrates the physical location of the user-configurable jumpers. Table 2-1 lists each jumper designator, its function, and the factory-installed default configuration.

Figure 2-2: Edge View of the Jumper Locations

| Jumper | Function                                                            | Factory Setting                   |

|--------|---------------------------------------------------------------------|-----------------------------------|

| E100   | Installed - SYSFAIL not asserted upon reset                         | Installed                         |

|        | Removed - SYSFAIL asserted upon reset                               |                                   |

| E101   | Installed - Universe memory mapped<br>Removed - Universe I/O mapped | Installed (Should not be removed) |

| E102   | Installed - Drives VMEbus SYSRESET<br>Removed - Does not drive      | Installed                         |

| E103   | Installed - Receives VMEbus SYSRESET<br>Removed - Does not receive  | Installed                         |

Table 2-1: VMEbus Interface Jumper Functions and Factory Settings

Please refer to the VMEbus Interface Volume I manual for other jumper settings.

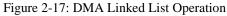

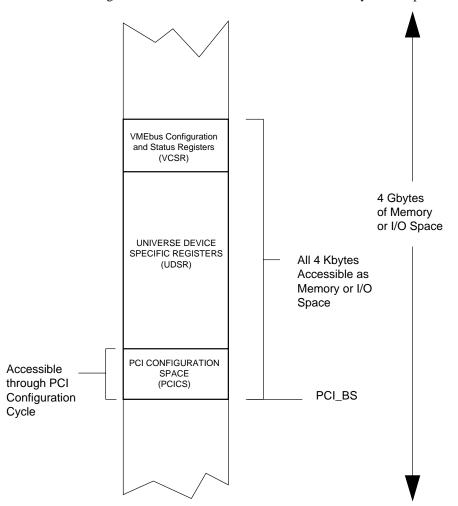

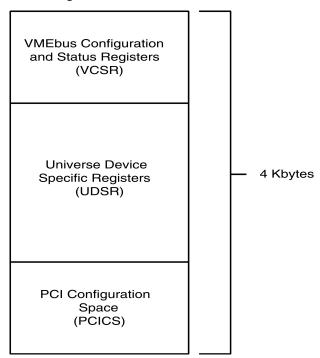

The Universe II chip maps the 4K register set in both I/O and memory space each with 4 Kbyte resolution. The registers may thus be accessed using either mode. However, in order to maintain compatibility with existing software, memory space access should be used. The address of the registers are contained in the Universe II's configuration space base address registers 0 and 1 (for example, config space offset 0x10 and 0x14).

### Universe II Architectural Overview

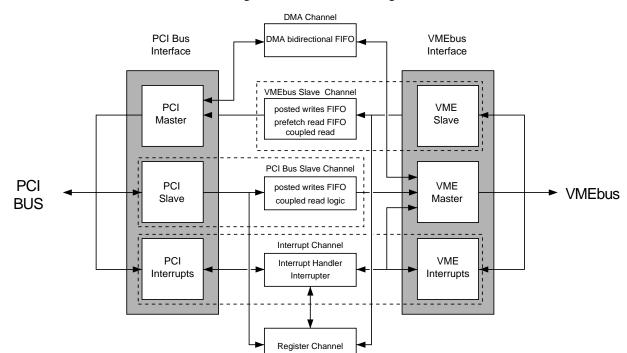

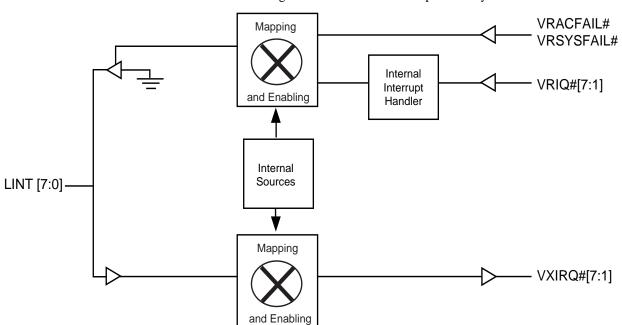

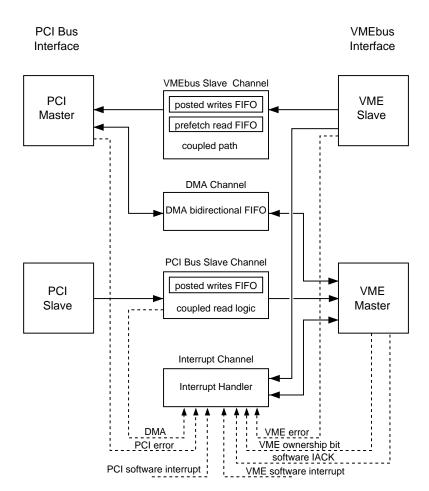

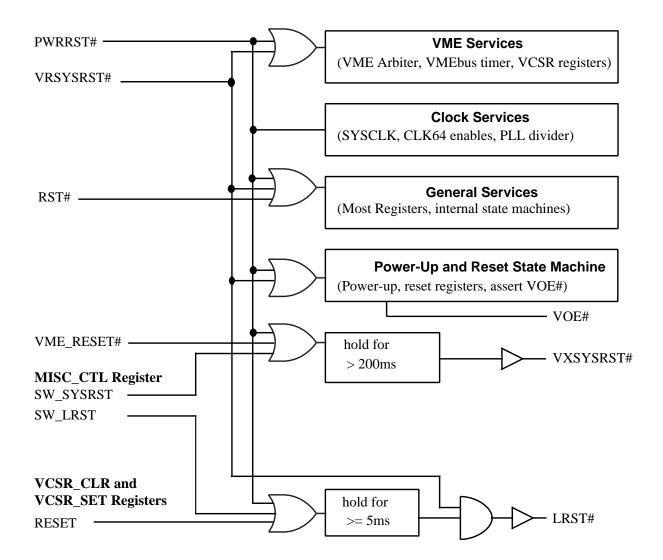

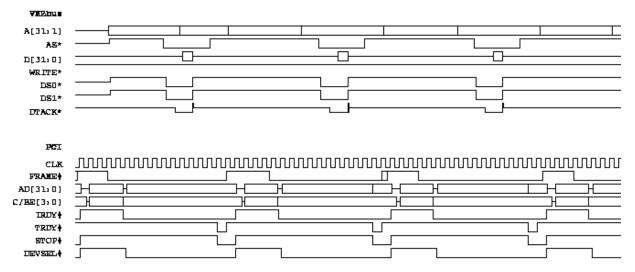

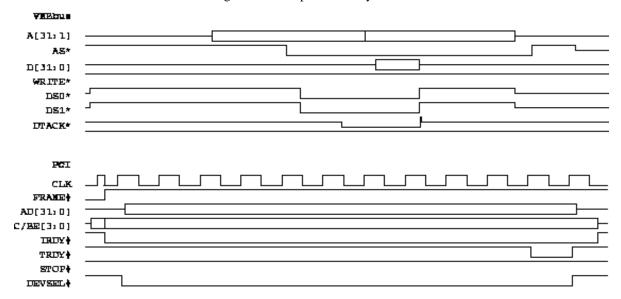

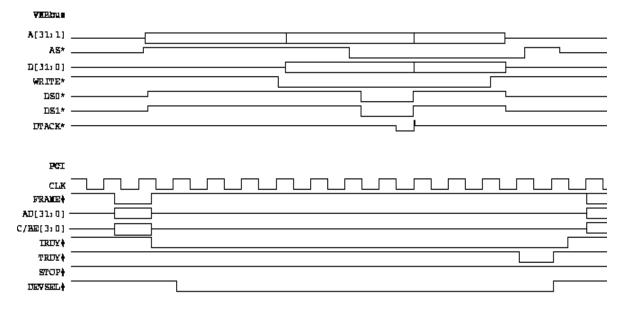

This section introduces the general architecture of the Universe II. This description makes frequent reference to the functional block diagram provided in Figure 2-3. Notice that for each of the interfaces, VMEbus and PCI bus, there are three functionally distinct modules: master module, slave module, and interrupt module. These modules are connected to the different functional channels operating in the Universe II. These channels are:

- VMEbus Slave Channel

- PCI bus Target Channel

- DMA Channel

- Interrupt Channel

- Register Channel

The Architectural Overview is organized into the following sections:

- VMEbus Interface

- PCI Bus Interface

- Interrupter and Interrupt Handler

- DMA Controller

These sections describe the operation of the Universe II in terms of the different modules and channels illustrated in Figure 2-3.

### **VMEbus** Interface

#### Universe II as VMEbus Slave

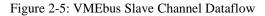

The Universe II VMEbus Slave Channel accepts all of the addressing and data transfer modes documented in the VME64 specification (except A64 and those intended to augment 3U applications, for example, A40 and MD32). Incoming write transactions from the VMEbus may be treated as either coupled or posted, depending upon the programming of the VMEbus slave image (see "VME Slave Images" on page 2-49). With posted write transactions, data is written to a Posted Write Receive FIFO (RXFIFO), and the VMEbus master receives data acknowledgment from the Universe II. Write data is transferred to the PCI resource from the RXFIFO without the involvement of the initiating VMEbus master (see "Posted Writes" on page 2-18 for a full explanation of this operation). With a coupled cycle, the VMEbus master only receives data acknowledgment when the transaction is complete on the PCI bus. This means that the VMEbus is unavailable to other masters while the PCI bus transaction is executed.

Read transactions may be either prefetched or coupled. If enabled by the user, a prefetched read is initiated when a VMEbus master requests a block read transaction (BLT or MBLT) and this mode is enabled. When the Universe II receives the block read request, it begins to fill its Read Data FIFO (RDFIFO) using burst transactions from the PCI resource. The initiating VMEbus master then acquires its block read data from the RDFIFO rather than from the PCI resources directly.

Figure 2-3: Architectural Diagram for the Universe II

### **Universe II as VMEbus Master**

The Universe II becomes VMEbus master when the VMEbus Master Interface is internally requested by the PCI Bus Target Channel, the DMA Channel, or the Interrupt Channel. The Interrupt Channel always has priority over the other two channels. Several mechanisms are available to configure the relative priority that the PCI Bus Target Channel and DMA Channel have over ownership of the VMEbus Master Interface.

The Universe II's VMEbus Master Interface generates all of the addressing and data transfer modes documented in the VME64 specification (except A64 and those intended to augment 3U applications, for example, A40 and MD32). The Universe II is also compatible with all VMEbus modules conforming to pre-VME64 specifications. As VMEbus master, the Universe II supports Read-Modify-Write (RMW), and Address-Only-with-Handshake (ADOH) but does not accept RETRY\* as a termination from the VMEbus slave. The ADOH cycle is used to implement the VMEbus Lock command allowing a PCI master to lock VMEbus resources.

### PCI Bus Interface

#### Universe II as PCI Target

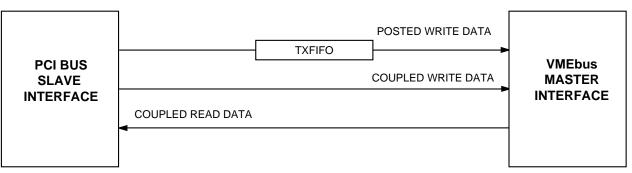

Read transactions from the PCI bus are always processed as coupled. Write transactions may be either coupled or posted, depending upon the setting of the PCI bus target image (see "PCI Bus Target Images" on page 2-52). With a posted write transaction, write data is written to a Posted Write Transmit FIFO (TXFIFO) and the PCI bus master receives data acknowledgment from the Universe II with zero wait-states. Meanwhile, the Universe II obtains the VMEbus and writes the data to the VMEbus resource independent of the initiating PCI master (see "Posted Writes" on page 2-18 for a full description of this operation).

To allow PCI masters to perform RMW and ADOH cycles, the Universe II provides a Special Cycle Generator. The Special Cycle Generator can be used in combination with a VMEbus ownership function to guarantee PCI masters exclusive access to VMEbus resources over several VMEbus transactions (see "The Special Cycle Generator" on page 2-44 and "Using the VOWN bit" on page 2-47 for a full description of this functionality).

#### Universe II as PCI Master

The Universe II becomes PCI master when the PCI Master Interface is internally requested by the VMEbus Slave Channel or the DMA Channel. There are mechanisms provided which allow the user to configure the relative priority of the VMEbus Slave Channel and the DMA Channel.

### Interrupter and Interrupt Handler

#### Interrupter

The Universe II Interrupt Channel provides a flexible scheme to map interrupts to the PCI bus or VMEbus Interface. Interrupts are generated from hardware or software sources (see "Interrupt Generation" on page 2-60 and "Interrupt Handling" on page 2-67 for a full description of hardware and software sources). Interrupt sources can be mapped to any of the PCI bus or VMEbus interrupt output pins. Interrupt sources mapped to VMEbus interrupts are generated on the VMEbus interrupt output pins VIRQ# [7:1]. When a software and hardware source are assigned to the same VIRQn# pin, the software source always has higher priority.

Interrupt sources mapped to PCI bus interrupts are generated on one of the INT# [7:0] pins. To be fully PCI compliant, all interrupt sources must be routed to a single INT# pin.

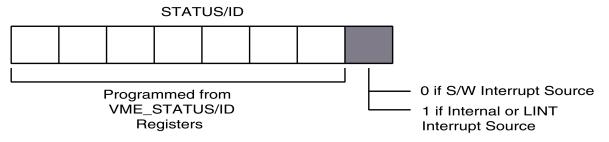

For VMEbus interrupt outputs, the Universe II interrupter supplies an 8-bit STATUS/ID to a VMEbus interrupt handler during the IACK cycle, and optionally generates an internal interrupt to signal that the interrupt vector has been provided (see "VMEbus Interrupt Generation" on page 2-64).

Interrupts mapped to PCI bus outputs are serviced by the PCI interrupt controller. The CPU determines which interrupt sources are active by reading an interrupt status register in the Universe II. The source negates its interrupt when it has been serviced by the CPU (see "PCI Interrupt Generation" on page 2-61).

#### VMEbus Interrupt Handling

A VMEbus interrupt triggers the Universe II to generate a normal VMEbus IACK cycle and generate the specified interrupt output. When the IACK cycle is complete, the Universe II releases the VMEbus and the interrupt vector is read by the PCI resource servicing the interrupt output. Software interrupts are ROAK, while hardware and internal interrupts are RORA.

#### **DMA Controller**

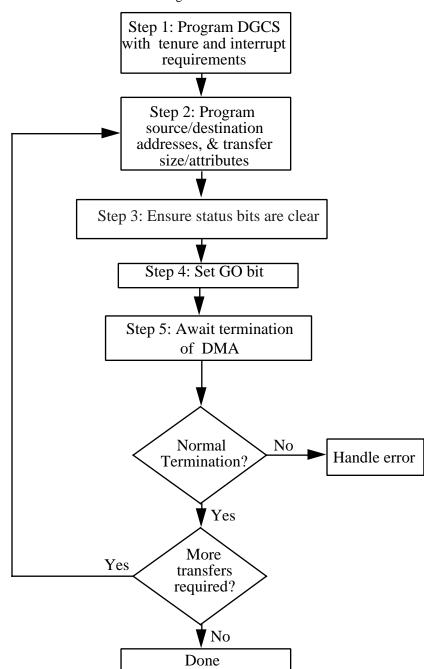

The Universe II provides an internal DMA controller for high performance data transfer between the PCI and VMEbus. DMA operations between the source and destination bus are decoupled through the use of a single bidirectional FIFO (DMAFIFO). Parameters for the DMA transfer are software configurable in the Universe II registers (see "DMA Controller" on page 2-75).

The principal mechanism for DMA transfers is the same for operations in either direction (PCI-to-VMEbus, or VMEbus-to-PCI), only the relative identity of the source and destination bus changes. In a DMA transfer, the Universe II gains control of the source bus and reads data into its DMAFIFO. Following specific rules of DMAFIFO operation (see "FIFO Operation and Bus Ownership" on page 2-89), it then acquires the destination bus and writes data from its DMAFIFO.

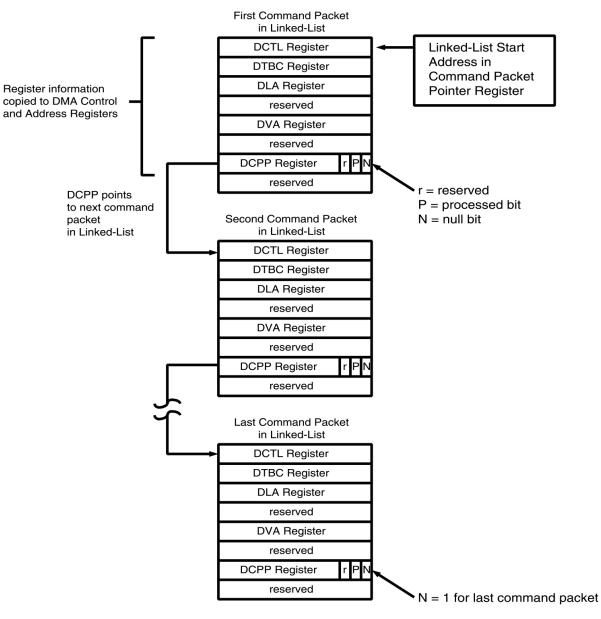

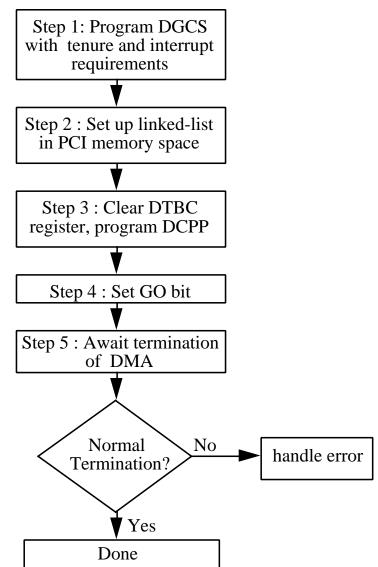

The DMA controller can be programmed to perform multiple blocks of transfers using entries in a linked-list. The DMA will work through the transfers in the linked-list following pointers at the end of each linked-list entry. Linked-list operation is initiated through a pointer in an internal Universe II register, but the linked-list itself resides in PCI bus memory.

### **VMEbus** Interface

The VMEbus Interface incorporates all operations associated with the VMEbus. This includes master and slave functions, VMEbus configuration and system controller functions. These operations are covered as follows:

- VMEbus Requester, page 2-10

- Universe II as VMEbus Master, page 2-12

- Universe as VMEbus Slave, page 2-17

- VMEbus Configuration, page 2-25

- Automatic Slot Identification, page 2-26

- System Controller Functions, page 2-28

- BI-Mode, page 2-30. For information concerning the Universe II VMEbus slave images, see "VME Slave Images".

### **VMEbus Requester**

#### Internal Arbitration for VMEbus Requests

Three different internal channels within the Universe II require use of the VMEbus: the Interrupt Channel, the PCI Target Channel, and the DMA Channel. These three channels do not directly request the VMEbus, instead they compete internally for ownership of the VMEbus Master Interface.

The Interrupt Channel (refer to Figure 2-3) always has the highest priority for access to the VMEbus Master Interface. The DMA and PCI Target Channel requests are handled in a fair manner. The channel awarded VMEbus mastership maintains ownership of the VMEbus until it is 'done'. The definition of 'done' for each channel is given on page 2-11 in "VMEbus Release".

The Interrupt Channel requests the VMEbus master when it detects an enabled VMEbus interrupt line asserted and needs to run an interrupt acknowledge cycle to acquire the STATUS/ID.

The PCI Target Channel requests the VMEbus Master Interface to service the following conditions:

- the TXFIFO contains a complete transaction, or

- if there is a coupled cycle request.

The DMA Channel requests the VMEbus Master Interface if:

- the DMAFIFO has 64 bytes available (if it is reading from the VMEbus) or 64 bytes in its FIFO (if it is writing to the VMEbus), or

- the DMA block is complete (see "DMA Controller" on page 2-75).

In the case of the DMA Channel, the user can optionally use the DMA Channel VMEbus-off-timer to further qualify requests from this channel. The VMEbus-off-timer controls how long the DMA remains off the VMEbus before making another request (see "PCI-to-VMEbus Transfers" on page 2-89).

The Universe II provides a software mechanism for VMEbus acquisition through the VMEbus ownership bit (VOWN in the MAST\_CTL register, Table B-160). When the VMEbus ownership bit is set, the Universe II acquires the VMEbus and sets an acknowledgment bit (VOWN\_ACK in the MAST\_CTL register, Table B-160) and optionally generates an interrupt to the PCI bus (see "VME Lock Cycles—Exclusive Access to VMEbus Resources" on page 2-46). The Universe II maintains VMEbus ownership bit is cleared. During the VMEbus tenure initiated by setting the ownership bit, only the PCI Target Channel and Interrupt Channel can access the VMEbus Master Interface.

### **Request Modes**

#### **Request Levels**

The Universe II is software configurable to request on all VMEbus request levels: BR3\*, BR2\*, BR1\*, and BR0\*. The default setting is for level 3 VMEbus request. The request level is a global programming option set through the VRL field in the MAST\_CTL register (Table B-160). The programmed request level is used by the VMEbus Master Interface regardless of the channel (Interrupt Channel, DMA Channel, or PCI Target Channel) currently accessing the VMEbus Master Interface.

#### Fair and Demand

The Universe II requester may be programmed for either Fair or Demand mode. The request mode is a global programming option set through the VRM bits in the MAST\_CTL register (Table B-160).

In Fair mode, the Universe II does not request the VMEbus until there are no other VMEbus requests pending at its programmed level. This mode ensures that every requester on an equal level has access to the bus.

In Demand mode (the default setting), the requester asserts its bus request regardless of the state of the BRn\* line. By requesting the bus frequently, requesters far down the daisy chain may be prevented from ever obtaining bus ownership. This is referred to as "starving" those requesters. Note that in order to achieve fairness, all bus requesters in a VMEbus system must be set to Fair mode.

#### **VMEbus Release**

The Universe II VMEbus requester can be configured as either RWD (release when done) or ROR (release on request) using the VREL bit in the MAST\_CTL register (Table B-160). The default setting is for RWD. ROR means the Universe II releases BBSY\* only if a bus request is pending from another VMEbus master and once the channel that is the current owner of the VMEbus Master Interface is done. Ownership of the bus may be assumed by another channel without rearbitration on the bus if there are no pending requests on any level on the VMEbus. When set for RWD, the VMEbus Master Interface releases BBSY\* when the channel accessing the VMEbus Master Interface is done. Note that the MYBBSY status bit in the MISC\_STAT register (Table B-164) is set while the Universe II asserts the BBSY\* output.

In RWD mode, the VMEbus is released when the channel (for example, the DMA Channel) is done, even if another channel has a request pending (for example, the PCI Target Channel). A rearbitration of the VMEbus is required for any pending channel requests. Each channel has a set of rules that determine when it is 'done' with its VMEbus transaction.

The Interrupt Channel is done when a single interrupt acknowledge cycle is complete.

The PCI Target Channel is done under the following conditions:

- when the TXFIFO is empty (the TXFE bit is set by the Universe II in the MISC\_STAT register, Table B-164 ),

- when the maximum number of bytes per PCI Target Channel tenure has been reached (as programmed with the PWON field in the MAST\_CTL register, Table B-160),

- after each posted write, if the PWON is equal to 0b1111, as programmed in the MAST\_CTL register, Table B-160

- when the coupled cycle is complete and the Coupled Window Timer has expired,

- if the Coupled Request Timer expires before a coupled cycle is retried by a PCI master, or

- when VMEbus ownership is acquired with the VOWN bit in the MAST\_CTL register and then the VOWN bit is cleared (in other words, if the VMEbus is acquired through the use of the VOWN bit, the Universe II does not release BBSY\* until the VOWN bit is cleared—see "VME Lock Cycles—Exclusive Access to VMEbus Resources" on page 2-46).

The DMA Channel is done under the following conditions (see "FIFO Operation and Bus Ownership" on page 2-89 and "DMA Error Handling" on page 2-93):

- DMAFIFO full during VMEbus-to-PCI bus transfers,

- DMAFIFO empty during PCI bus to VMEbus transfers,

- if an error is encountered during the DMA operation,

- the DMA VMEbus Tenure Byte Counter has expired, or

- DMA block is complete.

The Universe II does not monitor BCLR\* and so its ownership of the VMEbus is not affected by the assertion of BCLR\*.

### Universe II as VMEbus Master

The Universe II becomes VMEbus master as a result of the following chain of events:

- 1. a PCI master accesses a Universe II PCI target image (leading to VMEbus access) or the DMA Channel initiates a transaction,

- 2. either the Universe II PCI Target Channel or the DMA Channel wins access to the VMEbus Master Interface through internal arbitration, and

- 3. the Universe II Master Interface requests and obtains ownership of the VMEbus.

The Universe II will also become VMEbus master if the VMEbus ownership bit is set (see "VME Lock Cycles—Exclusive Access to VMEbus Resources" on page 2-46) and in its role in VMEbus interrupt handling (see "VMEbus Interrupt Handling" on page 2-68).

The following sections describe the function of the Universe II as a VMEbus master in terms of the different phases of a VMEbus transaction: addressing, data transfer, cycle termination, and bus release.

The Universe I chip is unable to perform a 64-bit (double type) floating point operation on a read from VMEbus address, e.g., T=\*Vme and T=T+1.0. This problem does not occur with the Universe II chip. However, to maintain backward compatibility, use two operations.

#### Addressing Capabilities

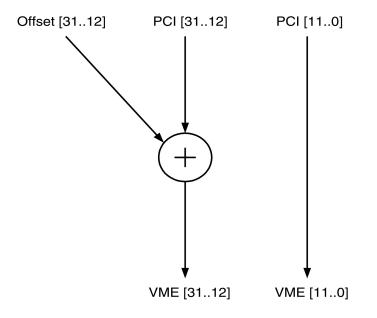

Depending upon the programming of the PCI target image (see "PCI Bus Target Images" on page 2-52), the Universe II generates A16, A24, A32, and CR/CSR address phases on the VMEbus. The address mode and type (supervisor/non-privileged and program/data) are also programmed through the PCI target image. Address pipelining is provided except during MBLT cycles, where the VMEbus specification does not permit it.

The address and AM codes that are generated by the Universe II are functions of the PCI address and PCI target image programming (see "PCI Bus Target Images" on page 2-52) or through DMA programming.

The Universe II generates Address-Only-with-Handshake (ADOH) cycles in support of lock commands for A16, A24, and A32 spaces. ADOH cycles must be generated through the Special Cycle Generator (see "The Special Cycle Generator" on page 2-44).

There are two User Defined AM codes that can be programmed through the USER\_AM register (Table B-166). The USER\_AM register can only be used to generate and accept AM codes 0x10 through 0x1F. These AM codes are designated as USERAM codes in the VMEbus specification. After power-up, the two values in the USER\_AM register default to the same VME64 user-defined AM code.

If USER\_AM codes are used with the VMEbus Slave Interface, ensure that the cycles use 32-bit addressing, and that only single cycle accesses are used. BLTs and MBLTs with USER\_AM codes will lead to unpredictable behavior.

#### **Data Transfer Capabilities**

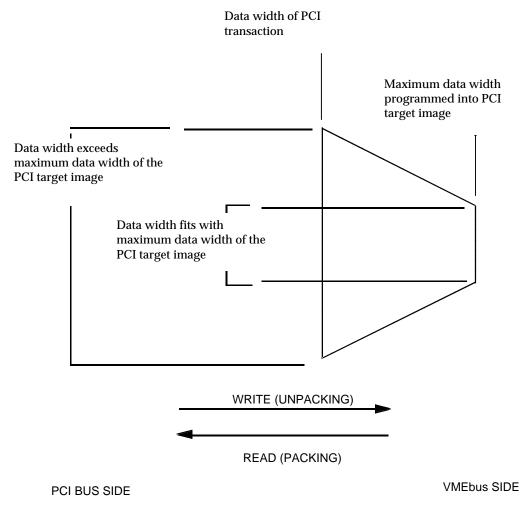

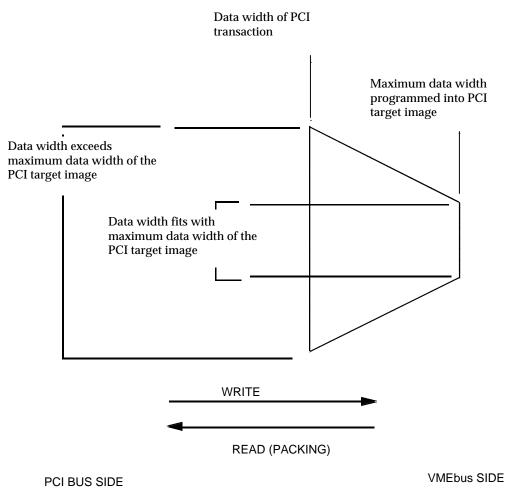

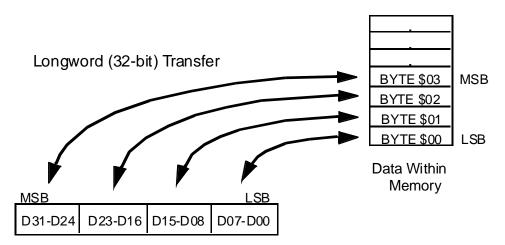

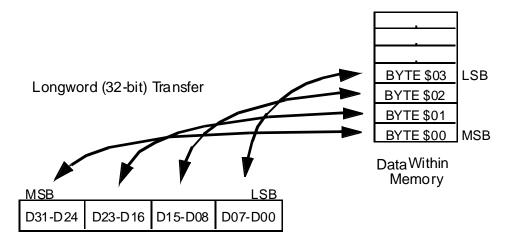

The data transfer between the PCI bus and VMEbus is depicted in Figure 2-4. The Universe II can be seen as a funnel where the mouth of the funnel is the data width of the PCI transaction. The end of the funnel is the maximum VMEbus data width programmed into the PCI target image. For example, consider a 32-bit PCI transaction accessing a PCI target image with VDW set to 16 bits. A data beat with all byte lanes enabled will be broken into two 16-bit cycles on the VMEbus. If the PCI target image is also programmed with block transfers enabled, the 32-bit PCI data beat will result in a D16 block transfer on the VMEbus. Write data is unpacked to the VMEbus and read data is packed to the PCI bus data width.

If the data width of the PCI data beat is the same as the maximum data width of the PCI target image, then the Universe II maps the data beat to an equivalent VMEbus cycle. For example, consider a 32-bit PCI transaction accessing a PCI target image with VDW set to 32 bits. A data beat with all byte lanes enabled is translated to a single 32-bit cycle on the VMEbus.

As the general rule, if the PCI bus data width is less than the VMEbus data width then there is no packing or unpacking between the two buses. The only exception to this is during 32-bit PCI multidata beat transactions to a PCI target image programmed with maximum VMEbus data width of 64 bits. In this case, packing/unpacking occurs to make maximum use of the full bandwidth on both buses. Only aligned VMEbus transactions are generated, so if the requested PCI data beat has unaligned or non-contiguous byte enables, then it is broken into multiple aligned VMEbus transactions no wider than the programmed VMEbus data width. For example, consider a three-byte PCI data beat (on a 32-bit PCI bus) accessing a PCI target image with VDW set to 16 bits. The three-byte PCI data beat will be broken into two aligned VMEbus cycles: a single-byte cycle and a double-byte cycle (the ordering of the two cycles depends on the arrangement of the byte enables in the PCI data beat). If in the above example the PCI target image has a VDW set to 8 bits, then the three-byte PCI data beat will be broken into three single-byte VMEbus cycles.

BLT/MBLT cycles are initiated on the VMEbus if the PCI target image has been programmed with this capacity (see "PCI Bus Target Images" on page 2-52). The length of the BLT/MBLT transactions on the VMEbus will be determined by the initiating PCI transaction or the setting of the PWON field in the MAST\_CTL register (Table B-160). For example, a single data beat PCI transaction queued in the TXFIFO results in a single data beat block transfer on the VMEbus. With the PWON field, the user can specify a transfer byte count that will be dequeued from the TXFIFO before the VMEbus Master Interface relinquishes the VMEbus. The PWON field specifies the minimum tenure of the Universe II on the VMEbus. However, tenure is extended if the VOWN bit in the MAST\_CTL register is set (see "Using the VOWN bit" on page 2-47).

During DMA operations, the Universe II will attempt block transfers to the maximum length permitted by the VMEbus specification (256 bytes for BLT, 2 Kbytes for MBLT) and as limited by the VON counter (see "DMA VMEbus Ownership" on page 2-79).

The Universe II provides indivisible transactions with the VMEbus lock commands and the VMEbus ownership bit (see "VME Lock Cycles—Exclusive Access to VMEbus Resources" on page 2-46).

Figure 2-4: Influence of Data Width and Target Image Data Width on Data Packing/Unpacking

2

The Universe II accepts BERR\* or DTACK\* as cycle terminations from the VMEbus slave. It does not support RETRY\*. The assertion of BERR\* indicates that some type of system error occurred and the transaction did not complete properly. A VMEbus BERR\* received by the Universe II during a coupled transaction is communicated to the PCI master as a Target-Abort. No information is logged if the Universe II receives BERR\* in a coupled transaction. If an error occurs during a posted write to the VMEbus, the Universe II uses the V\_AMERR register (Table B-212) to log the AM code of the transaction (AMERR [5:0]), and the state of the IACK\* signal (IACK bit, to indicate whether the error occurred during an IACK cycle). The current transaction in the FIFO is purged. The V\_AMERR register also records if multiple errors have occurred (with the M\_ERR bit), although the actual number of errors is not given. The error log is qualified by the value of the V\_STAT bit. The address of the errored transaction is latched in the V\_AERR register (Table B-214). When the Universe II receives a VMEbus error during a posted write, it generates an interrupt on the VMEbus and/or PCI bus depending upon whether the VERR and LERR interrupts are enabled (see "Interrupt Handling" on page 2-67, Table B-118 and Table B-120).

DTACK\* signals the successful completion of the transaction.

### Universe as VMEbus Slave

This section describes the VMEbus Slave Channel and other aspects of the Universe II as VMEbus slave. The following topics are discussed:

- Coupled Transfers, on page 2-18

- Posted Writes, on page 2-18

- Prefetched Block Reads, on page 2-20

- VMEbus Lock Commands (ADOH Cycles), on page 2-21

- VMEbus Read-Modify-Write Cycles (RMW Cycles), on page 2-22

- Location Monitors on page 2-22

- Generating PCI Configuration Cycles, on page 2-23.

The Universe II becomes VMEbus slave when one of its eight programmed slave images or register images are accessed by a VMEbus master (note that the Universe II cannot reflect a cycle on the VMEbus and access itself). Depending upon the programming of the slave image, different possible transaction types result (see "VME Slave Images" on page 2-49 for a description of the types of accesses to which the Universe II responds).

For reads, the transaction can be coupled or prefetched. Similarly, write transactions can be coupled or posted. The type of read or write transaction allowed by the slave image depends on the programming of that particular VMEbus slave image (see Figure 2-5 below and "VME Slave Images" on page 2-49). To ensure sequential consistency, prefetched reads, coupled reads, and coupled write operations are only processed once all previously posted write operations have completed (for example, the RXFIFO is empty).

Incoming cycles from the VMEbus can have data widths of 8-bit, 16-bit, 32-bit, and 64-bit. Although the PCI bus supports only two port sizes (32-bit and 64-bit), the byte lanes on the PCI bus can be individually enabled, which allows each type of VMEbus transaction to be directly mapped to the PCI data bus.

#### Note

In order for a VMEbus slave image to respond to an incoming cycle, the PCI Master Interface must be enabled (bit BM in the PCI\_CSR register, Table B-4). If data is enqueued in the VMEbus Slave Channel FIFO and the PCI BM bit is cleared, the FIFO will empty but no additional transfers will be received.

The VMEbus Interface supports a 32-bit PCI bus only

#### **Coupled Transfers**

A coupled transfer means that no FIFO is involved in the transaction and handshakes are relayed directly through the Universe II. Coupled mode is the default setting for the VMEbus slave images. Coupled transfers only proceed once all posted write entries in the RXFIFO have completed (see Posted Writes below).

A coupled cycle with multiple data beats (for example, block transfers) on the VMEbus side is always mapped to single data beat transactions on the PCI bus, where each data beat on the VMEbus is mapped to a single data beat transaction on the PCI bus regardless of data beat size. No packing or unpacking is performed. The only exception to this is when a D64 VMEbus transaction is mapped to D32 on the PCI bus. The data width of the PCI bus depends on the programming of the VMEbus slave image (32-bit or 64-bit, see "VME Slave Images" on page 2-49). The Universe II enables the appropriate byte lanes on the PCI bus as required by the VMEbus transaction. For example, a VMEbus slave image programmed to generate 32-bit transactions on the PCI bus is accessed by a VMEbus D08 BLT read transaction (prefetching is not enabled in this slave image). The transaction is mapped to single data beat 32-bit transfers on the PCI bus with only one byte lane enabled.

Target-Retry from a PCI target is not communicated to the VMEbus master. PCI transactions terminated with Target-Abort or Master-Abort are terminated on the VMEbus with BERR\*. Note that the Universe II sets the R\_TA or R\_MA bits in the PCI\_CS register (Table B-4) when it receives a Target-Abort or Master-Abort.

#### **Posted Writes**

A posted write involves the VMEbus master writing data into the Universe II's RXFIFO, rather than directly to the PCI address. Write transactions from the VMEbus are processed as posted if the PWEN bit is set in the VMEbus slave image control register (see "VME Slave Images" on page 2-49). If the bit is cleared (the default setting) the transaction bypasses the FIFO and is performed as a coupled transfer (see above). Incoming posted writes from the VMEbus are queued in the 32-entry deep RXFIFO. (The RXFIFO is the same structure as the RDFIFO. The different names are used for the FIFO's two roles, only one of which it can implement at once.) Each entry in the RXFIFO can contain 64 address bits, or 64 data bits. Each incoming VMEbus address phase, whether it is 16-bit, 24-bit, or 32-bit, constitutes a single entry in the RXFIFO and is followed by subsequent

data entries. The address entry contains the translated PCI address space and command information mapping relevant to the particular VMEbus slave image that has been accessed (see "VME Slave Images" on page 2-49). For this reason, any re-programming of VMEbus slave image attributes will only be reflected in RXFIFO entries queued after the re-programming. Transactions queued before the re-programming are delivered to the PCI bus with the VMEbus slave image attributes that were in use before the re-programming.

Incoming non-block write transactions from the VMEbus require two entries in the RXFIFO: one address entry (with accompanying command information) and one data entry. The size of the data entry corresponds to the data width of the VMEbus transfer. Block transfers require at least two entries: one entry for address and command information, and one or more data entries. The VMEbus Slave Channel packs data received during block transfers to the full 64-bit width of the RXFIFO. For example, a ten data phase D16 BLT transfer (20 bytes in total) does not require ten data entries in the RXFIFO. Instead, eight of the ten data phases (16 bits per data phase for a total of 128 bits) are packed into two 64-bit data entries in the RXFIFO. The final two data phases (32 bits combined) are queued in the next RXFIFO entry. When you add the address entry to the three data entries, this VMEbus block write has been stored in a total of four RXFIFO entries.

Unlike the PCI Target Channel (see page 2-39) the VMEbus Slave Channel does not retry the VMEbus if the RXFIFO does not have enough space to hold an incoming VMEbus write transaction. Instead, the DTACK\* response from the VMEbus Slave Interface is delayed until space becomes available in the RXFIFO. Since single transfers require two entries in the RXFIFO, two entries must be freed up before the VMEbus Slave Interface asserts DTACK\*. Similarly, the VMEbus Slave Channel requires two available RXFIFO entries before it can acknowledge the first data phase of a BLT or MBLT transfer (one entry for the address phase and one for the first data phase). If the RXFIFO has no available space for subsequent data phases in the block transfer, then the VMEbus Slave Interface delays assertion of DTACK\* until a single entry is available for the next data phase in the block transfer.

The PCI Master Interface uses transactions queued in the RXFIFO to generate transactions on the PCI bus. No address phase deletion is performed, so the length of a transaction on the PCI bus corresponds to the length of the queued VMEbus transaction. Non-block transfers are generated on the PCI bus as single data beat transactions. Block transfers are generated as one or more burst transactions, where the length of the burst transaction is programmed by the (PABS field in the MAST\_CTL register, Table B-160).

The Universe II always packs or unpacks data from the VMEbus transaction to the PCI bus data width programmed into the VMEbus slave image (with all PCI bus byte lanes enabled). For example, consider a VMEbus slave image programmed for posted writes and a D32 PCI bus that is accessed with a VMEbus D16 block write transaction. The VMEbus D16 write transaction is mapped to a D32 write transaction on the PCI bus with all byte lanes enabled. (However, note that a single D16 transaction from the VMEbus is mapped to the PCI bus as D32 with only two byte lanes enabled).

During block transfers, the Universe II will pack data to the full negotiated width of the PCI bus. This may imply that for block transfers that begin or end on addresses not aligned to the PCI bus width different byte lanes may be enabled during each data beat. If an error occurs during a posted write to the PCI bus, the Universe II uses the L\_CMDERR register (Table B-62) to log the command information for the transaction (CMDERR [3:0]). The L\_CMDERR register also records if multiple errors have occurred (with the M\_ERR bit) although the actual number is not given. The error log is qualified with the L\_STAT bit. The address of the errored transaction is latched in the LAERR register (Table B-64). An interrupt is generated on the VMEbus and/or PCI bus depending upon whether the VERR and LERR interrupts are enabled (see "Bus Error Handling" on page 2-57 and "Interrupt Handling" on page 2-67).

#### **Prefetched Block Reads**

Prefetching of read data occurs for VMEbus block transfers (BLT, MBLT) in those slave images that have the prefetch enable (PREN) bit set (see "VME Slave Images" on page 2-49). In the VMEbus Slave Channel, prefetching is not supported for non BLT/MBLT transfers.

Without prefetching, block read transactions from a VMEbus master are handled by the VMEbus Slave Channel as coupled reads. This means that each data phase of the block transfer is translated to a single data beat transaction on the PCI bus. In addition, only the amount of data requested during the relevant data phase is fetched from the PCI bus. For example, a D16 block read transaction with 32 data phases on the VMEbus maps to 32 PCI bus transactions, where each PCI bus transaction has only two byte lanes enabled. Note the VMEbus lies idle during the arbitration time required for each PCI bus transaction, resulting in a considerable performance degradation.

With prefetching enabled, the VMEbus Slave Channel uses a 32-entry deep RDFIFO to provide read data to the VMEbus with minimum latency. (The RXFIFO is the same structure as the RDFIFO. The different names are used for the FIFO's two roles, only one of which it can implement at once.) The RDFIFO is 64 bits wide, with additional bits for control information. If a VMEbus slave image is programmed for prefetching, then a block read access to that image causes the VMEbus Slave Channel to generate aligned burst read transactions on the PCI bus (the size of the burst read transactions is determined by the setting of the aligned burst size, PABS in the MAST\_CTL register). These PCI burst read transaction are queued in the RDFIFO and the data is then delivered to the VMEbus. Note that the first data phase provided to the VMEbus master is essentially a coupled read, but subsequent data phases in the VMEbus block read are delivered from the RDFIFO and are essentially decoupled (see "Prefetched Reads" on page 2-58 for the impact on bus error handling).

The data width of the transaction on the PCI bus (32-bit or 64-bit) depends on the setting of the LD64EN bit in the VMEbus slave image control register (e.g. see Table B-168) and the capabilities of the accessed PCI target. Internally, the prefetched read data is packed to 64 bits, regardless of the width of the PCI bus or the data width of the original VMEbus block read (no address information is stored with the data). Once one entry is queued in the RDFIFO, the VMEbus Slave Interface delivers the data to the VMEbus, unpacking the data as necessary to fit with the data width of the original VMEbus block read (e.g. D16, or D32). The VMEbus Slave Interface continuously delivers data from the RDFIFO to the VMEbus master performing the block read transaction. Because PCI bus data transfer rates exceed those of the VMEbus, it is unlikely that the RDFIFO will ever be unable to deliver data to the VMEbus master. For this reason, block read performance on the VMEbus will be similar to that observed with block writes. However, should the RDFIFO be unable to deliver data to the VMEbus master (which may happen if there is considerable traffic on the PCI bus or the PCI bus target has a slow response) the VMEbus Slave Interface delays DTACK\* assertion until an entry is queued and is available for the VMEbus block read.

On the PCI side, prefetching continues as long as there is room for another transaction in the RDFIFO and the initiating VMEbus block read is still active. The space required in the RDFIFO for another PCI burst read transaction is determined by the setting of the PCI aligned burst size (PABS in the MAST\_CTL register, Table B-160). If PABS is set for 32 bytes, there must be four entries available in the RDFIFO; for aligned burst size set to 64 bytes, eight entries must be available, for aligned burst size set to 128 bytes, there must be 16 entries available. When there is insufficient room in the RDFIFO to hold another PCI burst read, the read transactions on the PCI bus are terminated and only resume if room becomes available for another aligned burst AND the original VMEbus block read is still active. When the VMEbus block transfer terminates, any remaining data in the RDFIFO is purged.

Reading on the PCI side will not cross a 1024-byte boundary. The PCI Master Interface will release FRAME# and the VMEbus Slave Channel will relinquish internal ownership of the PCI Master Interface when it reaches this boundary. The VMEbus Slave Channel will re-request internal ownership of the PCI Master Interface as soon as possible, in order to continue reading from the external PCI target. (As described elsewhere, the PABS setting determines how much data must be available in the RDFIFO before the VMEbus Slave Channel continues reading.)

Regardless of the read request, the data width of prefetching on the PCI side is full width with all byte lanes enabled. If the request is unaligned, then the first PCI data beat will have only the relevant byte lanes enabled. Subsequent data beats will have full data width with all byte lanes enabled. If LD64EN is set in the VMEbus Slave image, the Universe II requests D64 on the PCI bus by asserting REQ64# during the address phase. If the PCI target does not respond with ACK64#, subsequent data beats are D32.

If an error occurs on the PCI bus, the Universe II does not translate the error condition into a BERR\* on the VMEbus. Indeed, the Universe II does not directly map the error. By doing nothing, the Universe II forces the external VMEbus error timer to expire.

The VMEbus Interface supports a 32-bit PCI bus only

#### VMEbus Lock Commands (ADOH Cycles)

The Universe II supports VMEbus lock commands as described in the VME64 specification. Under the specification, ADOH cycles are used to execute the lock command (with a special AM code). Any resource locked on the VMEbus cannot be accessed by any other resource during the bus tenure of the VMEbus master.

When the Universe II receives a VMEbus lock command, it asserts LOCK# to the addressed resource on the PCI bus. The PCI Master Interface processes this as a read transfer (with no data). All subsequent slave VMEbus transactions are coupled while the Universe II owns PCI LOCK#. Note that the VMEbus Slave Channel has dedicated access to the PCI Master Interface during the locked transaction. The Universe II holds the PCI bus lock until the VMEbus lock command is terminated, for example, when BBSY\* is negated.

The Universe II accepts ADOH cycles in any of the slave images when the Universe II PCI Master Interface is enabled (BM bit in PCI\_CSR register) and the images are programmed to map transactions into PCI Memory Space.

In the event that a Target-Abort or a Master-Abort occurs during a locked transaction on the PCI bus, the Universe II will relinquish its ownership of LOCK# in accord with the PCI bus Specification. It is the responsibility of the user to verify the R\_MA and R\_TA status bits of the PCI\_CSR status register to determine whether or not ownership of LOCK# was lost.

Once an external VMEbus masters locks the PCI bus, the Universe II DMA will not perform transfers on the PCI bus until the bus is unlocked.

#### VMEbus Read-Modify-Write Cycles (RMW Cycles)

A read-modify-write (RMW) cycle allows a VMEbus master to read from a VMEbus slave and then write to the same resource without relinquishing bus tenure between the two operations. Each of the Universe II slave images can be programmed to map RMW transactions to PCI locked transactions. If the LLRMW enable bit is set in the selected VMEbus slave image control register (e.g. Table B-168), then every non-block slave read is mapped to a coupled PCI locked read. LOCK# will be held on the PCI bus until AS\* is negated on the VMEbus. Every non-block slave read is assumed to be a RMW since there is no possible indication from the VMEbus master that the single cycle read is just a read or the beginning of a RMW.

If the LLRMW enable bit is not set and the Universe II receives a VMEbus RMW cycle, the read and write portions of the cycle will be treated as independent transactions on the PCI bus: for example, a read followed by a write. The write may be coupled or decoupled depending on the state of the PWEN bit in the accessed slave image.

#### Note

There may be an adverse performance impact for reads that are processed through a RMW-capable slave image; this may be accentuated if LOCK# is currently owned by another PCI master.

RMW cycles are not supported with unaligned or D24 cycles.

When an external VMEbus Master begins a RMW cycle, at some point a read cycle will appear on the PCI bus. During the time between when the read cycle occurs on the PCI bus and when the associated write cycle occurs on the PCI bus, no DMA transfers will occur on the PCI bus.

#### **Register Accesses**

See "Universe II Registers" on page 2-97 for a full description of register mapping and register access.

#### **Location Monitors**

Universe II has four location monitors to support a VMEbus broadcast capability. The location monitors' image is a 4-Kbyte image in A16, A24 or A32 space on the VMEbus. If enabled, an access to a location monitor causes the PCI Master Interface to generate an interrupt.

The Location Monitor Control Register (LM\_CTL, Table B-200) controls the Universe II's location monitoring. The EN field of the LM\_CTL register enables the capability. The PGM[1:0] field sets the Program/Data AM code. The SUPER[1:0] field of the LM\_CTL register sets the Supervisor/User AM code to which the Universe II responds. The VAS[3:0] field of the LM\_CTL

register specifies the address space that is monitored. The BS[31:12] field of the location monitor Base Address Register (LM\_BS, Table B-202) specifies the lowest address in the 4 Kbyte range that will be decoded as a location monitor access. While the Universe II is said to have four location monitors, they all share the same LM\_CTL and LM\_BS registers.

In address spaces A24 and A16, the respective upper address bits are ignored.

When an access to a location monitor is detected, an interrupt is generated on the PCI bus. VMEbus address bits [4:3] determine which Location Monitor will be used, and hence which of four PCI interrupts to generate. (See "Location Monitors" on page 2-73 for details on mapping the interrupts from the location monitor.)

The location monitors do not store write data. Read data from the location monitors is undefined. Location monitors do not support BLT or MBLT transfers.

Each Universe II on the VMEbus should be programmed to monitor the same 4 Kbytes of addresses on the VMEbus. Note that the Universe II may access its own location monitor. If the Universe II accesses its own (enabled) location monitor, the same Universe II generates DTACK\* on the VMEbus and thereby terminates its own cycle. This removes the necessity of the system integrator ensuring that there is another card enabled to generate DTACK\*. The generation of DTACK\* happens after the Universe II has decoded and responded to the cycle. If the location monitor is accessed by a different master, the Universe II does not respond with DTACK\*.

#### **Generating PCI Configuration Cycles**

PCI Configuration cycles can be generated by accessing a VMEbus slave image whose Local Address Space field (LAS) is set for Configuration Space.

Both Type 0 and Type 1 cycles are generated and handled through the same mechanism. Once a VMEbus cycle is received and mapped to a configuration cycle, the Universe II compares bits [23:16] of the incoming address with the value stored in the MAST\_CTL Register's Bus Number field (BUS\_NO[7:0] in Table B-160). If the bits are the same as the BUS\_NO field, then a TYPE 0 access is generated. If they are not the same, a Type 1 configuration access is generated. The PCI bus-generated address then becomes an unsigned addition of the incoming VMEbus address and the VMEbus slave image translation offset.

#### **Generating Configuration Type 0 Cycles**

The Universe II asserts one of AD[31:11] on the PCI bus to select a device during a configuration Type 0 access. To perform a configuration Type 0 cycle on the PCI bus:

- Program the LAS field of VSIx\_CTL for Configuration Space,

- Program the VSIx\_BS, VSIx\_BD registers to some suitable value,

- Program the VSIx\_TO register to 0, and

- Program the BUS\_NO field of the MAST\_CTL register to some value.

Perform a VMEbus access where:

- VA[7:2] identifies the PCI Register Number and will be mapped directly to AD[7:2],

- VA[10:8] identifies the PCI Function Number and will be mapped directly to AD[10:8],

- VA[15:11] selects the device on the PCI bus and will be mapped to AD[31:12] according to Table 2-2 on page 65,

- VA[23:16] matches the BUS\_NO in MAST\_CTL register, and

- Other address bits are irrelevant—they are not mapped to the PCI bus

Table 2-2: PCI Address Line Asserted as a Function of VA[15:11]

| VA[15:11] <sup>1</sup> | PCI Address Line Asserted <sup>2</sup> |

|------------------------|----------------------------------------|

| 00000                  | 11                                     |

| 00001                  | 12                                     |

| 00010                  | 13                                     |

| 00011                  | 14                                     |

| 00100                  | 15                                     |

| 00101                  | 16                                     |

| 00110                  | 17                                     |

| 00111                  | 18                                     |

| 01000                  | 19                                     |

| 01001                  | 20                                     |

| 01010                  | 21                                     |

| 01011                  | 22                                     |

| 01100                  | 23                                     |

| 01101                  | 24                                     |

| 01110                  | 25                                     |

| 01111                  | 26                                     |

| 10000                  | 27                                     |

| 10001                  | 28                                     |

| 10010                  | 29                                     |

| 10011                  | 30                                     |

| 10100                  | 31                                     |

<sup>1</sup>*The other values of VA[15:11] are not defined and must not be used.* <sup>2</sup>*Only one of AD[31:11] is asserted; the other address lines in AD[31:11] are negated.*

Generating Configuration Type 1 Cycles

To generate a configuration Type 1 cycle on the VMEbus:

- Program LAS field of VSIx\_CTL to Configuration Space,

- Program the VSIx\_BS, VSIx\_BD registers to some suitable value,

- Program the VSIx\_TO register to 0 and

- Program the BUS\_NO field of the MAST\_CTL register to some value.

Perform a VMEbus access where:

- VMEbus Address [7:2] identifies the PCI Register Number,

- VMEbus Address [10:8] identifies the PCI Function Number,

- VMEbus Address [15:11] identifies the PCI Device Number,

- VMEbus Address [23:16] does not match the BUS\_NO in MAST\_CTL register, and

- VMEbus Address [31:24] are mapped directly through to the PCI bus.

# **VMEbus Configuration**

The Universe II provides the following functions to assist in the initial configuration of the VMEbus system:

- First Slot Detector,

- Register Access at Power-up, and

- Auto Slot ID (two methods).

These are described separately below.

## **First Slot Detector**

As specified by the VME64 specification the First Slot Detector module on the Universe II samples BG3IN\* immediately after reset to determine whether the Universe II's host board resides in slot 1. The VMEbus specification requires that BG[3:0]\* lines be driven high after reset. This means that if a card is preceded by another card in the VMEbus system, it will always sample BG3IN\* high after reset. BG3IN\* can only be sampled low after reset by the first card in the system (there is no preceding card to drive BG3IN\* high). If BG3IN\* is sampled at logic low immediately after reset (due to the Universe II's internal pull-down), then the Universe II's host board is in slot 1 and the Universe II becomes SYSCON: otherwise, the SYSCON module is disabled. This mechanism may be overridden by software through clearing or setting the SYSCON bit in the MISC\_CTL register (Table B-162).

The Universe II monitors IACK\* (rather than IACKIN\*) when it is configured as SYSCON. This permits it to operate as SYSCON in a VMEbus chassis slot other than slot 1, provided there are only empty slots to its left. The slot with SYSCON in it becomes a virtual slot 1.

## VMEbus Register Access at Power-up

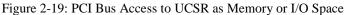

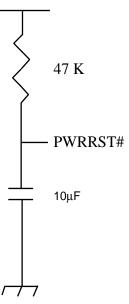

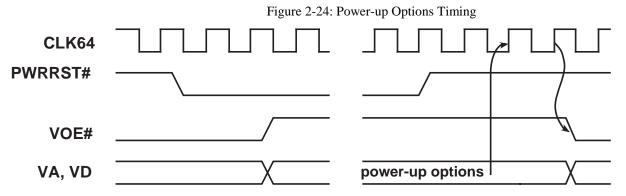

The Universe II provides a VMEbus slave image that allows access to all Universe II Control and Status Registers (UCSR). The base address for this slave image is programmed through the VRAI\_BS register (Table B-207). At power-up, the Universe II can program the VRAI\_BS and VRAI\_CTL (Table B-204) registers with information specifying the UCSR slave image (see "Power-Up Options" on page 2-112).

Register access at power-up would be used in systems where the Universe II's card has no CPU, or where register access for that card needs to be independent of the local CPU.

# **Automatic Slot Identification**

The Universe II supports two types of Auto-ID functionality. One type uses the Auto Slot ID technique as described in the VME64 specification. The other type uses a proprietary method developed by DY4 Systems and implemented in the Tundra SCV64. Neither system identifies geographical addressing, only the relative position amongst the boards present in the system (for example, fourth board versus fourth slot).

Auto-ID prevents the need for jumpers to uniquely identify cards in a system. This can:

- increase the speed of system level repairs in the field,

- reduce the possibility of incorrect configurations, and

- reduce the number of unique spare cards that must be stocked.

Both methods of Auto ID employed by the Universe II are described below.

## Auto Slot ID: VME64 Specified

The VME64 auto ID cycle (described in the VME64 Specification) requires at power-up that the Auto ID slave

- generate IRQ2\*, and

- negate SYSFAIL\*.

When the Auto ID slave responds to the Monarch's IACK cycle, it will

- enable accesses to its CR/CSR space,

- provide a Status/ID to the Monarch indicating the interrupt is an Auto-ID request,

- assert DTACK\*, and

- release IRQ2\*.

The Universe II participates in the VME64 auto ID cycle in either an automatic or semi-automatic mode. In its fully automatic mode, it holds SYSFAIL\* asserted until SYSRST\* is negated. When SYSRST\* is negated, the Universe II asserts IRQ2\* and releases SYSFAIL\*. In its semi-automatic mode, the Universe II still holds SYSFAIL\* asserted until SYSRST\* is negated. However, when SYSRST\* is negated, the local CPU performs diagnostics and local logic sets the AUTOID bit in the MISC\_CTL register (Table B-162). This asserts IRQ2\* and releases SYSFAIL\*.

After SYSFAIL\* is released and the Universe II detects a level 2 IACK cycle, it responds with the STATUS/ID stored in its level 2 STATID register (which defaults to 0xFE).

The Universe II can be programmed so that it will not release SYSFAIL\* until the SYSFAIL bit in the VCSR\_CLR register (Table B-248) is cleared by local logic (SYSFAIL\* is asserted if the SYSFAIL bit in the VCSR\_SET register, Table B-250, is set at power-up). Since the system Monarch does not service the Auto-ID slave until after SYSFAIL\* is negated, not clearing the SYSFAIL bit allows the Auto-ID process to be delayed until the CPU completes local diagnostics. Once local diagnostics are complete, the CPU clears the SYSFAIL bit and the Auto-ID cycle proceeds.

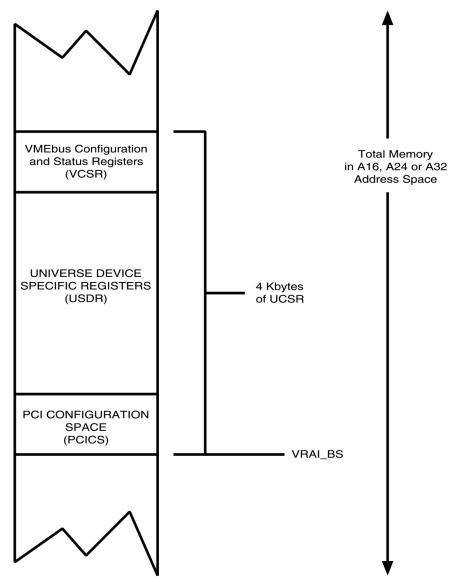

The Monarch can perform CR/CSR reads and writes at A[23:19]= 0x00 in CR/CSR space and relocate the Universe II's CR/CSR base address.

## Universe II and the Auto-ID Monarch

At power-up an Auto-ID Monarch waits to run a level 2 IACK cycle until after SYSFAIL\* goes high. After the IACK cycle is performed and it has received a Status/ID indicating an Auto-ID request, the monarch software

- masks IRQ2\* (so that it will not service other interrupters at that interrupt level until current Auto-ID cycle is completed),

- performs an access at 0x00 in CR/CSR space to get information about Auto-ID slave,

- moves the CR/CSR base address to a new location, and

- unmasks IRQ2\* (to allow it to service the next Auto-ID slave).

The Universe II supports monarch activity through its capability to be a level 2 interrupt handler. All other activity must be handled through software residing on the board.

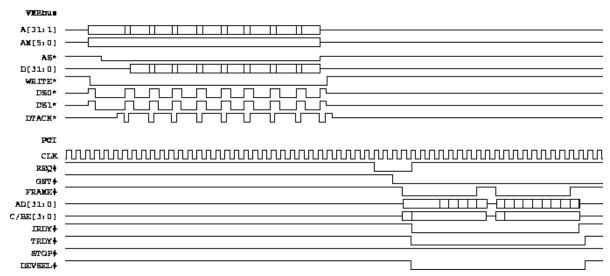

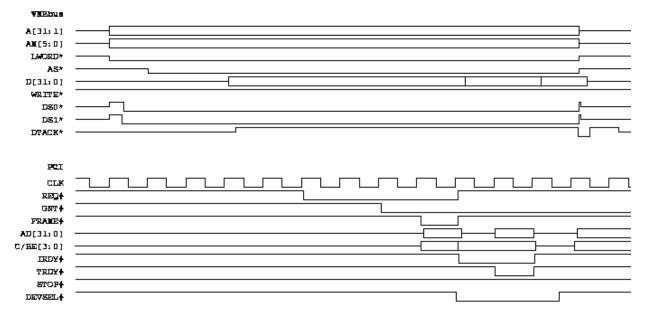

# Auto-ID: A Proprietary Tundra Method

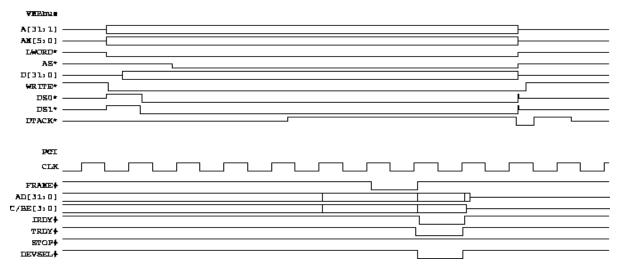

The Universe II uses a proprietary Auto-ID scheme if this is selected as a power-up option (see Auto-ID on page 163). The Tundra proprietary Auto-ID function identifies the relative position of each board in the system, without using jumpers or on-board information. The ID number generated by Auto-ID can then be used to determine the board's base address.

After any system reset (assertion of SYSRST\*), the Auto-ID logic responds to the first level one IACK cycle on the VMEbus.

After the level one IACK\* signal has been asserted (either through IRQ1\* or with a synthesized version), the Universe II in slot 1 counts five clocks from the start of the cycle and then asserts IACKOUT\* to the second board in the system (see Figure 2-6). All other boards continue counting until they receive IACKIN\*, then count four more clocks and assert IACKOUT\* to the next board. Finally, the last board asserts IACKOUT\* and the bus pauses until the data transfer time-out circuit ends the bus cycle by asserting BERR\*.

Figure 2-6: Timing for Auto-ID Cycle

SYSCLK

AS\*

DS0\*

IACK\*

IACK0UT\*

(CARD 1)

IACKOUT\*

(CARD 2)

IACKOUT\*

5

4

6

7

Because all boards are four clocks "wide", the value in the clock counter is divided by four to identify the slot in which the board is installed; any remainder is discarded. Note that since the start of the IACK cycle is not synchronized to SYSCLK, a one count variation from the theoretical value of the board can occur. However, in all cases the ID value of a board is greater than that of a board in a lower slot number. The result is placed in the DY4AUTOID [7:0] field and the DY4DONE bit is set (both are located in the MISC\_STAT register, Table B-164).

8

9

10

11

12

13

14

# **System Controller Functions**

0

0

1

When located in Slot 1 of the VMEbus system (see "First Slot Detector"), the Universe II assumes the role of SYSCON and sets the SYSCON status bit in the MISC\_CTL register (Table B-162). In accordance with the VME64 specification, as SYSCON the Universe II provides:

• a system clock driver,

2

3

- an arbitration module,

- an IACK Daisy Chain Driver (DCD), and

- a bus timer.

# System Clock Driver

(CARD 3) ID COUNTER

VALUE

The Universe II provides a 16 MHz SYSCLK signal derived from CLK64 when configured as SYSCON.

ID = 13

15

## **VMEbus Arbiter**

When the Universe II is SYSCON, the Arbitration Module is enabled. The Arbitration Module supports the following arbitration modes:

- Fixed Priority Arbitration Mode (PRI),

- Single Level Arbitration (SGL) (a subset of PRI), or

- Round Robin Arbitration Mode (RRS) (default setting).

These are set with the VARB bit in the MISC\_CTL register (Table B-162).

# Fixed Priority Arbitration Mode (PRI)

In this mode, the order of priority is VRBR#[3], VRBR#[2], VRBR#[1], and VRBR#[0] as defined by the VME64 specification. The Arbitration Module issues a Bus Grant (VBGO [3:0]#) to the highest requesting level.

If a Bus Request of higher priority than the current bus owner becomes asserted, the Arbitration Module asserts VBCLR# until the owner releases the bus (VRBBSY# is negated).

# Single Level Arbitration Mode (SGL)

In this mode, a subset of priority mode, all requests and grants are made exclusively on level 3. Set the Universe II in PRI mode to use this mode.

# **Round Robin Arbitration Mode (RRS)**

This mode arbitrates all levels in a round robin mode, repeatedly scanning from levels 3 to 0. Only one grant is issued per level and one owner is never forced from the bus in favor of another requester (VBCLR# is never asserted). Since only one grant is issued per level on each round robin cycle, several scans will be required to service a queue of requests at one level.

## **VMEbus Arbiter Time-out**

The Universe II's VMEbus arbiter can be programmed to time-out if the requester does not assert BBSY\* within a specified period. This allows BGOUT to be negated so that the arbiter may continue with other requesters. The timer is programmed using the VARBTO field in the MISC\_CTL register (Table B-162), and can be set to 16  $\mu$ s, 256  $\mu$ s, or disabled. The default setting for the timer is 16  $\mu$ s. The arbitration time-out timer has a granularity of 8  $\mu$ s; setting the timer for 16  $\mu$ s means the timer may timeout in as little as 8  $\mu$ s.

# **IACK Daisy-Chain Driver Module**

The IACK Daisy-Chain Driver module is enabled when the Universe II becomes system controller. This module guarantees that IACKIN\* will stay high for at least 30 ns as specified in rule 40 of the VME64 specification.

# VMEbus Time-out

A programmable bus timer allows users to select a VMEbus time-out period. The time-out period is programmed through the VBTO field in the MISC\_CTL register (Table B-162) and can be set to 16 $\mu$ s, 32 $\mu$ s, 64 $\mu$ s, 128  $\mu$ s, 256  $\mu$ s, 512  $\mu$ s, 1024  $\mu$ s, or disabled. The default setting for the timer is 64  $\mu$ s. The VMEbus Timer module asserts VXBERR# if a VMEbus transaction times out (indicated by one of the VMEbus data strobes remaining asserted beyond the time-out period).