# GFK-2056 New In Stock! GE Fanue Manuals

http://www.pdfsupply.com/automation/ge-fanuc-manuals/series-90-70-

# serie<sup>907</sup>90-70-9070 1-919-535-3180

IC697VAL216/IC697VAL232

www.pdfsupply.com

Email:

sales@pdfsupply.com

# **GE Fanuc Automation**

Programmable Control Products

# IC697VAL216 / IC697VAL232 / IC697VAL264 16-bit Analog-to-Digital Converter Board

User's Manual

GFK-2056

514-000434-000 B

May 2002

# Warnings, Cautions, and Notes as Used in this Publication

### Warning

Warning notices are used in this publication to emphasize that hazardous voltages, currents, temperatures, or other conditions that could cause personal injury exist in this equipment or may be associated with its use.

In situations where inattention could cause either personal injury or damage to equipment, a Warning notice is used.

Caution

Caution notices are used where equipment might be damaged if care is not taken.

### Note

Notes merely call attention to information that is especially significant to understanding and operating the equipment.

This document is based on information available at the time of its publication. While efforts have been made to be accurate, the information contained herein does not purport to cover all details or variations in hardware or software, nor to provide for every possible contingency in connection with installation, operation, or maintenance. Features may be described herein which are not present in all hardware and software systems. GE Fanuc Automation assumes no obligation of notice to holders of this document with respect to changes subsequently made.

GE Fanuc Automation makes no representation or warranty, expressed, implied, or statutory with respect to, and assumes no responsibility for the accuracy, completeness, sufficiency, or usefulness of the information contained herein. No warranties of merchantability or fitness for purpose shall apply.

The following are trademarks of GE Fanuc Automation North America, Inc.

Alarm Master CIMPLICITY CIMPLICITY 90–ADS CIMSTAR Field Control GEnet Genius Helpmate Logicmaster Modelmaster Motion Mate ProLoop PROMACRO PowerMotion PowerTRAC Series 90 Series Five Series One Series Six Series Three VersaMax VersaPro VuMaster Workmaster

©Copyright 2000 GE Fanuc Automation North America, Inc. All Rights Reserved.

| Chapter 1 | Introduction, Description, and Specifications                     | 1-1 |

|-----------|-------------------------------------------------------------------|-----|

|           | Reference Material and Other GE Fanuc Manuals                     |     |

|           | General Description                                               |     |

|           | Functional Description                                            |     |

|           | Safety Summary                                                    |     |

| Chapter 2 | Configuration and Installation                                    | 2-1 |

|           | Physical Installation                                             |     |

|           | Before Applying Power: Checklist                                  |     |

|           | Operational Configuration                                         |     |

|           | Calibration                                                       |     |

|           | Connector Descriptions                                            |     |

|           | System Considerations                                             |     |

| Chapter 3 | Programming                                                       |     |

|           | Introduction to Controlling the Analog-to-Digital Converter Board |     |

|           | General Control Features                                          |     |

|           | Control Registers                                                 |     |

|           | Timer/Counter Control General Characteristics                     |     |

|           | Data Organization and Control                                     |     |

|           | Operating Modes                                                   |     |

|           | Bus Interrupter                                                   |     |

|           | Typical Programming Examples                                      |     |

| Chapter 4 | Theory of Operation                                               | 4-1 |

|           | Internal Functional Organization                                  |     |

|           | Control Interface                                                 |     |

|           | Data Buffer Memory                                                |     |

|           | Operating Modes                                                   |     |

|           | Analog Input Multiplexing, Sampling, and Digitizing               |     |

|           | Power Converter                                                   |     |

| Chapter 5 | Maintenance                                                       | 5-1 |

Chapter 1

# Introduction, Description, and Specifications

This manual describes the features, installation, and operation of the following Standard Performance, 16-bit Analog-to-Digital Converter Boards:

| Part Number | Channels    | Connectors                | Contact Type |

|-------------|-------------|---------------------------|--------------|

| IC697VAL216 | 16 channels | two 96-pin DIN connectors | Non-latching |

| IC697VAL232 | 32 channels | two 96-pin DIN connectors | Non-latching |

| IC697VAL264 | 64 channels | two 96-pin DIN connectors | Non-latching |

# Reference Material and Other GE Fanuc Manuals

For a detailed explanation of the VMEbus and its characteristics, "The VMEbus Specification" is available from:

VITA VMEbus International Trade Association 7825 East Gelding Dr., No. 104 Scottsdale, AZ 85260 (480) 951-8866 FAX: (480) 951-0720 Internet: www.vita.com

The following Application and Configuration Guides are available from GE Fanuc to assist in the selection, specification, and implementation of systems based upon GE Fanuc's products:

| Analog I/O Products (Built-in-Test)<br>Configuration Guide (catalog number<br>GFK-2084) | Provides assistance in configuring analog I/O<br>subsystems based on GE Fanuc's analog I/O<br>products, including common designs, which offer a<br>wide variety of solutions. |

|-----------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Connector and I/O Cable Application<br>Guide (catalog number GFK-2085)                  | Describes I/O connections that can be used with GE Fanuc's VMEbus products. Includes connector compatibility information and examples.                                        |

### General Description

The Analog-to-Digital Converter Board is a member of GE Fanuc's extensive family of analog input/output products for the VMEbus. With 16-bit digitizing resolution, program-controlled gain, selectable conversion rate, and automatic scanning of 64 differential analog inputs, the Analog-to-Digital Converter Board provides exceptional dynamic range and analog input channel density. Various operating modes are supported, including autoscanning, data bursts, and external synchronization. This board is designed to interface directly with GE Fanuc's line of signal conditioning boards for digitizing the outputs from thermocouples, RTDs, and strain gages.

Individual channel gains can be downloaded for use during scanning operations, or the board can be configured with a fixed gain that is common to all channels. Multiple boards can be synchronized together to enable as many as 16 boards to initiate each scan simultaneously. An Interval Timer, Bus Interrupter, Channel Counter, and Midscan/Endscan flag simplify the monitoring of data within the dual port data buffer. The system applications that can benefit from the Analog-to-Digital Converter Board capabilities include factory automation, process control, data acquisition systems, training simulators, and laboratory instrumentation. The following brief overview of principal features illustrates the flexibility and performance that is available with the Analog-to-Digital Converter Board:

- 16, 32, or 64 differential analog inputs

- 16-bit A/D conversion

- 381 Hz to 50 kHz selectable scanning rate

- Programmable gains of x1 or x10

- A/D converter ranges of  $\pm 2.5$  V,  $\pm 5$  V,  $\pm 10$  V, 0 to +5 V, 0 to +10 V

- Programmable channel gains

- 16- to 1,024-word dual port data buffer

- Operation in short I/O (A16), standard (A24), or extended (A32) data space

- Programmable channel block size and buffer size

- 500 Hz low pass input filters

- Continuous and burst operating modes

- Free running operation or external/internal triggering

- Bus interrupter for Midscan or Endscan indication

- Programmable interval timer for timed data bursts

- Direct cabling from GE Fanuc signal conditioning boards

- Initializes after a reset in autoscan mode with gain = x1

### Functional Description

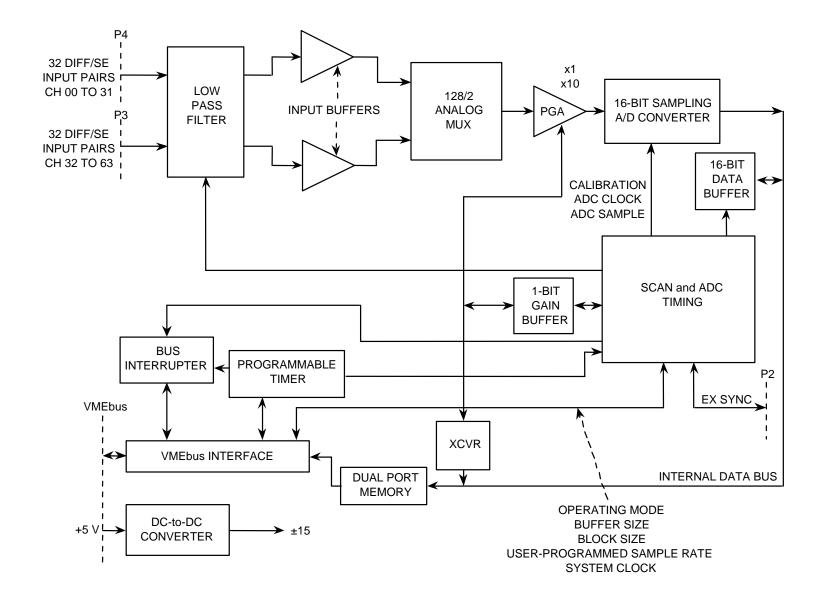

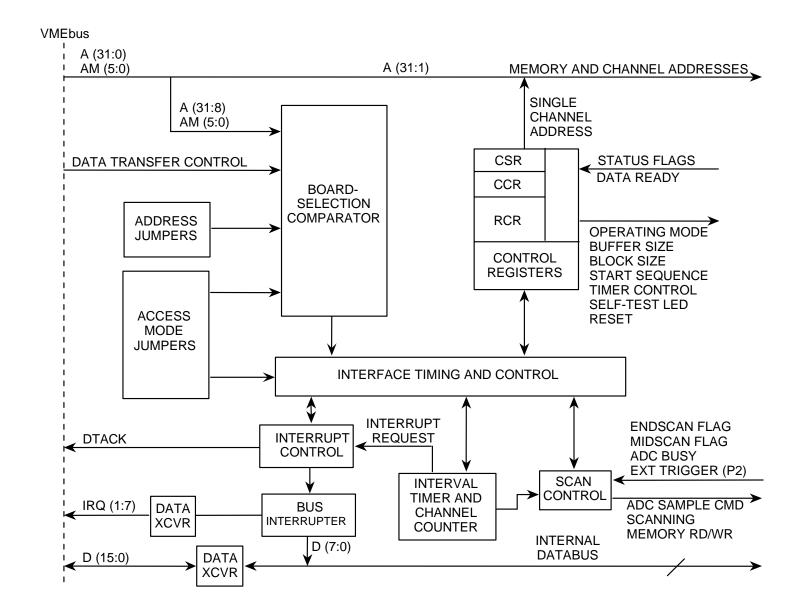

The Analog-to-Digital Converter Board (see Figure 1-1 on page 1-5) is a high-resolution, 16-bit, 64-channel Analog Scanning and Digitizing Input board for VMEbus system applications. Dual-ported data memory, on-board timers, automatically controlled gain, and a programmable bus interrupter enable the Analog-to-Digital Converter Board to support extensive analog input traffic, with minimum involvement of the host processor.

Analog inputs are scanned and digitized sequentially. The digital values are stored in a dual port data buffer which can be accessed at any time from the VMEbus. The gain of each channel can be programmed individually, or can be set in software for a fixed gain common to all channels. Channel gain is software selectable as x1 or x10. A/D converter voltage ranges are jumper-selectable for  $\pm 2.5$  V,  $\pm 5$  V,  $\pm 10$  V, 0 to 5 V, 0 to 10 V.

When a system or program reset occurs, the board initializes in the 64-channel autoscanning mode at a rate of 100 kHz and all channel gains are initialized to unity (x1). However, you must re-configure the board upon reset to autoscan at a rate of 50 kHz. After a reset operation, the program can select the timed burst or triggered burst modes, and can modify the block size, buffer size, and channel gains as necessary. The channel block is adjustable as 1, 8, 16, 32, or 64 channels, and the data buffer size can be selected from 16 to 1,024 data words in binary increments.

Timed data bursts are controlled by an interval timer which can provide repetitive or single-shot burst intervals of up to 687 sec. A burst can consist of from 8 to1,024-channel samples. A data ready flag is available at the middle or end of a scan, and an interrupt request can be generated simultaneously with the flag. The interrupt can also be initiated after a specific number of samples have been acquired.

Figure 1-1: Analog-to-Digital Converter Board Functional Block Diagram

# Safety Summary

### Warning

The following general safety precautions must be observed during all phases of this operation, service, and repair of this product. Failure to comply with these precautions or with specific warnings elsewhere in this manual violates safety standards of design, manufacture, and intended use of this product. GE Fanuc assumes no liability for the customer's failure to comply with these requirements.

### Ground the System

To minimize shock hazard, the chassis and system cabinet must be connected to an electrical ground. A three-conductor AC power cable should be used. The power cable must either be plugged into an approved three-contact electrical outlet or used with a three-contact to two-contact adapter with the grounding wire (green) firmly connected to an electrical ground (safety ground) at the power outlet.

### Do Not Operate in an Explosive Atmosphere

Do not operate the system in the presence of flammable gases or fumes. Operation of any electrical system in such an environment constitutes a definite safety hazard.

### Keep Away from Live Circuits

Operating personnel must not remove product covers. Component replacement and internal adjustments must be made by qualified maintenance personnel. Do not replace components with power cable connected. Under certain conditions, dangerous voltages may exist even with the power cable removed. To avoid injuries, always disconnect power and discharge circuits before touching them.

### Do Not Service or Adjust Alone

Do not attempt internal service or adjustment unless another person, capable of rendering first aid and resuscitation, is present.

### Do Not Substitute Parts or Modify System

Because of the danger of introducing additional hazards, do not install substitute parts or perform any unauthorized modification to the product. Return the product to GE Fanuc for service and repair to ensure that safety features are maintained.

Chapter 2

# Configuration and Installation

This chapter gives configuration and installation instructions for the Analog-to-Digital Converter Board, and is divided into the following sections:

- Physical Installation

- Before Applying Power: Checklist

- Operational Configuration

- Calibration

- Connector Descriptions

- Considerations

- System Considerations

Caution

Some of the components assembled on GE Fanuc's products may be sensitive to electrostatic discharge and damage may occur on boards that are subjected to a high energy electrostatic field. Unused boards should be stored in the same protective boxes in which they were shipped. When the board is to be placed on a bench for configuring, etc., it is suggested that conductive material be inserted under the board to provide a conductive shunt.

Upon receipt, any precautions found in the shipping container should be observed. All items should be carefully unpacked and thoroughly inspected for damage that might have occurred during shipment. The board(s) should be checked for broken components, damaged circuit board(s), heat damage, and other visible contamination. All claims arising from shipping damage should be filed with the carrier and a complete report sent to GE Fanuc together with a request for advice about the disposition of the damaged item(s).

# Physical Installation

2

Caution

#### Do not install or remove boards while power is applied.

De-energize the equipment and insert the board into an appropriate slot of the chassis. While ensuring that the board is properly aligned and oriented in the supporting card guides, slide the board smoothly forward against the mating connector until firmly seated.

# Before Applying Power: Checklist

Before applying power to the VMEbus chassis in which the board is installed, execute the following checklist to ensure that the board has been correctly prepared for operation.

- Verify that the chapters pertaining to programming and configuration, chapters 2 and 3, have been reviewed and applied to system requirements.

- Review "Operational Configuration" on page 2-4 and Table 2-1 on page 2-5 to verify that all jumpers are configured correctly for the application.

- Verify that the I/O cables are properly terminated for the input/output connectors. Refer to the "Connector Descriptions" on page 2-17 for connector descriptions.

- Physical installation should have been completed as described in "Physical Installation" on page 2-2.

- Ensure that all system cable connections are correct.

# **Operational Configuration**

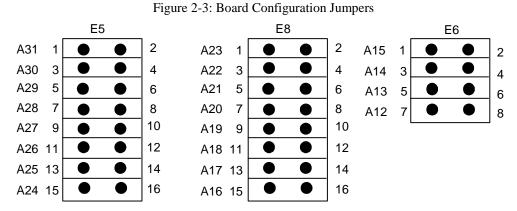

VMEbus access modes and analog input configurations are controlled by field replaceable jumpers. This section describes the use of these jumpers, and their effects on board performance. Locations and functions of all Analog-to-Digital Converter Board jumpers are shown in Figure 2-4 on page 2-12 and Table 2-1 on page 2-5. Typical jumper configurations are summarized in Table 2-2 on page 2-6.

# **Factory-Installed Jumpers**

Each Analog-to-Digital Converter Board is configured at the factory with the specific jumper arrangement shown in Table 2-1 on page 2-5. The factory configuration establishes the following functional baseline for the Analog-to-Digital Converter Board, and ensures that all essential jumpers are installed.

- Board Identification is located at \$0000 in the Short I/O Space, with either Supervisory or Nonprivileged access

- ±10 V range

- Differential inputs

- LOW inputs for channels 31 and 63 are disconnected from COMM and AGND

| Jumper IDENT | Function (Installed)                   | Factory CONFIG |

|--------------|----------------------------------------|----------------|

| E13-1,2      | Access Mode                            | Installed      |

| E13-3,4      | Access Mode                            | Installed      |

| E11-1,2      | Address Mode                           | Installed      |

| E11-3,4      | Address Mode                           | Installed      |

| E5-1,2       | Address Bit A31 = 0                    | Installed      |

| E5-3,4       | Address Bit $A30 = 0$                  | Installed      |

| E5-5,6       | Address Bit A29 = 0                    | Installed      |

| E5-7,8       | Address Bit $A28 = 0$                  | Installed      |

| E5-9,10      | Address Bit A27 = 0                    | Installed      |

| E5-11,12     | Address Bit $A26 = 0$                  | Installed      |

| E5-13,14     | Address Bit $A25 = 0$                  | Installed      |

| E5-15,16     | Address Bit $A24 = 0$                  | Installed      |

| E8-1,2       | Address Bit $A23 = 0$                  | Installed      |

| E8-3,4       | Address Bit $A22 = 0$                  | Installed      |

| E8-5,6       | Address Bit A21 = 0                    | Installed      |

| E8-7,8       | Address Bit A20 = 0                    | Installed      |

| E8-9,10      | Address Bit A19 = 0                    | Installed      |

| E8-11,12     | Address Bit A18 = 0                    | Installed      |

| E8-13,14     | Address Bit A17 = 0                    | Installed      |

| E8-15,16     | Address Bit $A16 = 0$                  | Installed      |

| E6-1,2       | Address Bit $A15 = 0$                  | Installed      |

| E6-3,4       | Address Bit $A14 = 0$                  | Installed      |

| E6-5,6       | Address Bit $A13 = 0$                  | Installed      |

| E6-7,8       | Address Bit $A12 = 0$                  | Installed      |

| E1-1,2       | CH 31 LOW Input<br>Conn to AGND        | Removed        |

| E2-1,2       | CH 63 LOW Input<br>Conn to AGND        | Removed        |

| E7-1,2       | Bipolar Analog inputs                  | Installed      |

| E7-2,3       | Unipolar Analog inputs                 | Removed        |

| E10-1,2      | ±2.5 V Range Gain<br>Multiplier        | Removed        |

| E9-1,2       | ±2.5 V Range Gain<br>Multiplier        | Removed        |

| E12-2,3      | ±10 V Range                            | Installed      |

| E12-1,2      | ±2.5 V, 0 to +5 V, 0 to<br>+10 V Range | Removed        |

| E3-3,2       | PGA_H                                  | Installed      |

| E3-1,2       | PGA_H Offset CAL                       | Removed        |

| E4-3,2       | PGA_L                                  | Installed      |

| E4-1,2       | PGA_L Offset CAL                       | Removed        |

Table 2-1: Programmable Jumper Functions

### Table 2-2: Typical Jumper Configurations

| Jumper   | State            | Position  |

|----------|------------------|-----------|

| E11-1,2  | STD Address Mode | Removed   |

| E11-3,4  | STD Address Mode | Removed   |

| E13-1,2  | SPVSR            | Removed   |

| E13-3,4  | SPVSR            | Removed   |

| E6-1,2   | A15=1            | Removed   |

| E6-3,4   | A14=1            | Removed   |

| E6-5,6   | A13=1            | Removed   |

| E6-7,8   | A12=1            | Removed   |

| E8-1,2   | A23=1            | Removed   |

| E8-3,4   | A22=1            | Removed   |

| E8-5,6   | A21=0            | Installed |

| E8-7,8   | A20=1            | Removed   |

| E8-9,10  | A19=0            | Installed |

| E8-11,12 | A18=0            | Installed |

| E8-13,14 | A17=0            | Installed |

| E8-15,16 | A16=1            | Removed   |

| E5-1,2   | A31=0            | Installed |

| E5-3,4   | A30=0            | Installed |

| E5-5,6   | A29=0            | Installed |

| E5-7,8   | A28=0            | Installed |

| E5-9,10  | A27=0            | Installed |

| E5-11,12 | A26=0            | Installed |

| E5-13,14 | A25=0            | Installed |

| E5-15,16 | A24=0            | Installed |

Example of Addressing Configuration for: Standard Address Mode; Supervisory Only; Address \$00D1 F000

### Note

To be consistent with conventional VMEbus development system nomenclature, hexadecimal numbers in this document are designated with a "\$" prefix unless otherwise indicated. Decimal numbers are presented without a prefix.

# **Access Modes**

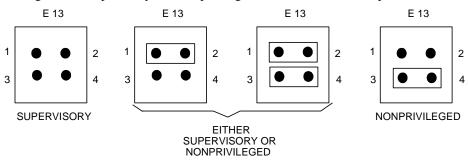

Supervisory (privileged) and user (nonprivileged) access is selected by jumper E13. Figure 2-1 below shows the jumper location and access mode.

Figure 2-1: Supervisory and Nonprivileged Access Mode and Jumper Locations

# **Address Modes**

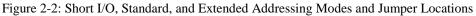

Short I/O, Standard, and Extended Addressing is selected by jumper E11. Figure 2-2 below shows the jumper location and address mode.

2

# **Board Address**

The board address is configured by jumpers E5, E8, and E6. The board supports A32/A24/A16 addressing. The jumpers corresponding to the address bits are shown in Figure 2-3 below.

The board address is programmed by installing shorting plugs at all "zero" or LOW address bit positions in jumper blocks E5, E6, and E8, and by omitting the shorting plugs at the "one" or HIGH positions. Address bit A12 is the least significant address bit that can be jumper-selected, and has a weight of 4,096 bytes.

# **Converter Voltage Range**

The A/D Converter voltage range is controlled by jumpers E7, E9, E10, and E12 as shown in Table 2-3 below.

| ADC Voltage Range * |       |      |        |            |           |  |

|---------------------|-------|------|--------|------------|-----------|--|

| Jumper              | ±10 V | ±5 V | ±2.5 V | 0 TO +10 V | 0 TO +5 V |  |

| E12                 | 2,3   | 1,2  | 1,2    | 1,2        | 1,2       |  |

| E10                 | REM   | REM  | INS    | REM        | INS       |  |

| E7                  | 1,2   | 1,2  | 1,2    | 2,3        | 2,3       |  |

| E9                  | REM   | REM  | INS    | REM        | INS       |  |

Table 2-3: A/D Converter Voltage Ranges

\* "INS" = Jumper installed, "REM" = Jumper removed.

### Note

The board must be recalibrated if the range is changed from the factory configuration of  $\pm 10$ V.

### Input Voltage Range

The input voltage range (full scale voltage at the input of each channel) is determined by both the analog input gain and the A/D converter voltage range:

INPUT VOLTAGE RANGE = CONVERTER VOLTAGE RANGE ÷ INPUT GAIN

For example, an input gain of x10 combined with a converter voltage range of  $\pm 5$  V produces an input voltage range of  $\pm 500$  mV ( $\pm 0.5$  V).

#### Note

Care must be exercised not to apply input voltages and gain combinations which exceed the converter voltage range. For example, a gain of 10 with an input voltage greater than 1.2 volts exceeds the maximum converter voltage range. In these cases, the data received will not be valid but may appear as valid data.

### Input Configurations

The analog inputs are configured as differential channels, as shown in Table 2-4 on page 2-11. The configurations are selected in groups of four consecutive channels by the positions of jumpers E1 and E2, and by the locations of SIP (single-in-line-package) resistor networks.

Each LOW side input has a 22  $\Omega$  resistor tied to AGND. The purpose of this resistor is to provide floating input protection. If the input lead is not connected, the board will see that channel at ground through 22  $\Omega$  resistor.

# **Internal Ground Connections**

All pins in the center "B" rows of both input connectors P3 and P4 are connected together to AGND, and provide a ground path and interchannel guards between differential input pairs when 96-wire 0.033-inch ribbon cables are used.

# Calibration

Before delivery from the factory, the Analog-to-Digital Converter Board is fully calibrated and conforms to all specifications. Should recalibration be required, refer to "Equipment Required" on page 2-13, "Calibration Procedure" on page 2-14, and "Functional Verification" on page 2-16, and perform the indicated procedures in the order shown. The locations of test points and adjustments are shown in Figure 2-4 on page 2-12.

### Note

The board must be recalibrated if the range is changed from the factory configuration of  $\pm 10$ V.

#### **Table 2-4: Input Configuration Selection**

| Input Configuration (Note 1) |              |                |    |  |

|------------------------------|--------------|----------------|----|--|

|                              | Differential |                |    |  |

| P4 Channel<br>Group          | SIP POS      | IP POS Jumpers |    |  |

|                              | (Note 2)     | E1             | E2 |  |

| 00 to 03                     | RP1          |                | _  |  |

| 04 to 07                     | RP3          |                |    |  |

| 08 to 11                     | RP5          |                |    |  |

| 12 to 15                     | RP7          |                | —  |  |

| 16 to 19                     | RP9          |                |    |  |

| 20 to 23                     | RP11         |                |    |  |

| 24 to 27                     | RP13         |                |    |  |

| 28 to 31                     | RP15         | REM            |    |  |

| Input Configuration (Note 1) |                              |    |     |  |

|------------------------------|------------------------------|----|-----|--|

|                              | Differential SIP POS Jumpers |    |     |  |

| P3 Channel<br>Group          |                              |    |     |  |

|                              | (Note 2)                     | E1 | E2  |  |

| 32 to 35                     | RP17                         |    |     |  |

| 36 to 39                     | RP19                         |    |     |  |

| 40 to 43                     | RP21                         |    |     |  |

| 44 to 47                     | RP23                         |    |     |  |

| 48 to 51                     | RP25                         |    |     |  |

| 52 to 55                     | RP27                         |    |     |  |

| 56 to 59                     | RP29                         |    |     |  |

| 60 to 63                     | RP31                         |    | REM |  |

### Note

- 1. Jumper positions are indicated as:

- 1,2 Shorting plug between pins 1 and 2.

- 2,3 Shorting plug between pins 2 and 3. REM Shorting plug removed.

- "Don't care"; shorting plug can be installed or removed.

- 2. "SIP POS" = "Single-in-line-package position." The indicated position is one of two possible locations for the input SIP. Only one of the two locations is occupied. For example, the SIP for channel group 00 to 03 can be located as either RP33 or RP1.

Figure 2-4: Locations of Test Points and Adjustments

# **Equipment Required**

| Digital Voltmeter (DVM) | 1.000 and 10.000 VDC ranges; 5 or more digits;<br>±0.003 percent of reading measurement accuracy;<br>10 M minimum input impedance.                                                                                                                                                                                                          |

|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Digital Voltage Source  | 10.000 VDC $\pm 0.001$ VDC voltage source; $\pm 0.003$ percent setting resolution and accuracy. 10 M maximum source resistance.                                                                                                                                                                                                             |

| Chassis                 | VMEbus backplane or equivalent, with J1<br>connector, 68000 Series master controller, $+5 \pm 0.1$<br>VDC, 7 A (reserve current) power supply. One slot<br>allocated for testing the Analog-to-Digital<br>Converter Board.                                                                                                                  |

| Extender Board          | VMEbus extender board.                                                                                                                                                                                                                                                                                                                      |

| Grounded input adapter  | 96-pin DIN connector (2 each) i.e., DIN 96CSC<br>WTR4093 with row A connections shorted to row<br>B connections shorted to row C connections. This<br>connector(s) plugs into the Analog-to-Digital<br>Converter Board's P3 and P4 connectors and<br>grounds all of the board's inputs for calibration<br>purposes.                         |

| All channels adapter    | 96-pin DIN connector (2 each) i.e., DIN 96CSC<br>WTR4093 with all row C connections shorted<br>together and to row B and all row A connections<br>shorted together. This connector(s) plugs into the<br>Analog-to-Digital Converter Board's P3 and P4<br>connectors allowing input voltage to be applied to<br>all channels simultaneously. |

| Common mode adapter     | 96-pin DIN connector (2 each) i.e., DIN 96CSC<br>WTR4093 with rows A and C shorted together.<br>This connector(s) plug into the Analog-to-Digital<br>Converter Board's P3 and P4 connectors allowing<br>for common-mode calibration.                                                                                                        |

### Note

Do not install or remove this board with power applied to the system.

2

# **Calibration Procedure**

- 1. Restore all program jumpers to the factory configuration, as shown in Table 2-1 on page 2-5.

- 2. Locate the board at an address that is compatible with the VMEbus operating system.

- 3. Install the Analog-to-Digital Converter Board on an extender board in the VMEbus chassis.

- 4. Place grounded input adapter in P3 and P4 connectors.

- Apply power to the chassis backplane. Allow a minimum warm-up interval of ten minutes before proceeding.

| Address | Data   | Register   | Mode               |

|---------|--------|------------|--------------------|

| \$000C  | \$C000 | S.W. Reset | Reset              |

| \$0004  | \$5800 | CCR        | Gain x1, Auto Scan |

6. Write the following data to the indicated board relative address:

### **ADC Reference ADJ**

- 7. Connect the digital voltmeter between TP3 (+) and TP1 (-).

- 8. Adjust potentiometer R82 for a reading of  $\pm 10.0000 \pm 0.00015$  VDC.

- 9. Move jumper from E12-2,3 to E12-1,2.

- 10. Adjust potentiometer R85 for a reading of  $+5.00000 \pm 0.00005$  VDC.

- 11. Move jumper from E12-1,2 to E12-2,3.

### **Offset ADJ**

- 12. Connect positive lead of DVM to TP4, connect the negative to TP1.

- 13. Observe meter reading then write \$5900 to address \$0004.

- 14. Adjust R76 until meter reads the same value for both \$5800 and \$5900 written to address \$0004.

- 15. With \$5800 written to \$0004 read and display board locations \$0080 through \$00FE repetitively, at 3 to 5 readings/sec.

- 16. Adjust R75 until the majority of reading display \$8000.

- 17. Remove grounded input adapter from P3 and P4 connectors.

### **CM ADJ**

- 18. Place common-mode adapter in P3 and P4 connectors.

- 19. Connect positive lead of voltage source to row A on adapter, connect negative lead to row B on adapter and set voltage source output to 0.0000 VDC.

- 20. With \$5800 written to \$0004 read and display board locations \$0080 through \$00FE repetitively, at 3 to 5 readings/sec.

- 21. Note the majority of readings. They should be \$8000. Set the voltage source to +10.0000 VDC. The majority of reading should still be \$8000. If readings differ by more than 1 count, adjust R79 until display reads \$8000. Set voltage source to -10.0000 VDC. Adjust R79 if necessary to have display read \$8000. Toggle between +10.0000 VDC and -10.0000 VDC and verify display reads \$8000.

- 22. Write \$5900 to board address \$0004 to set gain to 10.

- 23. With the voltage source set at 0.0000 VDC, note the majority of reading. Apply +10.0000 VDC and adjust R80 so reading do not differ from 0.0000 VDC reading by more than 3 counts. Do the same with -10.0000 VDC until both voltages produce no more than 3 counts deviation.

- 24. Repeat steps 20 through 23 until both values are correct.

- 25. Remove voltage source, and common mode calibration adapter.

### **GAIN ADJ**

- 26. Place All Channels adapter on P3 and P4. Connect positive lead of voltage source on "A" row and negative lead on "B" row. Rows "B" and "C" should be connected on adapter.

- 27. With \$5800 written to \$0004 read and display board locations \$0080 through \$00FE repetitively, at 3 to 5 readings/sec.

- 28. With the voltage set at -9.9997 VDC, adjust R68 until the majority of display values vary between \$0000 and \$0001. Due to noise, some channels may read greater than \$0001 occasionally.

- 29. With the voltage set at +9.9997 VDC, verify that the display values vary between \$FFFE and \$FFFF.

- 30. Repeat steps 28 and 29 until both values are correct.

- 31. Write \$5900 to board address \$0004 to set gain of 10.

- 32. With the voltage set at +0.99997 VDC, adjust R71 until the majority of display values vary between \$FFFE and \$FFFF. Due to noise, some channels may read greater than \$0001 occasionally.

- 33. With the voltage set at -0.99997 VDC, verify that the display values vary between \$0000 and \$0001.

# **Functional Verification**

This procedure tests the Programmable Gain Amplifier (PGA), and verifies the integrity of all input channels. Steps *1* through *5* are identical to steps *1* through *5* in "Calibration Procedure" on page 2-14, and can be omitted if the calibration procedure has been performed within the previous hour, and if power has not been removed from the board.

- 1. Restore all program jumpers to the factory configuration, as shown in Table 2-1 on page 2-5.

- 2. Locate the board at an address that is compatible with the VMEbus operating system.

- 3. Install the Analog-to-Digital Converter Board on an extender board in the VMEbus chassis.

- 4. Apply power to the chassis backplane. Allow a minimum warm-up interval of ten minutes before proceeding.

- 5. Connect the digital voltage source to the channel 00 input pins P4-A1 (+) and P4-C1 (-). Using a connector that shorts the "B" row to the "C" row, adjust voltage source output to 0.0000 VDC.

- 6. Write the following data to the indicated board address:

| Address | Data   | Register   | Mode            |

|---------|--------|------------|-----------------|

| \$000C  | \$C000 | S.W. RESET | Reset           |

| \$0004  | \$5900 | CCR        | GX10, Auto Scan |

- 7. Read and display board word location \$0080 (input channel 00) repetitively, at 3 to 5 readings /sec.

- 8. Adjust the voltage source output to +992.19 mVDC, and verify that the displayed value is between \$FED0 and \$FF30.

- 9. Write \$5800 to address \$0004 to set gain = 1.

- 10. Adjust the voltage source output to +9.9219 VDC, and verify that the displayed value is between \$FEFB and \$FF05.

- 11. Refer to the P3 and P4 connector descriptions in the table in Figure 2-6 on page 2-19 (P3) and the table in Figure 2-7 on page 2-20 (P4) to determine the input pairs used in the remainder of this procedure.

- 12. Move the digital voltage source test leads to the channel 01 input pins. Connect the positive test lead to the A row pin, and the negative test lead to the C row pin.

- 13. Change the address of the displayed data to \$0082 (input channel 01). Verify that the displayed value is between \$FEFA and \$FF06.

- 14. Repeat steps 14 and 15 for the remaining channels 02 through 63. Increase the displayed address by \$0002 for each successive channel, to a maximum address of \$00FE for channel 63.

- 15. Functional verification is completed. Remove power from the board. Remove all test connections. Restore the board to the factory configuration, as shown in Table 2-1 on page 2-5.

# **Connector Descriptions**

# **Connector Functions**

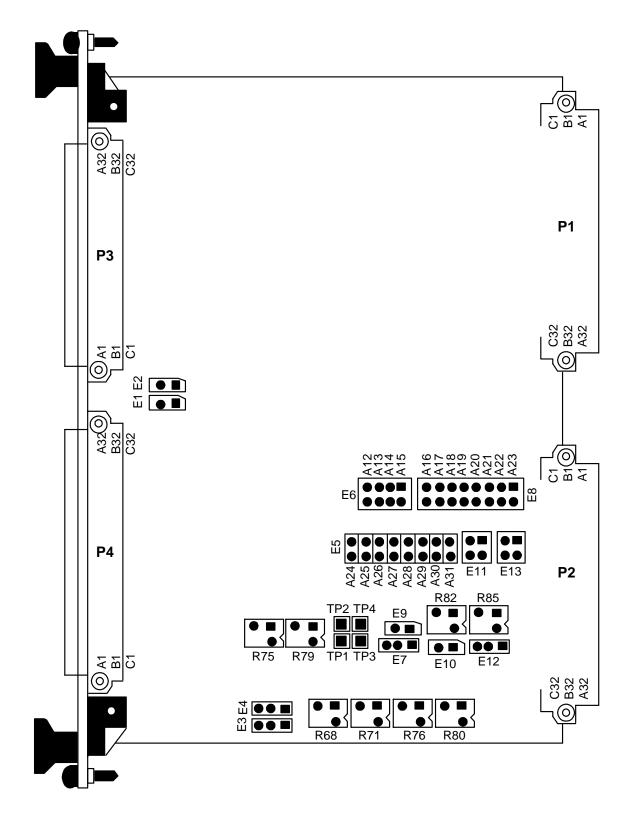

Electrical connections to the Analog-to-Digital Converter Board are made through four 96-pin DIN connectors P1 through P4, all of which have the pin configuration shown in Figure 2-4 on page 2-12. P1 connects the Analog-to-Digital Converter Board to the VMEbus backplane, and contains the address, data, and control lines, and all additional signals necessary to control VMEbus functions related to the board.

P2 provides the user pins necessary for external synchronization of the board as well as upper address/data lines. User pin assignments are listed in the table in Figure 2-5 on page 2-18.

Figure 2-5: P2 Connector Pinout

2

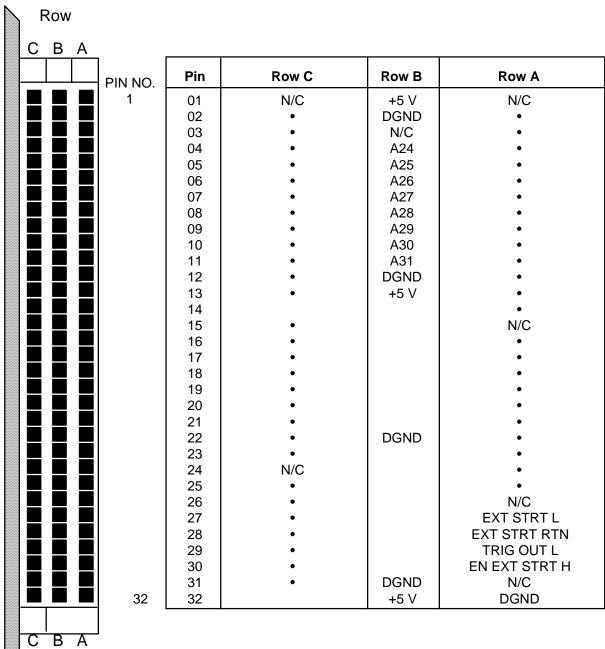

#### Figure 2-6: P3 Connector Pinout

гJ

2

| Row                                                                 |     |            |       |            |  |

|---------------------------------------------------------------------|-----|------------|-------|------------|--|

| АВС                                                                 |     |            |       |            |  |

| PIN NO.                                                             | Pin | Row A      | Row B | Row C      |  |

| 32                                                                  | 32  | CH 31 HIGH |       | CH 31 LOW* |  |

|                                                                     | 31  | CH 30 HIGH |       | CH 30 LOW  |  |

|                                                                     | 30  | CH 29 HIGH | AGND  | CH 29 LOW  |  |

|                                                                     | 29  | CH 28 HIGH |       | CH 28 LOW  |  |

|                                                                     | 28  | CH 27 HIGH | •     | CH 27 LOW  |  |

|                                                                     | 27  | CH 26 HIGH |       | CH 26 LOW  |  |

|                                                                     | 26  | CH 25 HIGH |       | CH 25 LOW  |  |

|                                                                     | 25  | CH 24 HIGH | •     | CH 24 LOW  |  |

|                                                                     | 24  | CH 23 HIGH |       | CH 23 LOW  |  |

|                                                                     | 23  | CH 22 HIGH |       | CH 22 LOW  |  |

|                                                                     | 22  | CH 21 HIGH | •     | CH 21 LOW  |  |

|                                                                     | 21  | CH 20 HIGH |       | CH 20 LOW  |  |

|                                                                     | 20  | CH 19 HIGH |       | CH 19 LOW  |  |

|                                                                     | 19  | CH 18 HIGH | •     | CH 18 LOW  |  |

|                                                                     | 18  | CH 17 HIGH |       | CH 17 LOW  |  |

|                                                                     | 17  | CH 16 HIGH |       | CH 16 LOW  |  |

|                                                                     | 16  | CH 15 HIGH | AGND  | CH 15 LOW  |  |

|                                                                     | 15  | CH 14 HIGH | -     | CH 14 LOW  |  |

|                                                                     | 14  | CH 13 HIGH | •     | CH 13 LOW  |  |

|                                                                     | 13  | CH 12 HIGH |       | CH 12 LOW  |  |

|                                                                     | 12  | CH 11 HIGH |       | CH 11 LOW  |  |

|                                                                     | 11  | CH 10 HIGH | •     | CH 10 LOW  |  |

|                                                                     | 10  | CH 09 HIGH |       | CH 09 LOW  |  |

|                                                                     | 9   | CH 08 HIGH |       | CH 08 LOW  |  |

|                                                                     | 8   | CH 07 HIGH | •     | CH 07 LOW  |  |

|                                                                     | 7   | CH 06 HIGH |       | CH 06 LOW  |  |

|                                                                     | 6   | CH 05 HIGH |       | CH 05 LOW  |  |

|                                                                     | 5   | CH 04 HIGH | •     | CH 04 LOW  |  |

|                                                                     | 4   | CH 03 HIGH |       | CH 03 LOW  |  |

|                                                                     | 3   | CH 02 HIGH |       | CH 02 LOW  |  |

|                                                                     | 2   | CH 01 HIGH | AGND  | CH 01 LOW  |  |

|                                                                     | 1   | CH 00 HIGH |       | CH 00 LOW  |  |

| *Channel 31 and 63 LOW inputs can be jumpered individually to AGND. |     |            |       |            |  |

ABC

# Input Modes

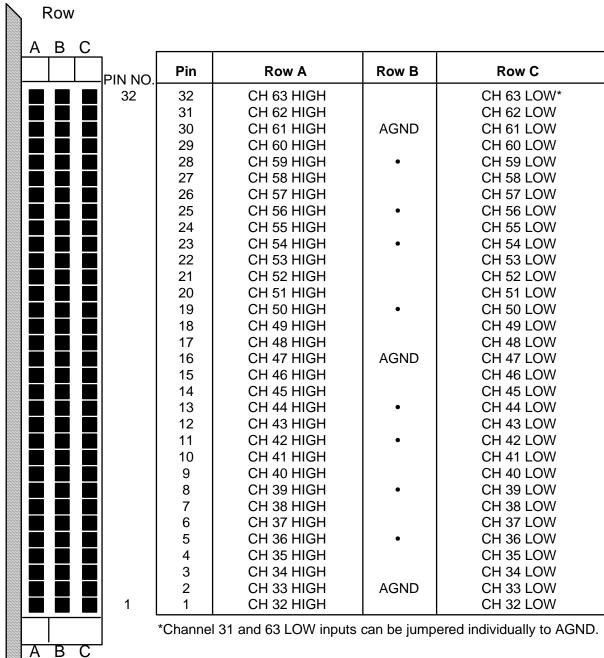

Analog inputs are connected to the board through front panel connectors P3 and P4. P4 contains the input pins for Channels 00 to 31, and P3 contains the input pins for Channels 32 to 63. Pin assignments for P3 and P4 are summarized in the table in Figure 2-6 on page 2-19 (P3) and the table in Figure 2-7 on page 2-20 (P4). The center "B" rows in P3 and P4 are connected together to AGND bus, which can be used as a guard bus for 96-wire cables. Refer to "Input Configurations" on page 2-9 and Table 2-4 on page 2-11 for **differential** input configurations.

# Cables

If 96-wire 0.033-inch ribbon cables or discrete wire type cables are used for the analog inputs, the center row can provide a ground reference to the analog return (AGND) on the board by installing Jumper J3. If 64-wire 0.050-inch ribbon cables are used, "VARI TWIST" or equivalent twisted pair cables are recommended to minimize crosstalk and induced noise. Access to AGND is available in 64-wire cables at pin C32 of P3 and P4 by installing E1-1,2 for P4, or E2-1, 2 for P3.

# **External Synchronization**

External TTL-level synchronization triggers are connected to the EXT STRT L input at the P2 connector (refer to "Input Configurations" on page 2-9). The EN EXT STRT H output is a flag to the triggering device that the Analog-to-Digital Converter Board is ready to accept an external trigger. To synchronize multiple Analog-to-Digital Converter Boards together, connect the TRIG OUT H output from the designated "master" board to the EXT STRT L input of all boards to be synchronized to the master.

# System Considerations

# **Applications with Signal Conditioning Boards**

The Analog-to-Digital Converter Board serves as a multiplexer/digitizer for signal conditioning boards. The output connectors on the signal conditioning boards are configured to cable directly to either P3 or P4 on the Analog-to-Digital Converter Board.

When used with signal conditioning boards, the Analog-to-Digital Converter Board is configured with differential inputs. These applications use a 500 Hz input filter.

# **Operation with Direct Analog Inputs**

When used without signal conditioning input boards, the Analog-to-Digital Converter Board provides direct full scale input ranges from  $\pm 250$  mV to  $\pm 10$  V.

The input filter for these applications is the 500 Hz filter. To minimize the effects of direct input multiplexing, the inputs on the Analog-to-Digital Converter Board are buffered using op-amps. The buffers supply a constant low impedance to the Programmable Gain Amplifier (PGA) regardless of the varying source impedance. Use the lowest input gain and the largest block size (see Interval Timer Register 1 (TR1) in Chapter 3) that are practical for the application.

If inputs are obtained directly from remote sources, the grounding scheme used can have a major effect on system performance. Each system has its own unique interference considerations, but the following general guidelines will apply in most cases.

- **Long Input Lines:** Long input lines (greater than 10 feet), or inputs from grounded sources (sources which are not floating), should be connected to differential inputs, and overall shields should be extended from the input sources to as close to the board as possible.

- **Source Impedance:** Use signal sources with the lowest available source impedances. Susceptibility to crosstalk and induced interference increases as the source impedance increases.

- Floating Signal Sources: The shield from a floating signal source (RTD, strain gage, etc.) should be connected to the LOW (negative) terminal at the source. For low impedance sources (less than 10), or for sources which are protected from interference fields, connect the board end of the shield to analog return (AGND) at the board. For high impedance sources, connect all shield terminals of the sources together, and leave the board ends of the shields open.

- **Grounded Signal Sources:** Outputs of grounded sources (sources which are not floating) must be referenced to a common ground which ensures that the input voltage will not exceed the input range (±10 V) of the board. Shields from grounded sources should be connected to the LOW terminal of the sources, and left open at the board.

- Unused Inputs: Unused inputs within each group of eight channels (0 through 7, 8 through 15, etc.) should be connected to a common ground to avoid interference with active channels. Grounding of unused 8-channel groups is not essential, but will assist in minimizing susceptibility to system noise.

# Chapter 3

# Chapter | Programming

This chapter gives programming instructions for the Analog-to-Digital Converter Board, and is divided into the following sections:

- Introduction to Controlling the Analog-to-Digital Converter Board

- General Control Features

- Control Registers

- Timer/Counter Control General Characteristics

- Data Organization and Control

- Operating Modes

- Bus Interrupter

- Typical Programming Examples

# Introduction to Controlling the Analog-to-Digital Converter Board

VMEbus communication takes place through Control/Status, Configuration, and Data registers which can be jumper located in either the A16 short I/O space, the A24 standard space, or the A32 extended address space. A resident bus interrupter is under program control and can be configured to generate any interrupt request from IRQ1 through IRQ7.

Digitized input data is accumulated in a dual port data buffer which consists of from 16 to 1,024 data words, where each data word contains the 16-bit digitized value of a single analog input channel. Data accumulates in the buffer in selectable blocks of 1, 8, 16, 32, or 64 input channels. Buffer size and block size both are under program control, and the buffer can be read at any time without affecting the scanning sequence.

Data scaling is adjustable with jumper-controlled voltage ranges. Channel gain is software programmable and can be fixed at x1 or x10 or can be set in the Auto Gain mode which uses the gain buffer. A data ready flag can be programmed to occur when the buffer is either full or half-full. An interrupt can be generated simultaneously with the data ready flag, or after a specific number of samples have been acquired.

The analog inputs can be scanned continuously or in triggered data bursts. Bursts (single scans) can be acquired automatically at intervals up to 687 seconds, or can be triggered by an external event. Single channel random access is also supported. Various block size/buffer size combinations are available to add versatility to the board.

References to programming jumpers are made throughout this chapter. Jumper installation requirements are described in Chapter 2.

General Control Features

# **Addressing Modes and Board Location**

Programmable address jumpers permit the Analog-to-Digital Converter Board to be located in either the short I/O (A16) space, the standard address (A24) space, or the extended address (A32) space.

The board can be located on any 2048-word boundary. Access privilege is jumper-designated as supervisory, nonprivileged, or either supervisory or nonprivileged.

# **Data Transfers**

Data transfers respond to both D8 (EO) and D16 transfers.

Any register or buffer location can be read at any time without affecting the existing scanning sequence.

### **Reset Operations and Initialization**

All Control Registers are reset by a VMEbus system reset. All control registers except Interrupt Control Register (ICR) and Interrupt Vector Register (IVR) are reset by writing to location \$000C. Either reset operation initializes the board to the following configurations:

- Continuous scanning operating mode at 100 kHz rate (must be immediately reconfigured to 50 kHz)

- Block size (64 for 32-channel board, 16 for 16-channel board)

- Data word buffer size (64 for 32-channel board, 16 for 16-channel board)

- Automatic gain set to x1

- Offset binary data coding

- Self-test LED ON

- Data Ready flag at end-of-buffer

The Analog-to-Digital Converter (ADC) will go through a calibration cycle on either a system reset or software reset. The user can initiate a calibration cycle by writing to location \$000C. The data written to this location is arbitrary. If the automatic gain mode has been selected in the Configuration Control Register, channel gains other than x1 must be programmed as described in "Gain RAM (Gain)" on page 3-23.

# **Conventions**

- Hexadecimal Notation: To be consistent with conventional VMEbus development system nomenclature, hexadecimal numbers throughout this document are indicated with the prefix "\$" unless otherwise indicated, and are expressed in byte "\$XX", word "\$XXXX" or longword "\$XXXX XXXX" formats. Decimal numbers are presented without a designating prefix.

- Logic States: This document uses the convention that a data bit or control line is "SET" when it is in the "1", or HIGH state, and is "CLEARED" when "0" or LOW.

# Control Registers

Register designations and locations are summarized in Table 3-1 below.

| Register Address (Hex) | Register Designation           | DESIG | Access |

|------------------------|--------------------------------|-------|--------|

| \$0000                 | Board Identification Register  | BIR   | R      |

| \$0002                 | Control and Status Register    | CSR   | R/W    |

| \$0004                 | Configuration Control Register | CCR   | R/W    |

| \$0006                 | Rate Control Register          | RCR   | R/W    |

| \$0008                 | Interrupt Control Register     | ICR   | R/W    |

| \$000A                 | Interrupt Vector Register      | IVR   | R/W    |

| \$000C                 | Software Reset Command         | SRC   | W      |

| \$000E                 | Software Trigger Command       | STC   | W      |

| \$0010                 | Auto Gain                      | GAIN  | R/W    |

| \$0012 to 001E         | Reserved                       | -     | N/A    |

| \$0020                 | Interval Timer 0 Register      | TR0   | R/W    |

| \$0022                 | Interval Timer 1 Register      | TR1   | R/W    |

| \$0024                 | Data Counter Register          | DCR   | R/W    |

| \$0026                 | Timer Control Register         | TCR   | W      |

| \$0028 to \$007E       | Reserved                       | -     | NA     |

| \$0080 to \$087E       | Data Buffer                    | BUFF  | R/W    |

| \$0880 to \$0FFE       | Scratch Pad Memory             | RAM   | R/W    |

Table 3-1: Analog-to-Digital Converter Board Register Map Table

3

# **Board ID Register (BIR)**

The Board ID Register is a fixed, read only data register. The contents of this register identifies the Analog-to-Digital Converter Board. The board ID for the Analog-to-Digital Converter Board is \$2EXX, where XX is defined in the Table 3-3.

| Board ID Register (0ffset \$0000) Read Only, Byte/Word                                                          |   |   |   |   |   |   |   |

|-----------------------------------------------------------------------------------------------------------------|---|---|---|---|---|---|---|

| Bit 15         Bit 14         Bit 13         Bit 12         Bit 11         Bit 10         Bit 09         Bit 08 |   |   |   |   |   |   |   |

| 0                                                                                                               | 0 | 1 | 0 | 1 | 1 | 1 | 0 |

| Bit 07 | Bit 06 | Bit 05 | Bit 04 | Bit 03 | Bit 02 | Bit 01 | Bit 00 |

|--------|--------|--------|--------|--------|--------|--------|--------|

| 0      | 0      | 0      | 0      | 0      | 0      | BIR 1  | BIR 0  |

Table 3-3: Board ID Register Channel ID

| Analog-to-Digital<br>Converter Board | Number of<br>Channels | Condition               | BIR 1 | BIR 0 |

|--------------------------------------|-----------------------|-------------------------|-------|-------|

| X3X                                  | 64                    | Standard<br>Performance | 0     | 0     |

| X4X                                  | 32                    | Standard<br>Performance | 0     | 1     |

| X5X                                  | 16                    | Standard<br>Performance | 1     | 0     |

# **Control and Status Register (CSR)**

|                                                                   |     |        |    | -     |    | -      |         |        |        |               |

|-------------------------------------------------------------------|-----|--------|----|-------|----|--------|---------|--------|--------|---------------|

| Control and Status Register (0ffset \$0002) Read/Write, Byte/Word |     |        |    |       |    |        |         |        |        |               |

| Bit 15                                                            | B   | it 14  | Bi | t 13  | ]  | Bit 12 | Bit 11  | Bit 10 | Bit 09 | Bit 08        |

| LED Off                                                           | Dat | a FMT  | Tm | ode 1 | Т  | mode 0 | 32b TMR | Flag   | 0      | 0             |

| Bit 07                                                            | ,   | Bit (  | )6 | Bit   | 05 | Bit 04 | Bit 03  | Bit 02 | Bit 01 | <b>Bit 00</b> |

| CAL CMI                                                           | PLT | Data R | DY | Arm   | ed | Triged | 0       | 0      | 0      | 0             |

#### Table 3-4: Control and Status Register Bit Map

#### **Control And Status Register Bit Definitions**

| Bit 15:             | <b>LED Off</b> – A logical 1 written to this bit location causes the front panel status LED to be turned off. A logical 0 written to this bit location causes the front panel status LED to be turned on. (Default is logic 0.)                |

|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit 14:             | <b>Data Format (Data FMT)</b> – A logical 1 written to this bit location causes data to be stored in two's complement format. A logical 0 written to this bit location caused data to be stored in offset binary format. (Default is logic 0.) |

| Bits 13 through 12: | Trigger Mode control bits (Tmode [1:0]) – This field is used to select the                                                                                                                                                                     |

trigger event as shown in the Table 3-5 below. (Default is logic 00.)

#### Table 3-5: Trigger Event Modes

| Selected Trigger Event   | Tmode 1 | Tmode 0 |

|--------------------------|---------|---------|

| Software Trigger Command | 0       | 0       |

| External Trigger         | 0       | 1       |

| Interval Timer Trigger   | 1       | 0       |

| Reserved                 | 1       | 1       |

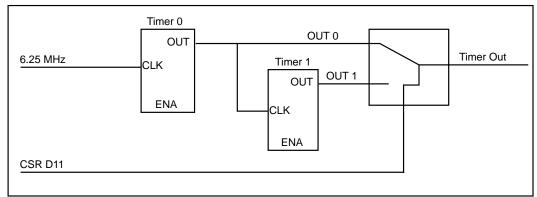

Bit 11: 32-bit Timer (32b TMR) - A logical 1 written to this bit location causes Interval Timer 1 and Interval Timer 0 to be configured as a 32-bit interval timer. A logical 0 written to this bit location enables only Interval Timer 0, providing a 16-bit interval counter. (Default is logic 0.)

Bit 10: Data Ready Flag (Flag) - A logical 1 written to this bit location causes the Data RDY flag to be activated at the middle of the data buffer. A logical 0 written to this location causes the Data RDY flag to be activated at the end of the data buffer. (Default is logic 0.)

Bits 09 through 08: **0** – Zero value.

| Bit 07:             | <b>ADC Calibration Complete (CAL CMPLT)</b> – This bit is read only. A logical 1 indicates that the ADC calibration is complete. This bit is cleared at the beginning of an ADC calibration sequence initiated by a VMEbus reset, or a Software Reset Command. |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit 06:             | <b>Data Ready</b> ( <b>Data RDY</b> ) – This bit is read only. A logical 1 indicates that the scan is complete and the data buffer is ready to be read. This bit is cleared on any read access to addresses \$0080 - \$0FFE.                                   |

| Bit 05:             | <b>Scan Mode Armed</b> ( <b>Armed</b> ) – This bit is read only. A logical 1 indicates that the current scan mode is armed. This is cleared by a valid trigger, a VMEbus reset, or a Software Reset Command.                                                   |

| Bit 04:             | <b>Triggered</b> ( <b>Triged</b> ) – This bit is read only. A logical 1 indicates that a valid trigger has been received and the current scan mode is active. This bit is cleared by scan completion, a VMEbus reset, or a Software Reset Command.             |

| Bits 03 through 00: | <b>0</b> – Zero value.                                                                                                                                                                                                                                         |

# **Configuration Control Register (CCR)**

| Configuration Control Register (Offset \$0004) Read/Write, Byte/Word |         |          |          |          |          |          |          |

|----------------------------------------------------------------------|---------|----------|----------|----------|----------|----------|----------|

| Bit 15                                                               | Bit 14  | Bit 13   | Bit 12   | Bit 11   | Bit 10   | Bit 09   | Bit 08   |

| Bufc 4                                                               | Bufc 3  | Bufc 2   | Bufc 1   | Bufc 0   | I Source | Gmode1   | Gmode 0  |

|                                                                      |         | 1        | 1        | 1        | 1        |          | r        |

| Bit 07                                                               | Bit 06  | Bit 05   | Bit 04   | Bit 03   | Bit 02   | Bit 01   | Bit 00   |

| Smode 1                                                              | Smode 0 | Groupc 5 | Groupc 4 | Groupc 3 | Groupc 2 | Groupc 1 | Groupc 0 |

Table 3-6: Configuration Control Register Bit Map

### **Configuration Control Register Bit Definitions**

| Bits 15 through 11: | <b>Buffer Configuration (Bufc [4:0])</b> – Buffer Configuration control bits.<br>This field is used to configure the available buffer size/block size combinations.                                                                                                                                                                                                                                                                                                                                                                    |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit 10:             | <b>Interrupt Request (I Source)</b> – A logical 1 written to this bit location causes a VMEbus interrupt request, when enabled, to be generated by the Data Counter. This allows an interrupt request to be generated when a programmed number of conversions have been completed. A logical 0 written to this location causes a VMEbus interrupt request, when enabled, to be generated by the Data RDY flag. This allows an interrupt request to be generated at the middle or at the end of the data buffer. (Default is logic 00.) |

| Bit 09 through 08:  | <b>Gain Mode (Gmode [1:0])</b> - Gain Mode control bits. This field is used to configure the channel gains as shown in Table 3-7 below. Fixed gains apply to all active channels. In Auto Gain mode the gain programmed into the channel x Auto Gain location is applied to channel x. (Default is logic 00.)                                                                                                                                                                                                                          |

Table 3-7: Gain Mode Channel Gains

| Gain Mode      | Gmode 1 | Gmode 0 |

|----------------|---------|---------|

| Fixed x1       | 0       | 0       |

| Fixed x10      | 0       | 1       |

| Auto Gain Mode | 1       | Х       |

Bits 07 through 06: Scan Mode (Smode [1:0]) - Scan Mode configuration control bits. This field is used to configure either the Auto Scan mode, the Single Scan mode, or the Random Access mode as shown in Table 3-8 below. In Auto Scan mode the scan is re-armed and triggered each time the end of the buffer is reached. When the end of the buffer is reached in Single Scan mode, the scan is terminated until the next trigger event. In Random Access mode, the scan is disabled. At each trigger event a single channel, indicated by Groupc [5..0], is converted and the data placed in buffer location 0 (offset address \$0080).

#### Table 3-8: Scan Mode Configuration

| Scan Mode          | Smode 1 | Smode 0 |

|--------------------|---------|---------|

| Auto Scan mode     | 0       | 0       |

| Single Scan mode   | 0       | 1       |

| Random Access mode | 1       | Х       |

**Bits 05 through 00:** Channel Group (Groupc [5:0]) – Channel group control bits. This field is used to select which group of channels will be active for scanning. It is also used to enter the desired channel in Random Access mode. If the buffer field is loaded with \$00, \$03, \$07, \$0C, \$11, or \$16 the entire buffer will be filled with the channel indicated by the group field. This is similar to Random Access, except the entire buffer is filled and not just the first location. Examples on how to use the Configuration Control Register are shown in the following paragraphs.

#### Examples on Using Configuration Control Register (CCR)

The Analog-to-Digital Converter Board has a buffer size of 1024 Words that can be accessed via the VMEbus. The configuration of this buffer may be manipulated using the Configuration Control Register located at Offset \$0004.

There are three terms used throughout this manual when discussing the configuration of the data buffer. The terms are:

| Buffer size | The VMEbus always has access to the entire set of 1024-words, but the user<br>may program the number of buffer locations that will be updated when the<br>Analog-to-Digital Converter Board makes a scan of the selected inputs. |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|             | Possible values: 16, 32, 64, 128, 256, 512, 1024.                                                                                                                                                                                |

| Block size  | The Block size is the number of active channels that will be measured<br>whenever the Analog-to-Digital Converter Board makes a scan of the selected<br>inputs.                                                                  |

|             | Possible values:                                                                                                                                                                                                                 |

|             | • 1, 8, 16 whenever the buffer size = $16$ .                                                                                                                                                                                     |

|             |                                                                                                                                                                                                                                  |

- 1, 8, 16, 32 whenever the buffer size = 32.

- 1, 8, 16, 32, 64 whenever the buffer size = 64 or larger.

Active Channels The group of active channels that will be measured whenever the Analog-to-Digital Converter Board makes a scan of the selected inputs.

Possible values:

- Any channel whenever the block size = 1.

- 0-7, 8-15, 16-23, 24-31, 32-39, 40-47, 48-55, 56-63 whenever the block size = 8.

- 0-15, 16-31, 32-47, 48-63 whenever the block size = 16.

- 0-31, 32-63 whenever the block size = 32.

- 0-63 whenever the block size = 64.

The user may find the following to be of help when programming the buffer configuration of the Analog-to-Digital Converter Board.

The following legend applies.

- 1: This bit must be set to 1.

- 0: This bit must be set to 0.

- I: This bit must be set as described under interrupt source.

- G: The bit shown must be set as described under gain settings.

- S: The bit shown must be set as described under scan mode.

- C: The bits shown are utilized whenever a single channel is active, insert the channel number in HEX in these places.

- X: The bit shown is a don't care, it may be set to a 1 or a 0.

- A: Valid for 64-channel board.

- B: Valid for 32-channel board.

- C: Valid for 16-channel board.

#### **Buffer Size 16 Words**

The following values will be used whenever programming the Analog-to-Digital Converter Board to fill a buffer of 16 words with data from a single channel. The user must specify the desired channel in the lower six bits of the register.

Block size of 1. 0000 0IGG SSCC CCCC

The following values will be used whenever programming the Analog-to-Digital Converter Board to fill a buffer of 16 words with data from a block of 8 active channels. The user must specify which block of channels are active in the lower three bits of the register.

Block size of 8:

| 0000 1IGG SSXX X000 | channels 0 through 7 are active. (A,B,C)  |

|---------------------|-------------------------------------------|

| 0000 1IGG SSXX X001 | channels 8 through 15 are active. (A,B,C) |

| 0000 1IGG SSXX X010 | channels 16 through 23 are active. (A,B)  |

| 0000 1IGG SSXX X011 | channels 24 through 31 are active. (A,B)  |

| 0000 1IGG SSXX X100 | channels 32 through 39 are active. (A)    |

| 0000 1IGG SSXX X101 | channels 40 through 47 are active. (A)    |

| 0000 1IGG SSXX X110 | channels 48 through 55 are active. (A)    |

| 0000 1IGG SSXX X111 | channels 56 through 63 are active. (A)    |

The following values will be used whenever programming the Analog-to-Digital Converter Board to fill a buffer of 16 words with data from a block of 16 active channels. The user must specify which block of channels are active in the lower three bits of the register.

Block size of 16:

| 0001 0IGG SSXX X00X | channels 0 through 15 are active. (A,B,C) |

|---------------------|-------------------------------------------|

| 0001 0IGG SSXX X01X | channels 16 through 31 are active. (A,B)  |

| 0001 0IGG SSXX X10X | channels 32 through 47 are active. (A)    |

| 0001 0IGG SSXX X11X | channels 48 through 63 are active. (A)    |

|                     |                                           |

#### **Buffer Size 32 Words**

The following values will be used whenever programming the Analog-to-Digital Converter Board to fill a buffer of 32 words with data from a single channel. The user must specify the desired channel in the lower six bits of the register.

Block size of 1. 0001 1IGG SSCC CCCC

The following values will be used whenever programming the Analog-to-Digital Converter Board to fill a buffer of 32 words with data from a block of 8 active channels. The user must specify which block of channels are active in the lower three bits of the register.

Block size of 8:

| 0010 0IGG SSXX X000 | channels 0 through 7 are active. (A,B,C) |

|---------------------|------------------------------------------|

| 0010 0IGG SSXX X001 | channels 8 through 15 are active. (A,B,C |

| 0010 0IGG SSXX X010 | channels 16 through 23 are active. (A,B) |

| 0010 0IGG SSXX X011 | channels 24 through 31 are active. (A,B) |

| 0010 0IGG SSXX X100 | channels 32 through 39 are active. (A)   |

| 0010 0IGG SSXX X101 | channels 40 through 47 are active. (A)   |

| 0010 0IGG SSXX X110 | channels 48 through 55 are active. (A)   |

| 0010 0IGG SSXX X111 | channels 56 through 63 are active. (A)   |

The following values will be used whenever programming the Analog-to-Digital Converter Board to fill a buffer of 32 words with data from a block of 16 active channels. The user must specify which block of channels are active in the lower three bits of the register.

Block size of 16:

| 0010 1IGG SSXX X00X | channels 0 through 15 are active. (A,B,C) |

|---------------------|-------------------------------------------|

| 0010 1IGG SSXX X01X | channels 16 through 31 are active. (A,B)  |

| 0010 1IGG SSXX X10X | channels 32 through 47 are active. (A)    |

| 0010 1IGG SSXX X11X | channels 48 through 63 are active. (A)    |

The following values will be used whenever programming the Analog-to-Digital Converter Board to fill a buffer of 32 words with data from a block of 32 active channels. The user must specify which block of channels are active in the lower three bits of the register.

Block size of 32:

| 0011 0IGG SSXX X0XX | channels 0 through 31 are active. (A,B) |

|---------------------|-----------------------------------------|

| 0011 0IGG SSXX X1XX | channels 32 through 63 are active. (A)  |

#### **Buffer Size 64 Words**

The following values will be used whenever programming the Analog-to-Digital Converter Board to fill a buffer of 64 words with data from a single channel. The user must specify the desired channel in the lower six bits of the register.

Block size of 1. 0011 1IGG SSCC CCCC

The following values will be used whenever programming the Analog-to-Digital Converter Board to fill a buffer of 64 words with data from a block of 8 active channels. The user must specify which block of channels are active in the lower three bits of the register.

Block size of 8:

| 0100 0IGG SSXX X000 | channels 0 through 7 are active.  | (A,B,C) |

|---------------------|-----------------------------------|---------|

| 0100 0IGG SSXX X001 | channels 8 through 15 are active. | (A,B,C) |

| 0100 0IGG SSXX X010 | channels 16 through 23 are active | . (A,B) |

| 0100 0IGG SSXX X011 | channels 24 through 31 are active | . (A,B) |

| 0100 0IGG SSXX X100 | channels 32 through 39 are active | . (A)   |

| 0100 0IGG SSXX X101 | channels 40 through 47 are active | . (A)   |

| 0100 0IGG SSXX X110 | channels 48 through 55 are active | . (A)   |

| 0100 0IGG SSXX X111 | channels 56 through 63 are active | . (A)   |

The following values will be used whenever programming the Analog-to-Digital Converter Board to fill a buffer of 64 words with data from a block of 16 active channels. The user must specify which block of channels are active in the lower three bits of the register.

Block size of 16:

| 0100 1IGG SSXX X00X | channels 0 through 15 are active. (A,B,C) |

|---------------------|-------------------------------------------|

| 0100 1IGG SSXX X01X | channels 16 through 31 are active. (A,B)  |

| 0100 1IGG SSXX X10X | channels 32 through 47 are active. (A)    |

| 0100 1IGG SSXX X11X | channels 48 through 63 are active. (A)    |

The following values will be used whenever programming the Analog-to-Digital Converter Board to fill a buffer of 64 words with data from a block of 32 active channels. The user must specify which block of channels are active in the lower three bits of the register.

Block size of 32:

| 0101 0IGG SSXX X0XX | channels 0 through 31 are active.  | (A,B) |

|---------------------|------------------------------------|-------|

| 0101 0IGG SSXX X1XX | channels 32 through 63 are active. | (A)   |

The following values will be used whenever programming the Analog-to-Digital Converter Board to fill a buffer of 64 words with data from a block of 64 active channels. The user must specify which block of channels are active in the lower three bits of the register.

Block size of 64:

0101 1IGG SSXX XXXX channels 0 through 63 are active. (A)

#### **Buffer Size 128 Words**

The following values will be used whenever programming the Analog-to-Digital Converter Board to fill a buffer of 128 words with data from a single channel. The user must specify the desired channel in the lower six bits of the register.

Block size of 1. 0110 0IGG SSCC CCCC

The following values will be used whenever programming the Analog-to-Digital Converter Board to fill a buffer of 128 words with data from a block of 8 active channels. The user must specify which block of channels are active in the lower three bits of the register.

Block size of 8:

| 0110 1IGG SSXX X000 | channels 0 through 7 are active.   | (A,B,C) |

|---------------------|------------------------------------|---------|

| 0110 1IGG SSXX X001 | channels 8 through 15 are active.  | (A,B,C) |

| 0110 1IGG SSXX X010 | channels 16 through 23 are active. | (A,B)   |

| 0110 1IGG SSXX X011 | channels 24 through 31 are active. | (A,B)   |

| 0110 1IGG SSXX X100 | channels 32 through 39 are active. | (A)     |

| 0110 1IGG SSXX X101 | channels 40 through 47 are active. | (A)     |

| 0110 1IGG SSXX X110 | channels 48 through 55 are active. | (A)     |

| 0110 1IGG SSXX X111 | channels 56 through 63 are active. | (A)     |

The following values will be used whenever programming the Analog-to-Digital Converter Board to fill a buffer of 128 words with data from a block of 16 active channels. The user must specify which block of channels are active in the lower three bits of the register.

Block size of 16:

| 0111 0IGG SSXX X00X | channels 0 through 15 are active. (A,B,C) |

|---------------------|-------------------------------------------|

| 0111 0IGG SSXX X01X | channels 16 through 31 are active. (A,B)  |

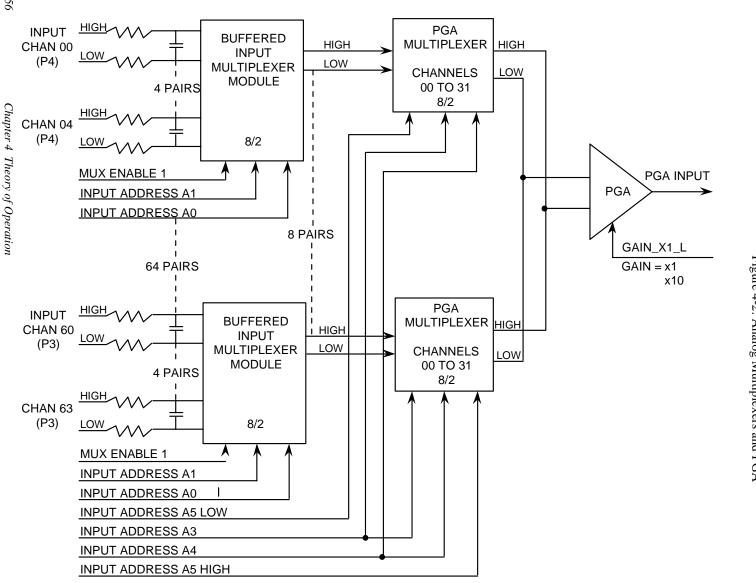

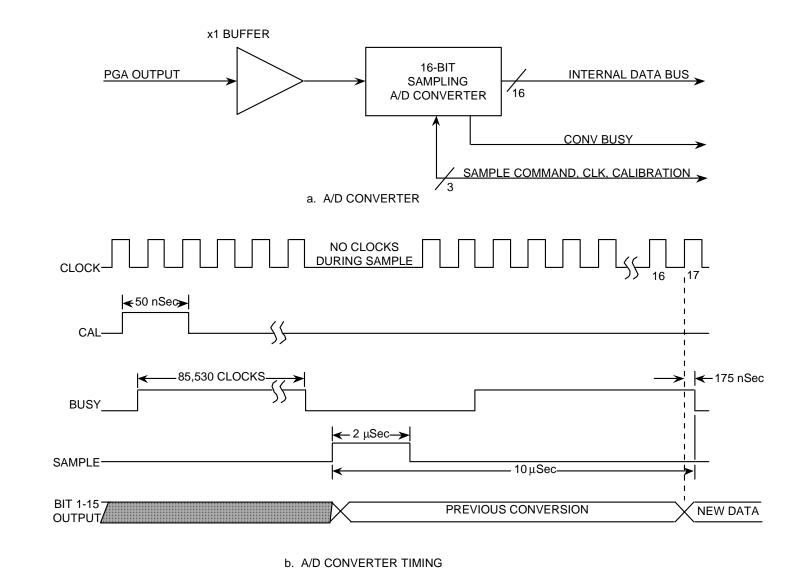

| 0111 0IGG SSXX X10X | channels 32 through 47 are active. (A)    |