# GFK-1643 New In Stock! GE Fanuc Manuals

http://www.pdfsupply.com/automation/ge-fanuc-manuals/ocs/GFK-1643

ocs 1-919-535-3180

SmartStack High Speed Counter Option

www.pdfsupply.com

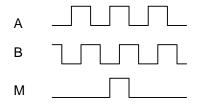

Email: sales@pdfsupply.com

## GFK-1643 New In Stock! GE Fanuc Manuals

http://www.pdfsupply.com/automation/ge-fanuc-manuals/ocs/GFK-1643

ocs 1-919-535-3180

SmartStack High Speed Counter Option

www.pdfsupply.com

Email: sales@pdfsupply.com

## Supplement for IC300HSC600 and IC300HSC601

### SmartStack™ High Speed Counter Options

October 27, 1999 GFK-1643B

### Warnings, Cautions, and Notes as Used in this Publication

Warning

Warning notices are used in this publication to emphasize that hazardous voltages, currents, temperatures or other conditions that could cause personal injury exist in this equipment or may be associated with its use.

In situations where inattention could cause either personal injury or damage to equipment, a Warning notice is used.

Caution

Caution notices are used where equipment might be damaged if care is not taken.

#### Note

Notes merely call attention to information that is especially significant to understanding and operating the equipment.

This document is based on information available at the time of its publication. While efforts have been made to be accurate, the information contained herein does not purport to cover all details or variations in hardware or software, nor to provide for every possible contingency in connection with installation, operation, or maintenance. Features may be described herein which are not present in all hardware and software systems. GE Fanuc Automation assumes no obligation of notice to holders of this document with respect to changes subsequently made.

GE Fanuc Automation makes no representations or warranty, expressed, implied, or statutory with respect to, and assumes no responsibility for the accuracy, completeness, sufficiency, or usefulness of the information contained herein. No warranties of merchantability or fitness for purpose shall apply.

The following are trademarks of GE Fanuc Automation North America, Inc.

Alarm Master CIMSTAR Helpmate PROMACRO Series Six **CIMPLICITY** Series 90 **GEnet** Logicmaster Series One CIMPLICITY 90 - ADS Genius ModelMaster Series Three VuMaster CIMPLICITY Power TRAC Genius PowerTRAC Series Five Workmaster ProLoop

The following are trademarks of Horner Electric, Inc.

Cscape SmartStack CsCAN

#### **Revisions to this Manual**

This version (GFK-1643B) of the SmartStack High Speed Counter Options User Manual contains the following revisions, additions, and deletions:

- 1. Revised parts of Safety Warnings located in Section 1.5, Section 2.1, Section 3.1.3, Section 4.1.3, 5.1.3, Section 6.1.3, Section 7.1.2, Section 8.1.2. The Safety Warnings are revised to indicate that when the OCS/RCS is in the Idle or Stop mode, the HSC600/601 continues normal operation.

- 2. Revised registers in notes located in Section 3.2.5a., item 1; Section 4.2.5a., item 1; and Section 4.4.1, item 4.

- 3. Added time base example in Section 3.3.2.

- 4. Revised Section 3.4.3 b. by changing the range of the programmable cycle time.

- 5. Revised Table 4.2, Output 5 from Setpoint 2 to Setpoint 1.

- 6. Revised register descriptions in Table 4.3, Table 4.5, Table 5.2, and Table 5.4.

#### **TABLE OF CONTENTS**

|         | ENDLY TIP FOR USING THE HSC600 / 601 SUPPLEMENT                              |     |

|---------|------------------------------------------------------------------------------|-----|

|         | 1: INTRODUCTION                                                              |     |

|         | cope                                                                         |     |

|         | otions Table                                                                 |     |

|         | onfiguration Overview                                                        |     |

| 1.3.1   | Advanced Use – Cscape Override Procedures (See Each Option)                  |     |

|         | efore Getting Started                                                        |     |

|         | afety Warning (Applies to all Options)                                       |     |

|         | 2: INITIAL CONFIGURATION                                                     |     |

| 2.1 Sa  | afety Warning                                                                | 15  |

|         | eliminary Configuration Procedures for All Options                           |     |

|         | onfiguration of HSC600/601 Modules                                           |     |

|         | 3: OPTION 1                                                                  |     |

|         | Bit Totalizer/Frequency Counter plus Dual 16-Bit PWM/Pulse Outputs           |     |

|         | otion 1 Overview                                                             |     |

| 3.1.1   | General                                                                      |     |

| 3.1.2   | Functions                                                                    |     |

| 3.1.3   | Safety Warning                                                               |     |

|         | ual 32-Bit Totalizer Counters Function – Option 1                            |     |

| 3.2.1   | Enabling the Totalizers/Counters                                             |     |

| 3.2.2   | Inputs to Totalizer Counters                                                 |     |

| 3.2.3   | Counter Input Modes – Option 1                                               |     |

| 3.2.4   | Input Signal Conditioning                                                    |     |

| 3.2.5   | Control Signals and External Inputs – Option 1                               |     |

| 3.2.6   | Totalizer Registers                                                          |     |

| 3.3 Du  | ual Channel Frequency Counter Function – Option 1                            |     |

| 3.3.1   | Channel A / Channel B                                                        |     |

| 3.3.2   | Registers                                                                    |     |

| 3.4 PV  | VM Output Counters – Option 1                                                | 25  |

| 3.4.1   | Enabling the PWM Output Counters                                             | 25  |

| 3.4.2   | Output Modes                                                                 | 25  |

| 3.4.3   | Cycle Time and ON Time                                                       |     |

| 3.4.4   | PWM Registers                                                                | 27  |

| 3.4.5   | PWM Connector                                                                |     |

| 3.4.6   | PWM Resolution                                                               |     |

| 3.5 Dir | rect I/O Function – Option 1                                                 |     |

| 3.5.1   | Registers                                                                    |     |

|         | Map - Option 1                                                               |     |

|         | onfiguration Procedures – Option 1                                           |     |

| 3.7.1   | Input Function Configuration                                                 |     |

| 3.7.2   | Input Signal Conditioning Configuration                                      |     |

| 3.7.3   | Output Function Configuration                                                |     |

| 3.7.4   | Final Configuration Steps and Viewing the I/O Map                            |     |

|         | Ivanced Use – Cscape Override Procedures                                     |     |

| 3.8.1   | General                                                                      |     |

| 3.8.2   | Overriding Cscape Parameters using a Ladder Code Program                     |     |

|         | 4: OPTION TWO                                                                |     |

|         | bit Counter with Output Latch, Pre-load Registers, and Two ON/OFF Comparison |     |

|         |                                                                              |     |

|         | otion 2 Overview                                                             |     |

| 4.1.1   | General                                                                      |     |

| 4.1.1   | Functions                                                                    |     |

| 4.1.3   | Safety Warning                                                               |     |

| 7.1.5   | carcity training                                                             | → 1 |

|                | al 32-Bit Counters (using Pre-load Register Values) Function – Option 2 | 42 |

|----------------|-------------------------------------------------------------------------|----|

| 4.2.1          | Enabling the Counters                                                   |    |

| 4.2.2          | Inputs to Counters                                                      |    |

| 4.2.3          | Counter Input Modes                                                     |    |

| 4.2.4          | Input Signal Conditioning                                               |    |

| 4.2.5<br>4.2.6 | Control Signals and External Inputs                                     |    |

| 4.2.6<br>4.2.7 | Pre-load Register Values ON/OFF Comparison Output Circuits              |    |

| 4.2.7<br>4.2.8 | Counter Registers                                                       |    |

| 4.2.6<br>4.2.9 | Direct I/O – Option 2                                                   |    |

|                | Map – Option 2                                                          |    |

|                | riguration Procedures - Option 2                                        |    |

| 4.4.1          | 32-Bit Counter Function Configuration                                   |    |

| 4.4.2          | Input Signal Conditioning Configuration                                 | 51 |

| 4.4.3          | Output Function Configuration                                           |    |

| 4.4.4          | Final Configuration Steps and Viewing the I/O Map                       | 51 |

|                | anced Use – Cscape Override Procedures                                  |    |

| 4.5.1          | General                                                                 |    |

| 4.5.2          | Overriding Cscape Parameters using a Ladder Code Program                | 52 |

|                | : OPTION 3                                                              |    |

|                | etronic Cam with Eight Combinable ON and OFF Functions                  |    |

| •              | ion 3 Overview                                                          |    |

| 5.1.1          | General                                                                 |    |

| 5.1.2          | Functions                                                               |    |

| 5.1.3          | Safety Warning                                                          |    |

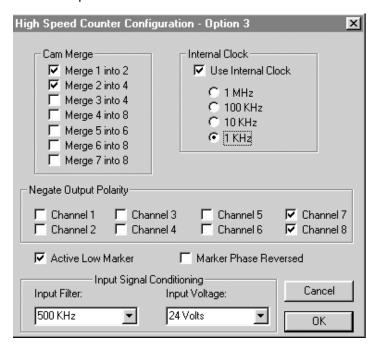

| 5.2 Elec       | ctronic Cam Function – Option 3                                         |    |

| 5.2.1<br>5.2.2 | Cam Operation                                                           |    |

| 5.2.2<br>5.2.3 | Connector                                                               |    |

| 5.2.3<br>5.2.4 | Cam Registers – Option 3                                                |    |

|                | ect I/O Function                                                        |    |

|                | Map – Option 3                                                          |    |

|                | ion 3 Configuration Procedures                                          |    |

|                | anced Use – Cscape Override Procedures                                  |    |

| 5.6.1          | General                                                                 | 69 |

| 5.6.2          | Overriding Cscape Parameters using a Ladder Code Program                |    |

|                | : OPTION 4                                                              | 73 |

|                | t Electronic Cam with Four Combinable ON and OFF Functions per Cam      |    |

|                | ion 4 Overview                                                          |    |

| 6.1.1          | General                                                                 |    |

| 6.1.2          | Functions                                                               |    |

| 6.1.3          | Safety Warning                                                          |    |

|                | ctronic Cam Function – Option 4                                         |    |

| 6.2.1<br>6.2.2 | Cam Operation                                                           |    |

| 6.2.2<br>6.2.3 | Set-points – Option 4                                                   |    |

| 6.2.3<br>6.2.4 | Connector                                                               |    |

|                | ect I/O – Option 4                                                      |    |

|                | Map – Option 4                                                          |    |

|                | ion 4 Configuration Procedures                                          |    |

|                | anced Use – Cscape Override Procedures                                  |    |

| 6.6.1          | General                                                                 |    |

| 6.6.2          | Overriding Cscape Parameters using a Ladder Code Program                |    |

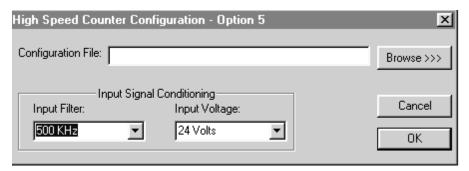

|                | : OPTION 5                                                              |    |

|                | llable Options                                                          |    |

|                | ion 5 Overview                                                          |    |

|                |                                                                         |    |

| 7.1.1 General                                                  |     |

|----------------------------------------------------------------|-----|

| 7.1.2 Safety Warning                                           | 89  |

| 7.2 Function / Installation of a Custom Option – Option 5      | 89  |

| 7.3 Registers – Option 5                                       |     |

| 7.3.1 System I/O Registers                                     |     |

| 7.3.2 Standard I/O Registers                                   |     |

| 7.4 I/O Map – Option 5                                         |     |

| 7.5 Advanced Use – Cscape Override Procedures                  |     |

| 7.5.1 General                                                  | 94  |

| 7.5.2 Overriding Cscape Parameters using a Ladder Code Program | 94  |

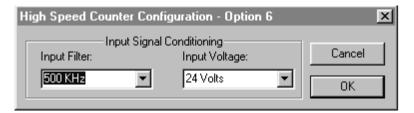

| CHAPTER 8: OPTION 6                                            |     |

| Diagnostic Tool                                                |     |

| 8.1 Option 6 Overview                                          |     |

| 8.1.1 General                                                  |     |

| 8.1.2 Safety Warning                                           |     |

| 8.2 Function                                                   |     |

| 8.3 Direct I/O Function and Registers – Option 6               |     |

| 8.4 System I/O Function and Registers                          |     |

| 8.5 I/O Map – Option 6                                         |     |

| 8.6 Option 6 Configuration Procedures                          |     |

| 8.7 Advanced Use – Cscape Override Procedures                  |     |

| 8.7.1 General                                                  |     |

| 8.7.2 Overriding Cscape Parameters using a Ladder Code Program | 101 |

| INDEX                                                          |     |

|                                                                |     |

#### USER FRIENDLY TIP FOR USING THE HSC600 / 601 SUPPLEMENT

In many instances, the user needs to only use **three** chapters in the *SmartStack*™ *High Speed Counter Options Supplement* for the HSC600 / 601:

- 1. Chapter 1 lists the six options that are available.

- **2.** Chapter 2 provides initial configuration procedures (using Cscape Software) that leads the user to the Options Screen.

- 3. Upon selecting an option, consult the Table of Contents to determine which chapter the option is located in. Each option has its own dedicated chapter and covers items such as:

- a. Functions and capabilities; pin-out

- b. Registers

- c. I/O Map shows functions that are mapped between the HSC600/601 and the ladder code in the OCS/RCS.

- d. Configuration procedures

- e. Advanced Use-Cscape Override Configuration Procedures used only for applications needing to override the Cscape setup during runtime. Not used in most applications.

**NOTES**

#### **CHAPTER 1: INTRODUCTION**

#### 1.1 Scope

The supplement for the SmartStack™ High Speed Counter Options covers the six functional options of the HSC600/HSC601 and provides configuration procedures using Cscape Software. Chapter One provides general information, and Chapter Two covers the initial configuration procedures that must be performed to select an option. The remaining chapters provide operational information and configuration procedures that are specific to each option. Each option has its own dedicated chapter.

#### 1.2 Options Table

Table 1.1 lists the six options that the HSC600/HSC601 can be configured to function as:

|          | Table 1.1 – Options for HSC600 and HSC601                                                                   |  |  |  |  |  |  |  |  |  |

|----------|-------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|

| Option # | Description                                                                                                 |  |  |  |  |  |  |  |  |  |

| 1        | Dual 32-Bit Totalizer/Frequency Counter plus Dual 16-bit PWM/Pulse Outputs                                  |  |  |  |  |  |  |  |  |  |

| 2        | Dual 32-Bit Counter with Output Latch, Pre-load Register and Two ON and OFF Comparison Outputs per Counter. |  |  |  |  |  |  |  |  |  |

| 3        | 24-bit Electronic Cam with 8 Combinable ON and OFF Functions.                                               |  |  |  |  |  |  |  |  |  |

| 4        | Dual 16-Bit Electronic Cams with 4 Combinable ON and OFF Functions per Cam.                                 |  |  |  |  |  |  |  |  |  |

| 5        | Field Installable Option. (Cscape uses an external file to specify the counter function.)                   |  |  |  |  |  |  |  |  |  |

| 6        | Diagnostic Tool Option. (This option Is intended for hardware testing only.)                                |  |  |  |  |  |  |  |  |  |

#### 1.3 Configuration Overview

The SmartStack™ High Speed Counter (HSC600/HSC601) offers a wide range of functional options for a variety of applications. One of six options is selectable during the configuration process using Cscape Software. The option selected determines the types of functions that the HSC can be configured for.

Upon choosing an option, additional selections are required to further define how the HSC600/601 functions. Using the Cscape Configuration screen, the user sets input and output parameters as well as other types of variables depending upon the option selected.

#### 1.3.1 Advanced Use – Cscape Override Procedures (See Each Option)

Note: The Cscape Override procedures are <u>not</u> intended for most applications and are recommended only for applications that require parameter changes during runtime.

Most application requirements are met using the standard Cscape configuration procedures described for each option in corresponding chapters throughout the supplement. The Cscape parameters remain the same (or are static) during runtime. However, there are some applications where it may be necessary to override the Cscape setup during runtime. Such applications are dynamic in that the parameters are changed while the program is executing. The HSC600/601 gives the user the flexibility of writing a ladder code program to allow a change to the Cscape parameters during runtime. Cscape Override configuration procedures are available for several of the six options and are located at the end of each applicable option chapter.

Note: Even if the user intends to change only one register using Cscape Override Procedures, then ALL registers must be configured from the ladder code as specified in the Cscape Override section for that option.

#### 1.4 Before Getting Started

- a. Wiring diagrams, specifications, and other pertinent information for the HSC600/601 are covered in individual data sheets created for each SmartStack Module. The SmartStack Module Supplement (GFK-1601) contains all of the data sheets and is periodically revised to reflect updates and changes.

- b. Installation and configuration procedures that are common to <u>all</u> SmartStack Modules are contained in the Control Station Hardware Manual (GFK-1631).

#### 1.5 Safety Warning (Applies to all Options)

Warning: Failure to disable the High Speed Counter Module (HSC600/601) manually through the ladder code program could cause either personal injury or damage to equipment.

When the OCS/RCS is in the Idle or Stop modes, the HSC600/601 continues normal operation. The user must physically disable the HSC600/601 through the ladder code program.

#### **CHAPTER 2: INITIAL CONFIGURATION**

#### 2.1 Safety Warning

Warning: Failure to disable the High Speed Counter Module (HSC600/601) manually through the ladder code program could cause either personal injury or damage to equipment.

When the OCS/RCS is in the Idle or Stop modes, the HSC600/601 continues normal operation. The user must physically disable the HSC600/601 through the ladder code program.

#### 2.2 Preliminary Configuration Procedures for All Options

The following procedures are used to select one of the six options. After an option is selected, read the chapter that is dedicated to the particular option. Each option chapter provides operational information and additional configuration procedures.

The SmartStack configuration is accomplished through the Configure Controller Type Dialog.

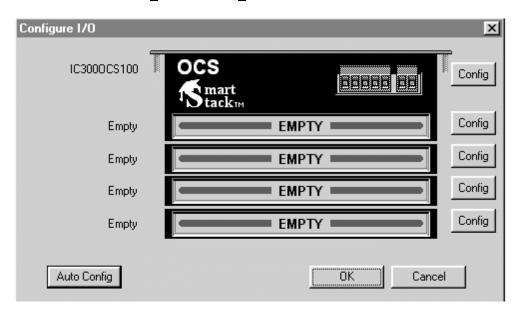

1. From the Main Menu, select Controller | Configure for the following dialog:

Figure 2.1 - Configure Controller Type Dialog

**Note:** Ensure that the proper controller is selected. If it is <u>not</u> selected, double-click on the box and select the desired controller from the pull-down menu. Press the OK button .

If the OCS/RCS has one or more SmartStack™ Modules already installed, the user can use <u>AutoConfig</u> to determine and set the I/O automatically. If the controller is <u>not</u> physically attached to Cscape or its SmartStack™ Modules are not available, use the manual configuration.

The user can choose to do the following:

a. Add a SmartStack I/O Module

**Caution:** For proper functioning and to avoid possible damage, do <u>not</u> install more than four SmartStack™ Modules per controller

1. To place a SmartStack I/O module into an EMPTY slot, ADD the module. From the CONFIGURE I/O Dialog, click on the CONFIG button to the right of the desired module or double-click on the empty slot.

Either method will invoke the SmartStack Module Selection Dialog:

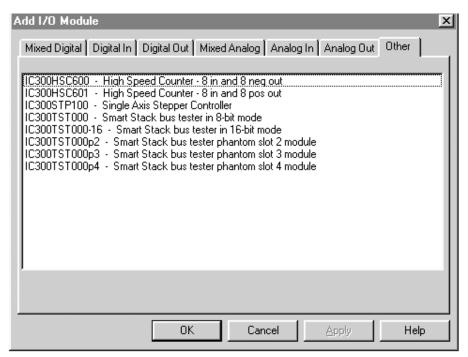

Figure 2.2 – Add I/O Module Screen ("Other" selections are shown.)

- 2. Use the mouse to select the type of module desired. The HSC600/601 is a specialty module. Select the **Other** Tab. Select the desired module, and click the OK button.

- b. Delete a SmartStack Module

If the desired SmartStack slot shows a module already installed, the module can be deleted.

- 1. Right-click on the picture of the configured slot. A floating menu appears.

- 2. From the menu, click on DELETE MODULE.

#### Select a Different SmartStack Module

If the desired SmartStack slot shows a module already installed, the module can be replaced with a different module.

- 1. Right-click on the picture of the configured slot. A floating menu appears.

- 2. From the menu, click on 1. REPLACE MODULE. This invokes the SmartStack Module Selection Dialog.

#### 2.3 Configuration of HSC600/601 Modules

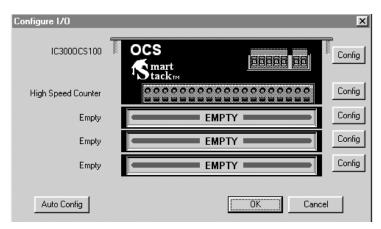

The screen now depicts the controller and HSC SmartStack Module that has been chosen by the user. The desired module is ready to be configured.

1. Double-click on the picture of the module or click on the Config button just to the right of the picture.

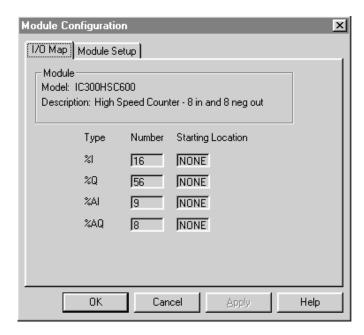

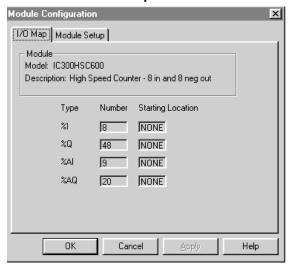

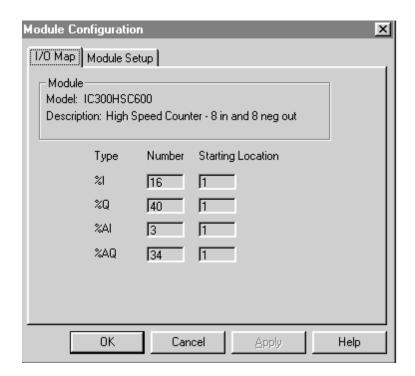

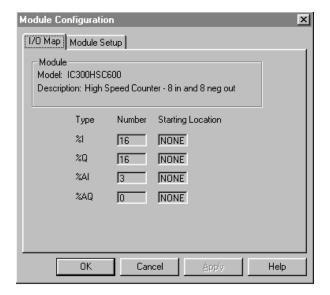

Figure 2.3 - Configure I/O Screen

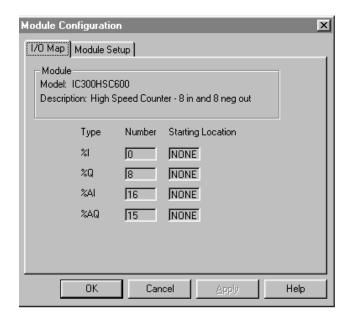

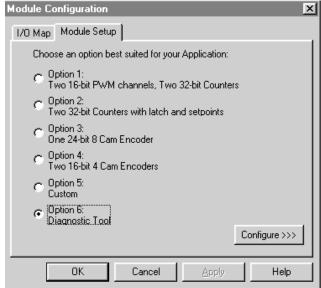

The Module Configuration Screen appears. Two tabs are available for selection.

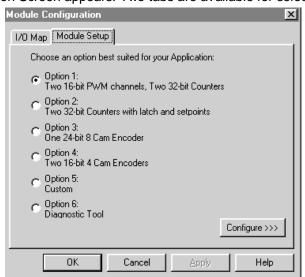

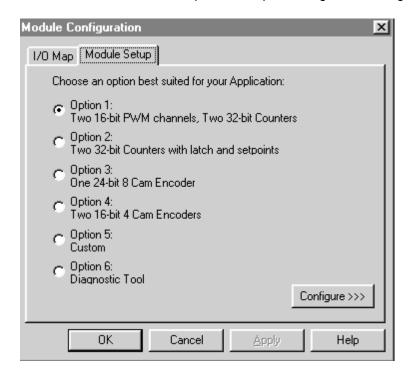

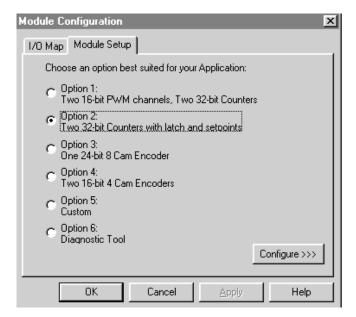

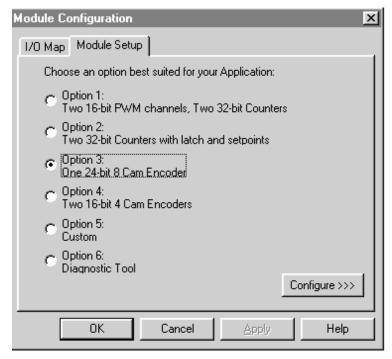

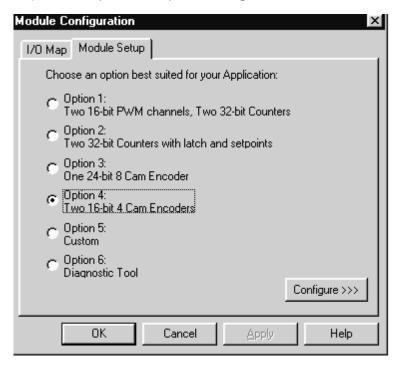

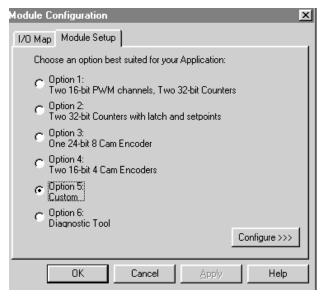

Figure 2.4 - Module Configuration Screen ("Module Setup" Tab Selected)

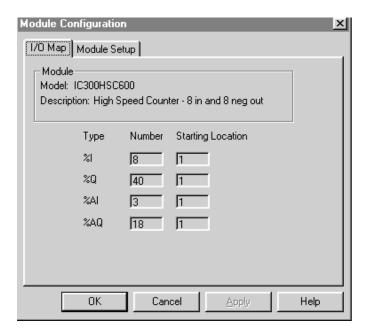

a. I/O Map Tab (Screen Not Shown)

The I/O Map describes which I/O registers are assigned to a specific SmartStack™ Module. Although there are no user-defined parameters, the I/O Map needs to be viewed <u>after</u> an option is selected and configured to determine where the module is located in the point map. *Once an option has been configured, the Module Configuration screen reappears, and the user can then select the I/O Map tab to review the settings.*

b. Module Setup Tab

Upon pressing the Module Setup Tab, the Figure 2.4 appears:

- 1. Select an option.

- 2. Once an option is selected, check the table of contents for the chapter that covers the option. Each option has its own dedicated chapter that provides operational information and additional configuration procedures for that option.

#### **CHAPTER 3: OPTION 1**

#### **Dual 32-Bit Totalizer/Frequency Counter plus Dual 16-Bit PWM/Pulse Outputs**

#### 3.1 Option 1 Overview

#### 3.1.1 General

Initial configuration procedures to select Option 1 are contained in Chapter Two. The following topics pertaining to Option 1 are covered in Chapter Three:

- a. Functions and capabilities; pin-out

- b. Registers

- c. I/O Map shows functions that are mapped between the HSC600/601 and the ladder code in the OCS/RCS.

- d. Configuration procedures

- e. Advanced Use-Cscape Override Configuration Procedures used <u>only</u> for applications needing to override the Cscape setup during runtime. Not used in most applications.

#### 3.1.2 Functions

Option 1 gives the HSC600/601 the capabilities to:

- a. Operate as Dual 32-Bit Totalizer Counters with output latches. Each input counter is placed in one of four possible input modes. The input counters can be configured independently.

- b. Perform as a Frequency Counter. Both input counters (Channel A and Channel B) on the HSC module are used for this function. Frequency can be measured for Channel A or Channel B or for both channels alternately. The HSC can <u>not</u> operate as a Dual 32-Bit Totalizer Counter when configured for this function.

- c. Act as Dual 16-bit PWM/Pulse *Output* Counters. Each Pulse Width Modulator/Pulse Output counter (PWM) can be configured independently. The PWM *Output* Counters are independent of the Totalizer *Input* Counters.

- d. Allow Direct I/O Access: Eight inputs and eight outputs are directly accessible in the %I and %Q registers of the Operator Control Station (OCS/RCS).

The functions of Option 1 are covered in greater detail in Sections 3.2 - 3.5.

#### 3.1.3 Safety Warning

Warning: Failure to disable the High Speed Counter Module (HSC600/601) manually through the ladder code program could cause either personal injury or damage to equipment.

When the OCS/RCS is in the Idle or Stop modes, the HSC600/601 continues normal operation. The user must physically disable the HSC600/601 through the ladder code program.

#### 3.2 Dual 32-Bit Totalizer Counters Function – Option 1

#### 3.2.1 Enabling the Totalizers/Counters

The HSC operates as two 32-Bit Totalizer Counters with output latches. Inputs to the HSC are counted/totaled. If this function is desired, one or both of the counters must be enabled during configuration by placing a checkmark in the box next to the applicable counter. One of four possible input modes must be selected for each enabled counter. If both counters are enabled, they can be configured independently of each other. The modes for each counter can differ.

Note: If this function is selected, the HSC can not function as a Frequency Counter.

#### 3.2.2 Inputs to Totalizer Counters

Each counter has the following inputs:

- 1. Clock / Count Up / Quadrature A

- 2. Count Direction / Count Down / Quadrature B

- 3. Count Clear Clears or resets the count or total.

- 4. Count Enable Starts the count/total.

- 5. Count Load Forces the count to a preset value

- 6. Count Latch Sends out the current counter value in the Read register.

Regardless of the input mode (discussed in the next section), each input counter has four control signals that are used to direct the counter (load, latch, clear and enable). All four control signals are provided to the HSC by the OCS/RCS or two of the signals can be provided as external inputs. Control signals and external inputs are explained in more detail in **Section 3.2.5**.

#### 3.2.3 Counter Input Modes – Option 1

One of four possible input modes must be selected for each enabled counter.

#### a. Totalizer Mode

The Totalizer Mode is used in applications that require counting either up or down. An example application is counting items on a production line. The following description explains how the inputs are used for this mode.

The Totalizer counts on each positive **Clock** edge. The **Clock Direction** input causes an up-count (when the input is a logic high) and a down-count (when the input is a logic low).

The **Direction** input of the counter can be configured as an *external input* (no %Q registers) *or register data from the OCS/RCS* (by selecting the **Latch**, **Load**, **Clear**, **and Enable from Ladder** box on the configuration screen). A Load value can be written to the Load Register, and the counter reloads its count to this value when the **Count Load** input is a logic high. The Counter remains at the load value while the **Count Load** input is held at logic high. Counting starts at a logic low. The Counter rolls over at 0 on a down-count and 4,294,967,296 on an up-count. **Count Clear** sets the counter to zero, and **Count Latch** latches a snap-shot of the count value. The **Count Enable** is used to enable/disable counting.

#### b. Up/Down Mode

The Up/Down Mode is used in applications that require counting up <u>and</u> down. An example application is counting items in a hopper as items are added (count up) and subtracted (count down). The following description explains how the inputs are used in for this mode.

The UP/DOWN counter operates much the same as the Totalizer with the **Clock** and **Direction** inputs conditioned as Clock-Up and Clock-Down inputs. The normal **Clock** input becomes Clock Up and the normal Direction input becomes Clock Down. A Load value can be written to the Load Register, and the counter reload its count to this value when the **Count Load** input is at logic high. The counter remains at the load value while the **Count Load** input is held at logic high. Counting starts at a logic low. The counter rolls over at 0 on a down-count and 4,294,967,296 on an up-count. **Count Clear** sets the counter to zero and **Count Latch** latches a snap-shot of the Count value. The **Count Enable** is used to enable/disable counting.

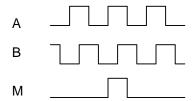

#### c. Quadrature Mode

The Quadrature Mode is used in applications where it is necessary to know the position of a motor and the direction/distance it has moved. An example application is the tracking of a rotary encoder. The following description explains how the inputs are used in for this mode.

The Quadrature Counter operates much the same as the Totalizer but it also operates with the **Clock** and **Direction** inputs conditioned as Clock A and Clock B. The normal **Clock** input becomes Clock A and the normal **Direction** input becomes Clock B. The phase relationship of Clock A and Clock B determines the count direction. A Load value can be written to the Load Register and the counter reloads its count to this value when the **Count Load** input is at logic high. The Counter remains at the load value while the **Count Load** input is held at logic high. Counting starts at a logic low. The Counter rolls over at 0 on a down-count and 4,294,967,296 on an up-count. **Count Clear** sets the counter to zero and **Count Latch** latches a snap-shot of the Count value. The **Count Enable** is used to enable/disable counting.

#### d. Timer Mode

The Timer Mode is used in applications requiring time interval measurements. The following description explains how the inputs are used for this mode.

Each Counter can also be configured to operate with an internal 10MHz clock input. The **Count Direction** can be configured for external input or DIR selected by up/down buttons on the configuration menu.

#### 3.2.4 Input Signal Conditioning

Input modes are affected by how the Clock and Count Direction inputs are conditioned. Conditioning of the input signals is based upon the selections made in the **Input Signal Conditioning** section of the Cscape configuration screen for Option 1. This section allows the user to set the ON/OFF voltages and the frequency for noise filtering. The input voltage threshold and the frequency response is selected from pull-down menus.

- 3.2.5 Control Signals and External Inputs Option 1

- a. Control Signals Sent from the Ladder Logic( or from External Sources

Each input counter has four control signals that are used to direct the counter (load, latch, clear and enable). The control signals are normally provided to the HSC in one of two possible ways via selections made to the Cscape configuration screen.

1. <u>All</u> four control signals are sent to the HSC from the OCS/RCS and are under the control of the ladder program within the OCS/RCS. To use this approach, checkmark the box that is labeled **Latch, Load, Clear, Enable from Ladder** for the applicable counter on the Cscape configuration screen.

**Note:** Counter 1 uses registers %Q25-28 for Latch, Load, Clear, and Enable signals. Counter 2 uses registers %Q29-32. (See Table 3.9.)

2. Two of the four control signals are received from external sources and are configured as external inputs. The remaining two control signals are accessible via the control register (%Q) within the OCS/RCS and are under the control of the OCS/RCS ladder program.

Note: Although the remaining two control signals fall under the control of the OCS/RCS ladder program, do <u>not</u> checkmark the box labeled **Latch**, **Load**, **Clear**, **Enable from Ladder** when using external inputs.

The Cscape configuration screen shows that each input counter has two external inputs. Each external input has a pull-down menu that allows the selection of a desired control signal for that input. (Counter One uses External Inputs 3 and 4; Counter Two uses External Inputs 7 and 8.)

b. Types of Control Signals

Each counter (if enabled) is controlled by the following control signals.

CLEAR Setting the Clear signal to Logic 1 clears the counter to zero, and the count remains at zero until the Clear signal is reset to Logic 0

LOAD Setting the Load signal to Logic 1 forces the count to the Load Value. The Count remains at the Load value until the Load signal is reset to Logic 0. The count then starts from that value and increments or decrements depending on the direction of the count.

**ENABLE** Setting the Enable signal to Logic 1 allows the Counter to count. When the Enable signal is set to Logic 0, counting is inhibited.

**LATCH**The current counter value is latched into the counter's Read Register on the rising edge of the Latch signal. The counting function is <u>not</u> disturbed by the latch. The register data is <u>not</u> reloaded until the following Latch signal's rising edge appears.

c. External Input and Control Connector – Option 1

Table 3.1 shows the inputs to the connector (J3) on the HSC. Inputs 1-4 are used for Counter A, and inputs 5-8 are used for Counter B. Each counter has clock and direction inputs as well as external inputs for control signals. Again, if external inputs are selected, the remaining two control signals are accessible via the control register (%Q) within the OCS/RCS and are under the control of the OCS/RCS ladder program. Pin 9 of J3 is used for the ground reference.

| Table 3.1 – Option 1 Pin-out (J3)                            |       |       |         |         |       |       |         |         |     |  |

|--------------------------------------------------------------|-------|-------|---------|---------|-------|-------|---------|---------|-----|--|

| Name Input1 Input2 Input3 Input4 Input5 Input6 Input7 Input8 |       |       |         |         |       |       |         |         |     |  |

| Pin                                                          | 1 2   |       | 3       | 4       | 5     | 6     | 7       | 8       | 9   |  |

| Usage                                                        | CLK A | DIR A | CNTRL A | CNTRL A | CLK B | DIR B | CNTRL B | CNTRL B | GRD |  |

#### 3.2.6 Totalizer Registers

The registers used by the Totalizer Counters in the OCS/RCS are defined by Cscape in Table 3.2.

The Counter Load values are 32 bit values. Each Counter can be loaded with these values, which are typically used in count down operation. %AQ1 DWORD is the Counter A load value. %AQ3 DWORD is the Counter B load value. The Load control is used to load the values into the desired counter. A read of the %Al6 DWORD and %Al8 DWORD register returns the 32 bit counter values latched by the Latch control.

If different parameter levels are desired *during runtime* than those listed on the Option 2 configuration screen, %Q19 (MASK) must be set. (See **Advanced Use –Cscape Override Procedures** in Section 3.8.)

Note: The Cscape Override procedures are <u>not</u> intended for most applications and are recommended only for applications that require parameter changes *during runtime*.

**Note:** Table 3.2 depicts *all* registers used in Option 1 in addition to the totalizer registers. **It is important to read through this chapter to obtain information covering different kinds of registers.** For example, information pertaining to Frequency Counter registers (Section 3.3.2) and PWM registers (Section 3.4.4) can be found in the sections specified. Also, the I/O Map (Table 3.6) contains additional information regarding registers used in Option 1.

| Register                      | Table 3.2 – Totalizer / Frequency Counter Registers *  Description |  |  |  |  |  |  |  |

|-------------------------------|--------------------------------------------------------------------|--|--|--|--|--|--|--|

| %I1-8                         | Inputs 1-8                                                         |  |  |  |  |  |  |  |

| %l9                           | Gate Signal for the frequency counter.                             |  |  |  |  |  |  |  |

| %l10-11                       | Used for PWM A & B.                                                |  |  |  |  |  |  |  |

| %I10-11<br>%I12-16            | Not used.                                                          |  |  |  |  |  |  |  |

| %Q1-8                         | Outputs 1-8                                                        |  |  |  |  |  |  |  |

| %Q1-6<br>%Q9-12               |                                                                    |  |  |  |  |  |  |  |

| %Q9-12<br>%Q13-16             | Mode A – Normally masked -used during Cscape Override.             |  |  |  |  |  |  |  |

|                               | Mode B – Normally masked -used during Cscape Override.             |  |  |  |  |  |  |  |

| %Q17                          | Frequency A – Normally masked -used during Cscape Override.        |  |  |  |  |  |  |  |

| %Q18                          | Frequency B– Normally masked -used during Cscape Override.         |  |  |  |  |  |  |  |

| %Q19                          | Leave set to 0 to preserve Cscape setup. This is the MASK bit.     |  |  |  |  |  |  |  |

| %Q20-24                       | Not used.                                                          |  |  |  |  |  |  |  |

| %Q25-28                       | Control A                                                          |  |  |  |  |  |  |  |

| %Q29-32                       | Control B                                                          |  |  |  |  |  |  |  |

| %Q33-36                       | Configuration A— Normally masked -used during Cscape Override.     |  |  |  |  |  |  |  |

| %Q37-40                       | Configuration B— Normally masked -used during Cscape Override.     |  |  |  |  |  |  |  |

| %Q41                          | Trigger PWM A – Normally masked -used during Cscape Override.      |  |  |  |  |  |  |  |

| %Q42                          | Pulse PWM A– Normally masked -used during Cscape Override.         |  |  |  |  |  |  |  |

| %Q43                          | X16 PWM A– Normally masked -used during Cscape Override.           |  |  |  |  |  |  |  |

| %Q44                          | Out PWM A- Normally masked -used during Cscape Override.           |  |  |  |  |  |  |  |

| %Q45                          | Trigger PWM B- Normally masked -used during Cscape Override.       |  |  |  |  |  |  |  |

| %Q46                          | Pulse PWM B– Normally masked -used during Cscape Override.         |  |  |  |  |  |  |  |

| %Q47                          | Pulse PWM B– Normally masked -used during Cscape Override.         |  |  |  |  |  |  |  |

| %Q48                          | Out PWM B- Normally masked -used during Cscape Override.           |  |  |  |  |  |  |  |

| %Q49-50                       | V-in- Normally masked -used during Cscape Override.                |  |  |  |  |  |  |  |

| %Q51-52                       | Frequency in– Normally masked -used during Cscape Override.        |  |  |  |  |  |  |  |

| %Q53-56                       | Not used.                                                          |  |  |  |  |  |  |  |

| %AI1 WORD                     | 1 (Option number)                                                  |  |  |  |  |  |  |  |

| %AI2 DWORD                    | Channel A count or frequency low word                              |  |  |  |  |  |  |  |

| %AI3                          | Channel A count or frequency high word                             |  |  |  |  |  |  |  |

| %AI4 DWORD                    | Channel B count or frequency low word                              |  |  |  |  |  |  |  |

| %AI5                          | Channel B count or frequency high word                             |  |  |  |  |  |  |  |

| %Al6 DWORD                    | Channel A latch value low word                                     |  |  |  |  |  |  |  |

| %AI7                          | Channel A latch value high word                                    |  |  |  |  |  |  |  |

| %Al8 DWORD                    | Channel B latch value low word                                     |  |  |  |  |  |  |  |

| %AI9                          | Channel B latch value high word                                    |  |  |  |  |  |  |  |

| %AQ1 DWORD                    | Channel A frequency time base low word / Counter A Load Value      |  |  |  |  |  |  |  |

| %AQ2                          | Channel A frequency time base high word                            |  |  |  |  |  |  |  |

| %AQ3 DWORD                    | Channel B frequency time base low word / Counter B Load Value      |  |  |  |  |  |  |  |

| %AQ4                          | Channel B frequency time base high word                            |  |  |  |  |  |  |  |

| %AQ5 WORD                     | Channel A PWM cycle time                                           |  |  |  |  |  |  |  |

|                               |                                                                    |  |  |  |  |  |  |  |

|                               | Channel A pulse or PWM on time                                     |  |  |  |  |  |  |  |

| %AQ7 WORD                     | Channel B PWM cycle time                                           |  |  |  |  |  |  |  |

| %AQ8 WORD  * Channel A = Cour | Channel B pulse or PWM on time                                     |  |  |  |  |  |  |  |

| Channel A = Cour              | ter 1 Channel B = Counter 2                                        |  |  |  |  |  |  |  |

#### 3.3 Dual Channel Frequency Counter Function – Option 1

#### 3.3.1 Channel A / Channel B

Option 1 can be configured for a two-channel Frequency Counter function, which uses both counters (Channel A and Channel B). Frequency can be measured at the **A clock input**, the **B clock input** or both the **A and B clock inputs** alternately.

#### 3.3.2 Registers

The registers used by the Frequency Counters in the OCS/RCS are defined by Cscape in Table 3.2.

The time base for the Channel A measurement is loaded into %AQ1 DWORD and the time base for the Channel B measurement is loaded into %AQ3 DWORD. The gate signal is available in %I9. The frequency measurements run automatically at approximately the rate of the time base plus one scan without user intervention. The most recent input A frequency is in %AI2 DWORD, and the most recent input B frequency is in %AI4 DWORD.

#### Time base Example:

The desired output is in hertz (1 second or 1Hz). Place 10,000,000 into %AQ1 (or %AQ3) - the time base is in seconds. The frequency output in %Al2 (or %Al4) is in hertz.

#### 3.4 PWM Output Counters – Option 1

#### 3.4.1 Enabling the PWM Output Counters

Option 1 contains two Pulse Width Modulation (PWM A and PWM B) circuits that are completely independent of the Totalizer Input Counters. PWM outputs are used to vary the length of time that a device or sensor is turned ON or OFF. In PWM, a pulse train consisting of equal-width and equal-amplitude pulses is changed by varying the width of the pulses in accordance with a modulating signal.

If this function is desired, one or both of the counters must be enabled during configuration by placing a checkmark in the box next to the applicable PWM Output Counter. If both counters are enabled, they can be configured independently of each other.

#### 3.4.2 Output Modes

Two independent PWM channels are provided (PWM A and PWM B). Each output counter can be used either in the continuous PWM mode or the One Shot pulse mode. The modes for each counter can differ.

- a. The continuous PWM/pulse mode is automatically selected by Cscape unless the user checkmarks the box next to the **One Shot** option. This continuous PWM mode is normally used to control valves, motors, and other devices.

- b. The One Shot mode is a single ON pulse triggered by Channel A or Channel B's trigger (%Q41 in the PWM register). The One Shot mode generates a shorter pulse than the ladder program is able to do.

PAGE 26 27 OCT 1999 GFK-1643B

#### 3.4.3 Cycle Time and ON Time

The PWM's are configured by entering a cycle time into the registers for the applicable output counter. The cycle time allows the HSC to define the output frequency, which includes the ON time. Also, an ON time value is entered into the registers (by the user) for the applicable counter, which allows the HSC to determine the duty cycle. (See Table 3.3.)

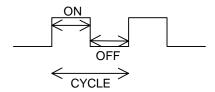

Figure 3.1 - PWM Cycle Time

#### a. Basic Calculations

Cycle Time = ON time + OFF time. Duty Cycle = ON time/Cycle Time Frequency = 1/Cycle Time.

#### **Examples:**

An ON time of 0 = 0% duty cycle An ON time of half the cycle time = 50% duty cycle An ON time equal to the cycle time = 100% Duty Cycle.

#### b. Calculating Frequency using Cycle Time

The PWM's are configured by entering a cycle time into registers %AQ5 (for PWM A) and %AQ7 (for PWM B). The PWM cycle time is programmable in 100ns increments from  $40\mu$ Sec to 3.2767mSec. The programmed value represents the number of 100ns counts for an entire cycle. Once the cycle time is entered, the frequency is determined by the HSC. There are two values that can be entered into the %AQ5 or %AQ7 registers, which have special uses: 1 and 0. See note.

#### **Example:**

A cycle time value of 1000 is entered in Register %AQ5 Cycle Time =  $1000 \times 100$ ns = 100 microsecond PWM cycle timeFrequency =  $1/\text{Cycle Time} = 1/10^{-4} = 10\text{KHz}$ .

**Note:** *Special use for 1 and 0*: A programmed value of 1 causes the internal count to remain at 0 and the PWM output to remain off. A programmed value of 0 sets the cycle time to its maximum value (6.5535ms).

**X16 Function:** A X16 function is available to multiply the PWM times by 16 and produces a longer cycle time and ON time. This yields a resolution of 1.6us and a maximum cycle time of over 100ms. The x16 function is selected using the configuration screen.

#### b. Calculating Duty Cycle using ON Time

The PWM ON time is programmable in 100ns increments from zero up to the total cycle time for 100% duty cycle.

#### **Examples:**

Duty Cycle = ON time/Cycle Time A cycle time value of 1000 is entered in Register %AQ5

ON Time entered in Register %AQ6: 0.

Duty Cycle = 0%

ON Time entered in Register %AQ6: 500.

Duty Cycle = 50%

ON Time entered in Register %AQ6: 1000.

Duty Cycle = 100%

X16 Function: The time increments are 1.6us.

3.4.4 PWM Registers

The registers used used by the PWM Output Counters in the OCS/RCS are defined in Table 3.3. . Register numbers below are referenced to the base register numbers for the HSC600 module.

The register blocks shown in white are configured by the user.

The register blocks shown in light gray are normally configured by the Cscape program. If the Cscape configuration is overridden, the user must also configure the blocks in gray. In such cases, refer to Section 3.8, which covers Cscape Override procedures.

| Table 3.3– PWM Registers |                                                                                                                                |  |  |  |  |  |  |

|--------------------------|--------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| %l10                     | PWM A signal.                                                                                                                  |  |  |  |  |  |  |

| %l11.                    | PWM B signal                                                                                                                   |  |  |  |  |  |  |

| %Q41                     | Off to On: Trigger channel A one shot pulse if enabled. On to Off: No effect. Pulse may not be retriggered until it times out. |  |  |  |  |  |  |

| %Q42                     | On: Enable channel A one shot mode (stops PWM A).  Off: Starts PWM A.                                                          |  |  |  |  |  |  |

| %Q43                     | On: Multiply channel A cycle and on times by 16. Off: Channels A times are multiples of 100ns.                                 |  |  |  |  |  |  |

| %Q44                     | On: Connect channel A signal to HE800HSC600 output 1. Off: Connect %Q1 to output 1.                                            |  |  |  |  |  |  |

| %Q45                     | Off to On: Trigger channel B one shot pulse if enabled. On to Off: No effect. Pulse may not be retriggered until it times out. |  |  |  |  |  |  |

| %Q46                     | On: Enable channel B one shot mode (stops PWM B). Off: Starts PWM B.                                                           |  |  |  |  |  |  |

| %Q47                     | On: Multiply channel B cycle and on times by 16. Off: Channels A times are multiples of 100ns.                                 |  |  |  |  |  |  |

| %Q48                     | On: Connect channel B signal to HE800HSC600 output 4. Off: Connect %Q4 to output 4.                                            |  |  |  |  |  |  |

| %AQ5                     | Channel A PWM cycle time.                                                                                                      |  |  |  |  |  |  |

| %AQ6                     | Channel A PWM or pulse on time. Should be no longer than channel A cycle time.                                                 |  |  |  |  |  |  |

| %AQ7                     | Channel B PWM cycle time.                                                                                                      |  |  |  |  |  |  |

| %AQ8                     | Channel B PWM or pulse on time. Should be no longer than channel B cycle time.                                                 |  |  |  |  |  |  |

#### 3.4.5 PWM Connector

Table 3.4 shows the outputs to the connector (J3) on the HSC. Outputs 1-4 are used for PWM A, and outputs 5-8 are used for PWM B. The PWM/pulse signals can be connected to physical outputs under program control. The PWM/pulse signals can also be read back to provide an internal timer or cycle timer function.

|      | Table3.4 – Option 1 Pinout (J3)                                              |     |     |     |       |     |     |     |     |       |

|------|------------------------------------------------------------------------------|-----|-----|-----|-------|-----|-----|-----|-----|-------|

| Name | Name   Output   Output   Output   Output   Output   Output   Output   Output |     |     |     |       |     |     |     |     |       |

|      | 1                                                                            | 2   | 3   | 4   | 5     | 6   | 7   | 8   |     |       |

| Pin  | 10                                                                           | 11  | 12  | 13  | 14    | 15  | 16  | 17  | 18  | 19    |

| Use  | %Q1                                                                          | %Q2 | %Q3 | %Q4 | %Q5   | %Q6 | %Q7 | %Q8 | GRD | Power |

|      | PWM A                                                                        |     |     |     | PWM B |     |     |     |     | Load  |

#### 3.4.6 PWM Resolution

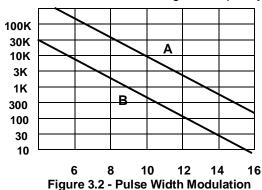

The PWM frequency is the inverse of the PWM cycle time. As discussed in Section 3.4.3, the 100ns and 1.6us PWM resolutions produce the following inverse relationships between PWM frequency and effective PWM resolution . Figure 3.2 shows the resolution achieved for a given frequency.

Pulse Width Modulation (PWM) Frequency

**Resolution in Bits**

A: Without x16

**Prescaler**

B: With x16

Prescaler

#### 3.5 Direct I/O Function – Option 1

#### 3.5.1 Registers

In the Direct I/O function, the read and write registers are directly accessible as discrete inputs and outputs are turned ON and OFF.

Eight %I and eight %Q registers are used in the Direct I/O function.

| Table 3.5 – Direct I/O Registers and Pinout |         |                               |  |  |  |  |  |  |  |

|---------------------------------------------|---------|-------------------------------|--|--|--|--|--|--|--|

| Register                                    | Signal  | Input and Output<br>Pins (J3) |  |  |  |  |  |  |  |

| %l1                                         | Input1  | 1                             |  |  |  |  |  |  |  |

| %l2                                         | Input2  | 2                             |  |  |  |  |  |  |  |

| %l3                                         | Input3  | 3                             |  |  |  |  |  |  |  |

| %l4                                         | Input4  | 4                             |  |  |  |  |  |  |  |

| %I5                                         | Input5  | 5                             |  |  |  |  |  |  |  |

| %l6                                         | Input6  | 6                             |  |  |  |  |  |  |  |

| %I7                                         | Input7  | 7                             |  |  |  |  |  |  |  |

| %l8                                         | Input8  | 8                             |  |  |  |  |  |  |  |

| %Q1                                         | Output1 | 10                            |  |  |  |  |  |  |  |

| %Q2                                         | Output2 | 11                            |  |  |  |  |  |  |  |

| %Q3                                         | Output3 | 12                            |  |  |  |  |  |  |  |

| %Q4                                         | Output4 | 13                            |  |  |  |  |  |  |  |

| %Q5                                         | Output5 | 14                            |  |  |  |  |  |  |  |

| %Q6                                         | Output6 | 15                            |  |  |  |  |  |  |  |

| %Q7                                         | Output7 | 16                            |  |  |  |  |  |  |  |

| %Q8                                         | Output8 | 17                            |  |  |  |  |  |  |  |

%I and %Q registers are connected to the input and output pins of connector J3. A Read of the %I registers returns the input pins and a write to the %Q registers latches data to the output pins. Two of the output pins (Output 1 and Output 5) can be used as PWM outputs which override the %Q register data. The Read of the %I registers returns data at the input pins regardless of the selected counter mode.

#### 3.6 I/O Map - Option 1

The I/O Map shows the functions that are mapped between the HSC600/601 and the ladder code in the OCS/RCS.

The register blocks that are shown in white are normally accessible using the ladder code. The OCS/RCS has a ladder program that the user sets parameters for. If the user does <u>not</u> set parameters for any one of these blocks, the OCS/RCS automatically writes a zero into the block.

The register blocks that are shown in light gray are automatically configured by Cscape <u>if</u> Q19 (the MASK or override bit) is set to 0. This is the normal setup for most applications. However, in dynamic applications that require parameter changes during runtime, the light gray blocks can be overridden. Refer to the final section in Chapter One, which covers Cscape Override procedures. If Cscape Override procedures are used, Q19 is set to 1.

Note: The Cscape Override procedures are <u>not</u> intended for most applications and are recommended only for applications that require parameter changes during runtime.

The dark gray blocks are not used.

| Table 3.6 – I/O Map |       |     |      |                                |             |            |            |             |          |                      |       |

|---------------------|-------|-----|------|--------------------------------|-------------|------------|------------|-------------|----------|----------------------|-------|

| %I INPUTS           |       |     |      |                                |             |            |            |             |          |                      |       |

| %l                  | 0     | 1   |      | 2                              | 3           | 4          | 5          | 6           | 7        | 8                    | 9     |

| %l 0x               |       | Inp | ut1  | Input2                         | Input3      | Input4     | Input5     | Input6      | Input7   | Input8               | GATE  |

| %l 1x               | PWMA  | PW  | /MB  |                                |             |            |            |             |          |                      |       |

| %Q OUT              | PUTS  |     |      |                                |             |            |            |             |          |                      |       |

| %Q                  | 0     | 1   |      | 2                              | 3           | 4          | 5          | 6           | 7        | 8                    | 9     |

| %Q 0x               |       | Ou  | t 1  | Out 2                          | Out 3       | Out 4      | Out 5      | Out 6       | Out 7    | Out 8                | ModeA |

| %Q 1x               | ModeA | Мо  | deA  | ModeA                          | ModeB       | ModeB      | ModeB      | ModeB       | FreqA    | FreqB                | MASK  |

| %Q 2x               |       |     |      |                                |             |            | CtrlA      | CtrlA       | CtrlA    | CtrlA                | CtrlB |

| %Q 3x               | CtrlB | Ctr | ΙB   | CtrlB                          | ConfA       | ConfA      | ConfA      | ConfA       | ConfB    | ConfB                | ConfB |

| %Q 4x               | ConfB | Tri | gA   | PulseA                         | X16A        | OutA       | TrigB      | PulseB      | X16B     | OutB                 | V-in  |

| %Q 5x               | V-in  | Fre | q-in | Freq-in                        |             |            |            |             |          |                      |       |

| Not used            |       |     |      |                                |             | Cor        | figured by | Cscape if N | MASK (%C | (19) is <u>not</u> s | set.  |

| %AI INP             | UTS   |     |      |                                |             |            |            |             |          |                      |       |

| %AI1                | WORD  |     | 1 (0 | ption numb                     | er)         |            |            |             |          |                      |       |

| %AI2                | DWORD | )   | Char | nel A cour                     | t or freque | ncy low wo | rd         |             |          |                      |       |

| %AI3                |       |     | Char | nel A cour                     | t or freque | ncy high w | ord        |             |          |                      |       |

| %AI4                | DWORD | )   | Cha  | nnel B cou                     | ınt or freq | uency low  | word       |             |          |                      |       |

| %AI5                |       |     | Char | nel B cour                     | t or freque | ncy high w | ord        |             |          |                      |       |

| %AI6                | DWORD | )   | Char | nel A latch                    | value low   | word       |            |             |          |                      |       |

| %AI7                |       |     | Char | nel A latch                    | value high  | n word     |            |             |          |                      |       |

| %AI8                | DWORD | )   | Char | nel B latch                    | value low   | word       |            |             |          |                      |       |

| %AI9                |       |     | Char | nel B latch                    | value high  | word       |            |             |          |                      |       |

| %AQ OU              | TPUTS |     |      |                                |             |            |            |             |          |                      |       |

| %AQ1                | DWORD | )   | Char | nel A frequ                    | ency time   | base low w | ord        |             |          |                      |       |

| %AQ2                |       |     | Char | nel A frequ                    | ency time   | base high  | word       |             |          |                      |       |

| %AQ3                | DWORD | )   | Char | nel B frequ                    | ency time   | base low w | ord        |             |          |                      |       |

| %AQ4                |       |     | Char | nel B frequ                    | ency time   | base high  | word       |             |          |                      |       |

| %AQ5                | WORD  |     |      | nel A PWI                      |             |            |            |             |          |                      |       |

| %AQ6                | WORD  |     |      | Channel A pulse or PWM on time |             |            |            |             |          |                      |       |

| %AQ7                | WORD  |     |      | hannel B PWM cycle time        |             |            |            |             |          |                      |       |

| %AQ8                | WORD  |     | Char | Channel B pulse or PWM on time |             |            |            |             |          |                      |       |

Note: This table serves as a general reference for the starting location of the registers. To determine the *actual* starting location of the various registers, it is necessary to consult the "I/O Map" screen in the Cscape Software *after* configuration. Refer to the following Configuration Procedures in this chapter for more details.

#### 3.7 Configuration Procedures – Option 1

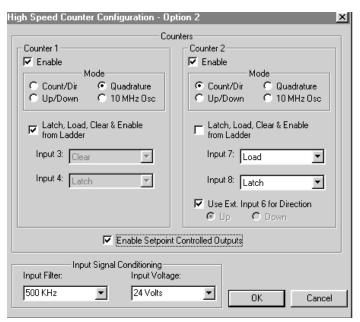

After performing the initial configuration procedures described in Chapter Two, the following procedures are provided to configure Option 1 input and output functions. Also, input signal conditioning parameters must be set including the voltage threshold and the frequency for noise filtering. It is recommended to read the operational information covered this chapter before performing the following steps.

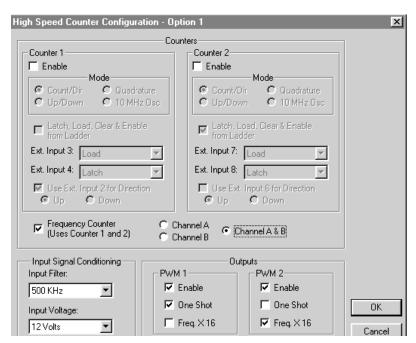

Figure 3.3 – Option 1 Selected

#### 3.7.1 Input Function Configuration

Configure the HSC600/601 for the desired input function(s). If an input function is <u>not</u> desired, the inputs are directly accessible in the OCS/RCS registers. The HSC600/601 can be independently configured as one or two Totalizer Counters <u>or</u> as a Frequency Counter. Follow the procedures specified for the desired input function.

#### a. If configuring the HSC600/601 as an Input Totalizer Counter:

(Refer to Section 3.3 for register data and other pertinent information covering the the Totalizer Counters.)

Note: For this example configuration, Counter One uses two external control signals; Counter Two uses control signals internally generated from the ladder code)

- 1. Click the Enable box located next to the desired Totalizer Counter(s). One or both counters can be enabled and can be configured independently. (See Figure 3.3.)

- 2. Select one of four possible input modes for each enabled counter: (See Section 3.2.3.)

- a. Count/Dir

- b. Up/Down

- c. Quadrature

- d. 10MHz OCS

High Speed Counter Configuration - Option 1 × Counters Counter 1 Counter 2: ▼ Enable ▼ Enable Mode Mode Count/Dir C Quadrature C Quadrature Count/Dir C Up/Down C 10 MHz Osc C Up/Down C 10 MHz Osc Latch, Load, Clear & Enable Latch, Load, Clear & Enable from Ladder from Ladder Ext. Input 3: Load Ext. Input 7: Load Ext. Input 4: Latch Ext. Input 8: Latch ✓ Use Ext. Input 2 for Direction ☐ Use Ext. Input 6 for Direction C Down C Down **⊚** Up : O Up : Frequency Counter Channel A C Channel A & B (Uses Counter 1 and 2) C Channel B Input Signal Conditioning Outputs Input Filter: PWM 1 PWM 2: ✓ Enable ▼ Enable 500 KHz One Shot Cone Shot OΚ Input Voltage:

Note: Counters One and Two do not have to be in the same mode.

12 Volts

Figure 3.4 - Totalizer Input Counters Selected

Freq. X16

3. If the **Count/Dir** mode is selected, it must be determined whether the *Direction Input* is provided via an external input. The choices for the *Direction Input* are located under the mode block for each counter on the Option 1 Screen.

If an external input is used to determine the *Direction Input* of the count (up or down): Click the box labeled **Use for Ext. Input 2 for Dir**.

Freq. X16

<u>If the *Direction Input* is configured by Cscape:</u> Select the appropriate circle labeled **Up** or **Down** to indicate the direction of the count.

Note: The *Direction Input* choices are only visible on the screen if the Count/Dir input mode is selected.

4. Select **control signals** for each enabled Totalizer Counter as discussed in Section 3.2.5. Determine whether all four control signals are wholly generated by the OCS/RCS <u>or</u> if two of the four the control signals are generated from external sources.

The Cscape configuration screen shows that each input counter has two external inputs. Each external input has a pull-down menu that allows the selection of a desired control signal for that input. (Counter One uses controls from External Inputs 3 and 4. Counter Two uses External Inputs 7 and 8.)

**Note:** External Inputs must <u>not</u> be left floating. They need to be tied to ground or plus as appropriate.

If all four control signals are sent to the HSC600/601 from the OCS/RCS and are under the control of the ladder program within the OCS/RCS: Select the box that is labeled **Latch**, **Load**, **Clear**, **Enable from Ladder** for the applicable counter on the Option 1 Screen.

**Note:** Counter 1 uses registers %Q33-36 for Latch, Load, Clear, and Enable signals. Counter 2 uses registers %Q37-40. (See Table 3.9.)

If two of the four control signals are received from external sources and are configured as external inputs: Select a control signal from the pull-down menus next to Ext. Input 3 and External Input 4 for Counter 1 (or Ext. Input 7 and Ext. Input 8 for Counter 2). The remaining two control signals are accessible via the control register (%Q) within the OCS/RCS and are under the control of the OCS/RCS ladder program.

Note: Although the remaining two control signals fall under the control of the OCS/RCS ladder program, do not click the box labeled **Latch**, **Load**, **Clear**, **Enable from Ladder** when using external inputs.

- If configuring the HSC600/601 as an Input Frequency Counter:

(Refer to Section 3.4 for register data and other pertinent information covering the Frequency Counter.)

- 1. To select the **Frequency Counter Mode**, click the box labeled **Frequency Counter** Uses Counters 1 and 2. Because both input counters (Channel A and Channel B) are required for this function, the HSC can <u>not</u> operate as a Dual 32-Bit Totalizer Counter when configured in the Frequency Counter Mode.

- 2. Select the channel(s) needing frequency measurement. The frequency can be measured for Channel A or Channel B by clicking the circle next to the desired channel. If frequency measurement is desired for both Channel A and B, click the circle that is labeled **Channel A & B**. In this case, the frequency is measured for both channels alternately. A single counter is used for frequency measurement, and the inputs are multiplexed to provide two channels of measurement. This has the effect of alternately sampling the outputs.(See Figure 3.5.)

Figure 3.5 – Frequency Input Counter Selected and Pulse Width Modulators (PWM) Enabled

#### 3.7.2 Input Signal Conditioning Configuration

- 1. The **Input Signal Conditioning** block allows the user to set the input voltage threshold and the input frequency response for noise filtering. It is located on the lower left side of the configuration screen. (See Figure 3.5.)

- 2. Using the corresponding pull-down menus, select the input voltage and the input frequency for noise filtering. (Refer to Section 3.2.4 for additional information.)

#### 3.7.3 Output Function Configuration

If desired, configure the HSC600/601 for the PWM/pulse output function. (If the PWM/pulse output function is <u>not</u> desired, the outputs are directly accessible in the OCS/RCS registers.) The HSC600/601 can be independently configured as one or two PWM/pulse Output Counters. (See Figure 3.5.)

- a. If configuring the HSC600/601 as a PWM/Pulse Output Counter:

(Refer to Section 3.4 for register data and other pertinent information covering the the PWM/pulse Output Counters.)

- 1. Click the Enable box located under the desired PWM/pulse Counter(s). One or both counters can be enabled and can be configured independently.

- 2. Select one of two possible output modes for each enabled PWM/pulse Counter: PWM 1 and PWM 2 do not have to be in the same mode. (See Section 3.4.2.)

<u>PWM/pulse Continuous Mode</u>: This mode is <u>not</u> shown on the configuration screen. *Unless the user chooses the One-Shot mode, the Continuous mode is automatically selected.*

One-Shot Mode: To select this mode, click the box labeled **One-Shot**.

#### 3.7.4 Final Configuration Steps and Viewing the I/O Map

After making desired selections, complete the final configuration procedures. It is appropriate to view the I/O Map tab after completing the configuration. The I/O Map shows the number of registers and the starting location of the registers.

- 1. Press **OK**. The screen reverts to the Module Configuration Screen.

- 2. Select the **I/O Map** tab. (See Figure 3.6.)

Note: For this configuration example, the I/O Map information shown is <u>not</u> necessarily a true representation of the registers and the starting locations. *It is important to understand how to read the information in the registers for an actual setup.*

Example: If the %I starting location = 10, then what is referred to as %I1 (in this chapter) is really %I10 in the actual I/O Map.

Figure 3.6 – I/O Map Tab

#### 3.8 Advanced Use – Cscape Override Procedures

#### 3.8.1 General

Most application requirements are met using the standard Cscape configuration procedures described earlier in this chapter. The user sets parameters using the Cscape Configuration screen, and the Cscape program has exclusive control over the application at all times. The parameters remain the same (or static) during runtime, and they do <u>not</u> change unless the user reconfigures the setup.

However, there are some applications where it may be necessary to override the Cscape configuration setup during runtime. The HSC600/601 gives the user the flexibility of writing a ladder code program to allow changes to the Cscape parameters during runtime. Such applications are dynamic in that the parameters change when the program is executing. Note that the Cscape configuration is used during power-up and continues until the program overrides the configuration.

Note: The Cscape Override procedures are <u>not</u> intended for most applications and are recommended only for applications that require parameter changes during runtime.

### 3.8.2 Overriding Cscape Parameters using a Ladder Code Program

**Note:** Even if the user intends to change only one register using Cscape Override Procedures, ALL registers must be configured from the ladder code as specified in the Cscape Override section for that option.

A ladder code program must be written to allow the override of the Cscape configuration during runtime. The programmer needs to manually set values into many of the registers that Cscape normally configures.

Although the ladder code program is used during runtime to override the Cscape setup, the standard Cscape configuration procedures must still be performed in order to download the necessary parameters required by the OCS/RCS for power-up. At runtime, the ladder program assumes control and overrides the Cscape configuration parameters.

The following registers need to be manually set using the ladder code program that is written to override the Cscape configuration.

1. Set %Q19 to 1 in the OCS/RCS to override the Cscape configuration of the counter modes, control mapping, frequency counter selection, and other variables.

| Table 3.7 – OCS/RCS Register |             |  |  |  |

|------------------------------|-------------|--|--|--|

| Register                     | Description |  |  |  |

| %Q19                         | Set to 1.   |  |  |  |

# a. To override the Cscape parameters for the Totalizer Counter Function:

# 1. Totalizer Input Modes

Configure the counter input modes using the %Q9 through %Q16 registers in the OCS/RCS. %Q9, %Q10, %Q11 and %Q12 select the mode of input. %Q13-16 control count direction. The following table describes the relationship of %Q values and the resulting configuration.

| Table 3.8 - %Q Registers and Counter Input Modes |           |      |      |                       |  |  |  |  |

|--------------------------------------------------|-----------|------|------|-----------------------|--|--|--|--|

| Counter A Ir                                     | nput Mode |      |      |                       |  |  |  |  |

| %Q9                                              | %Q10      | %Q13 | %Q14 | Mode                  |  |  |  |  |

| 0                                                | 0         | 0    | 0    | Count and Direction   |  |  |  |  |

| 0                                                | 1         | 0    | 0    | Up count / Down count |  |  |  |  |

| 1                                                | 0         | 0    | 0    | Quadrature            |  |  |  |  |

| 1                                                | 1         | 0    | 0    | Internal 10 MHz clock |  |  |  |  |