# **GE Fanuc Automation**

**Programmable Control Products**

Genius™ I/O GENI Board

User's Manual

GFK-0073

May 1990

Series One

Series Three

Workmaster

Series Six

VuMaster

# Warnings, Cautions, and Notes as Used in this Publication

# Warning

Warning notices are used in this publication to emphasize that hazardous voltages, currents, temperatures, or other conditions that could cause personal injury exist in this equipment or may be associated with its use.

In situations where inattention could cause either personal injury or damage to equipment, a Warning notice is used.

Caution notices are used where equipment might be damaged if care is not taken.

### Note

Notes merely call attention to information that is especially significant to understanding and operating the equipment.

This document is based on information available at the time of its publication. While efforts have been made to be accurate, the information contained herein does not purport to cover all details or variations in hardware or software, nor to provide for every possible contingency in connection with installation, operation, or maintenance. Features may be described herein which are not present in all hardware and software systems. GE Fanuc Automation assumes no obligation of notice to holders of this document with respect to changes subsequently made.

GE Fanuc Automation makes no representation or warranty, expressed, implied, or statutory with respect to, and assumes no responsibility for the accuracy, completeness, sufficiency, or usefulness of the information contained herein. No warranties of merchantability or fitness for purpose shall apply.

The following are trademarks of GE Fanuc Automation North America, Inc.

Alarm Master GEnet PowerMotion CIMPLICITY Genius ProLoop CIMPLICITY PowerTRAC Genius PowerTRAC PROMACRO CIMPLICITY 90-ADS Helpmate Series Five CIMSTAR Logicmaster Series 90 Field Control Modelmaster

> Copyright 1996 GE Fanuc Automation North America, Inc. All Rights Reserved

This book provides the information needed to integrate a Genius<sup>TM</sup> Network Interface (GENI) board in a user-developed microprocessor system. The reader should be familiar with microprocessor system design and implementation, and with the Genius I/O system.

# **Contents of this Manual**

This book contains the following chapters:

Chapter 1. The GENI Board: gives board specifications, and describes GENI's capabilities.

Chapter 2. Hardware Interface: contains information about GENI board hardware, motherboard requirements, signals, and timing.

Chapter 3. Software Interface: describes the GENI's Shared RAM memory, which handles all data transfer between GENI and the host. Chapter 3 also summarizes GENI's activities during startup, steady state operation, and device login.

Chapter 4. GENI Setup: describes the area of Shared RAM where GENI stores its DIP switch setting and other setup data.

Chapter 5. GENI Status: describes the portion of Shared RAM where GENI stores its status data.

Chapter 6. Interrupts: describes Interrupt conditions. Chapter 6 also explains how to monitor Interrupt status, and how to enable or disable Interrupts from GENI to the host.

Chapter 7. Device Configuration: describes the table in Shared RAM where GENI stores information about devices on the bus. It also explains how GENI obtains this data.

Chapter 8. Device Inputs and Outputs: describes the area of Shared RAM which is used for input and output data.

Chapter 9. I/O Table Lockout: explains how the host can request or relinquish lockout of the I/O Tables in Shared RAM.

Chapter 10. GENI Commands: explains how the host can send and receive datagrams, and change GENI configuration.

Chapter 11. Global Data: describes how GENI can automatically exchange up to 128 bytes of Global Data with all other devices on the bus.

Chapter 12. Directed Control Data: explains how GENI can direct or receive up to 128 bytes of data to/from any other bus controller.

Chapter 13. Memory Access Datagrams: explains how GENI handles requests by other devices to read or write host memory.

Chapter 14. Troubleshooting: suggests troubleshooting steps based on observation of LEDS and the occurrence of bus errors.

Appendix A. General Macro Definitions: suggests simple macro definitions that might be used for a C language interface to GENI.

iii

# For More Information

÷. •

Refer to the Genius I/O System User's Manual (GEK-90486) for detailed information about Genius I/O blocks, system communications, types of systems, and system planning.

Jeanne Grimsby Technical Writer

ć

GFK-0073

| CHAPTER 1. | GENI BOARD                                        | 1-2        |

|------------|---------------------------------------------------|------------|

|            | GENI Board Description<br>Board LEDs              | 1-2        |

|            | DIP Switches                                      | 1-2        |

|            | GENI Board Specifications                         | 1-3        |

|            | GENI Board Components                             | 1-5        |

|            | Motherboard Requirements                          | 1-5        |

|            | Mounting the GENI Board                           | 1-5        |

|            | Power Supply Requirements                         | 1-5        |

|            | GENI DIP Switches                                 | 1-6        |

| CHAPTER 2. | HARDWARE INTERFACE                                | 0.1        |

|            |                                                   | 2-1        |

|            | Bus Loads/Drive Capability                        | 2-1        |

|            | Motherboard Wiring Requirements                   | 2-2        |

|            | Signal Conditioning                               | 2-2        |

|            | Faceplate Markings                                | 2-3        |

|            | Hand-held Monitor Connector                       | 2-3        |

|            | Bus CableSelection                                | 2-3        |

|            | 10 Volt Connector Signals                         | 2-4        |

|            | 5 Volt Connector Signals                          | 2-4        |

|            | Timing for Shared RAM Read Cycle                  | 2-5        |

|            | Timing for Shared RAM Write Cycle                 | 2-7        |

|            | Interrupt and Reset Timing                        | 2-8<br>2-8 |

| <b></b>    | GENI Ready/Data Select Timing                     | 2-8        |

| CHAPTER 3. | SOFTWARE INTERFACE                                |            |

|            | Shared RAM Structure Variables                    | 3-2        |

| <b>,</b>   | Interface Suggestions                             | 3-3        |

| •          | Startup                                           | 3-5        |

|            | Steady State Operation                            | 3-6<br>3-7 |

|            | Device Login and Log-out                          | 3-1        |

| CHAPTER 4. | GENI SETUP                                        |            |

|            | Changing the Setup Table                          | 4-2        |

|            | Read ID Requests to GENI                          | 4-2        |

| CHAPTER 5. | GENI STATUS                                       | <i>с</i> . |

|            | GENI Software Revision Number                     | 5-1        |

|            | GENI OK Status                                    | 5-1        |

|            | GENI Hardware Status                              | 5-2        |

|            | Hand-held MonitorConnected to GENI Bus Controller | 5-2        |

|            | Excessive Bus Errors                              | 5-2        |

|            | Bus Error Count                                   | 5-3        |

|            | Bus Scan Time                                     | 5-3<br>5-3 |

|            | Example Variables                                 | 5-5        |

| CHAPTER 6. | INTERRUPTS<br>Example Variables                   | 6-1        |

|            | Interrupt Table                                   | 6-2        |

|            | Disable Interrupt Table                           | 6-3        |

|            | - Darren Include Include                          | 0.0        |

.

|              |                                                   | GFK-0073     |

|--------------|---------------------------------------------------|--------------|

| CHAPTER 7.   | DEVICE CONFIGURATION                              |              |

|              | Device Configuration Changes                      | 7-1          |

|              | Device Configuration Table                        | 7-2          |

|              | Example Variables                                 | 7-3          |

| CHAPTER 8.   | DEVICE INPUTS AND OUTPUTS                         |              |

|              | Example Variable                                  | 8-1          |

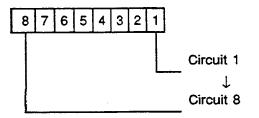

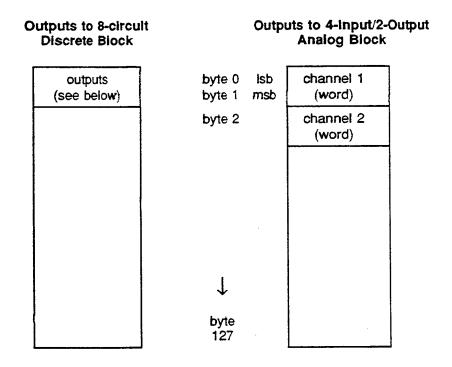

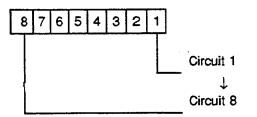

|              | I/O Table Structure                               | 8-2          |

|              | Input Table                                       | 8-3          |

|              | Location of a Device's Input Buffer               | 8-3          |

|              | Output Table                                      | 8-5          |

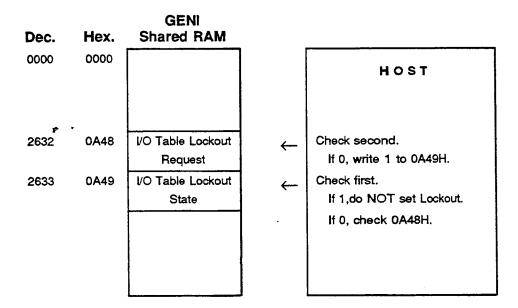

| CHAPTER 9.   | I/O TABLE LOCKOUT                                 | 0.1          |

|              | Lockout Procedure                                 | 9-1          |

| CHAPTER 10.  | GENI COMMANDS                                     | 10.1         |

|              | Command Block                                     | 10-1         |

|              | Status Byte                                       | 10-2         |

|              | Command Byte Format                               | 10-3         |

|              | Example Variables                                 | 10-4         |

|              | Example Macros                                    | 10-4<br>10-4 |

|              | Example Algorithms                                | 10-4         |

|              | Read Datagram Command                             | 10-6         |

|              | Procedure                                         | 10-0         |

|              | Status Definitions                                | 10-7         |

|              | Example Variables                                 | 10-7         |

|              | Transmit Datagram Command                         | 10-8         |

|              | Priority                                          | 10-9         |

|              | Maximum Datagram Length                           | 10-9         |

|              | Procedure                                         | 10-10        |

|              | Status Definitions                                | 10-10        |

| <b>P</b> - 1 | Example Variables                                 | 10-11        |

|              | Transmit Datagram with Reply Command              | 10-12        |

|              | Procedure<br>Status Definitions                   | 10-13        |

|              | Status Definitions                                | 10-13        |

|              | Example Variables<br>Configuration Change Command | 10-14        |

|              | Procedure                                         | 10-14        |

|              | Status Definitions                                | 10-15        |

| CHAPTER 11.  | GLOBAL DATA                                       |              |

| VIII         | Table Lockout                                     | 11-1         |

|              | Sending Global Data                               | 11-2         |

|              | Receiving Global Data                             | 11-2         |

|              | Timing Considerations                             | 11-2         |

| CHAPTER 12.  | DIRECTED CONTROL DATA                             |              |

|              | Sending Directed Control Data                     | 12-2         |

|              | Receiving Directed Control Data                   | 12-2         |

|              | Timing Considerations                             | 12-2         |

|              | Table Lockout                                     | 12-2         |

|              | Using Global Data and Directed Control Data       | 12-3         |

# CHAPTER 13. MEMORY ACCESS DATAGRAMS

**2** '

|             | Sending Memory Access Datagrams                       | 13-1 |

|-------------|-------------------------------------------------------|------|

|             | Receiving Memory Access Datagrams                     | 13-1 |

|             | Request Queue                                         | 13-1 |

|             | Request Queue Head Pointer                            | 13-1 |

|             | Request Queue Tail Pointer                            | 13-1 |

|             | Handling the Request Queue                            | 13-2 |

|             | Host Responses to Memory Access Datagrams             | 13-3 |

|             | Request Queue Buffer Format                           | 13-4 |

|             | Example Request Queue Variables                       | 13-4 |

|             | Header Byte                                           | 13-5 |

|             | Status Byte                                           | 13-5 |

|             | Example Status Variables for Request Queue Operations | 13-5 |

| CHAPTER 14. | TROUBLESHOOTING                                       |      |

| -           | Board LEDs                                            | 14-1 |

|             | Troubleshooting Steps                                 | 14-2 |

| APPENDIX A. | General Macro Definitions                             | A-1  |

1

± <sup>−</sup>

i

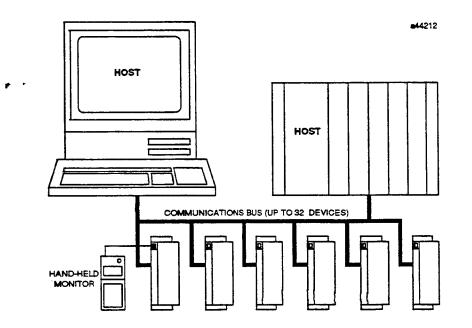

The GENI (Genius<sup>™</sup> Network Interface) Board (IC660ELB905) is a single printed circuit board designed to be a daughterboard in a user's microprocessor system. This manual explains motherboard requirements and operational and programming information needed to interface the GENI and motherboard to a host CPU. The host can be any CPU-type device v<sup>⊥</sup>ich is capable of reading and writing to GENI's general-purpose Shared RAM. The interface to this RAM is optimized for the IBM personal-computer bus, but can be adapted to work with many other types of CPU.

GENI handles all data transfer between the host and a Genius I/O bus, allowing the host to control remote I/O utilizing the extensive diagnostics, high reliability, and noise immunity of Genius I/O. In addition, the host can communicate with other hosts using the communications capabilities of the Genius LAN.

GENI operates as a general-purpose controller, performing the housekeeping tasks of initialization and fault management for up to 31 other bus devices. It keeps up-to-date images of the I/O controlled by each device, and can communicate with other controllers using datagrams, Global Data, and Directed Control Data messages. GENI handles all protocol, and provides a non-time critical method of tapping into the Genius bus.

The bus may serve any mix of I/O blocks and bus controllers; its primary purpose may be I/O control, or communications between hosts, or any combination of the two. The *Genius I/O System User's Manual* describes many types of systems that can be set up. In addition to Genius I/O blocks and bus controllers, a bus may serve one or more Genius Hand-held Monitors. The Hand-held Monitor is a versatile, portable operator interface device.

### 1-1

# **GENI Board Description**

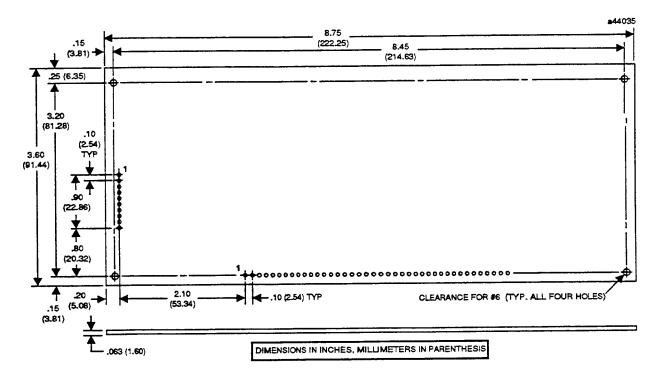

The GENI board is a rectangular, 4-layer board (3.6" by 8.75"). Components extend no more than .75" above the board surface. No components are mounted on the foil side of the board.

Connections to the motherboard are made by pins through the GENI board into a 10-pin connector and a 40-pin connector. The transformer and hybrid are located near the 10-pin connector to keep on-board electrical noise to a minimum.

### **Board LEDs**

Two LEDs on the GENI board show the status of the board itself, and of its communications with the Genius bus. During proper operation, both the BOARD OK and COMM OK LEDs will be on.

### **DIP Switches**

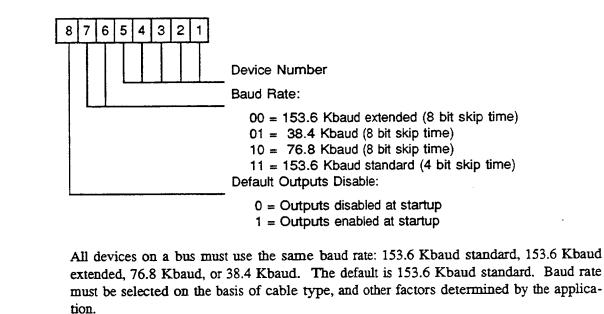

DIP switches on the board are used to select Baud Rate, to specify a bus Device Number, and to enable or disable outputs from the host to the devices on the bus.

### **GENI Board**

GFK-0073

# **GENI Board Specifications**

| Electrical:                  |                                                                   |

|------------------------------|-------------------------------------------------------------------|

| Power Requirements           | 5 volts DC +/-10%, 400mA (maximum)                                |

| Bus Loading                  | 1 LS TTL load per input line                                      |

| Bus Drive Capability         | 10 LS TTL loads per output line                                   |

| Mechanical                   |                                                                   |

| <b>GENI Board Dimensions</b> | Height at tallest component: 0.75 inches (19.05mm)                |

|                              | Width: 3.6 inches (91.44mm)                                       |

|                              | Depth: 8.4 inches (213.36mm)                                      |

|                              | Board thickness: 0.063 inch (1.60mm)                              |

| Environmental:               |                                                                   |

| Operating:                   |                                                                   |

| Ambient Temperature at board | $-25^{\circ}$ C to $+85^{\circ}$ C, $^{\circ}$ F to $+^{\circ}$ F |

| Humidity                     | 5% to 95% non-condensing                                          |

| Altitude                     | 10,000 feet                                                       |

| Vibration                    | 0.2 inch displacement 5 to 10 Hz                                  |

|                              | 1 G 10 to 200 Hz                                                  |

| Shock                        | 5 G. 10mS duration per MIL-STD 810C, method 516.2                 |

| Non-operating:               |                                                                   |

| Ambient Temperature at board | $-40^{\circ}$ C to $+125^{\circ}$ C, °F to $+^{\circ}$ F          |

| Humidity                     | 5% to 95% non-condensing                                          |

| Altitude                     | 40,000 feet                                                       |

| Vibration                    | 0.2 inch displacement 5 to 10 Hz                                  |

|                              | 1G 10 to 200 Hz                                                   |

| Shock                        | Board packed in shipping container:                               |

|                              | 5 G, 10mS duration per MIL-STD 810C, method 516.2                 |

|                              | - · , · · · · · · · · · · · · · · · · ·                           |

|                              |                                                                   |

# Ordering Information

| Description                     | Catalog<br>Number |

|---------------------------------|-------------------|

| GENI Board                      | IC660ELB905       |

| 8K x 8 EPROM                    | 44A723355-000     |

| HHM Connector                   | 44A723293-001     |

| Genius I/O System User's Manual | GEK-90486         |

.

# **GENI Board Components**

Principal components of the GENI board are:

| 6303 microprocessor                 | The serial interface microprocessor. It writes messages to transmit buffers in the MIT chip.                                                                                                                                                                                                                                                                                                                                                                                         |

|-------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MIT chip                            | The MIT chip handles the hardware interface to the bus. It also provides many support<br>functions such as CRC generation, error checking, a watchdog timer function, chip select,<br>LED drivers, and processor clock signals.                                                                                                                                                                                                                                                      |

| Transmit/receive<br>hybrid circuit  | A hybrid circuit interfaces the MIT transmit and receive signal levels to bus signal levels.                                                                                                                                                                                                                                                                                                                                                                                         |

| Transformer                         | The transformer isolates the GENI board circuitry from the bus cable.                                                                                                                                                                                                                                                                                                                                                                                                                |

| Dual port RAM                       | Dual port RAM is where the serial interface microprocessor (6303) and the GENI manager microprocessor (64180) exchange data. Dual port RAM removes timing skews between the two processors, which are running two separate, asynchronous systems. Dual Port RAM is controlled by an EPLD, which arbitrates memory requests on a byte-by-byte basis, allowing the 6303 and the 64180 equal access.                                                                                    |

| 64180<br>Microprocessor             | This microprocessor transfers data between GENI's Shared RAM and the serial interface microprocessor (6303), through dual port RAM. The 64180 microprocessor has 8K bytes of RAM for its exclusive use.                                                                                                                                                                                                                                                                              |

| Shared RAM                          | Shared RAM is the host's interface to GENI. It provides 16K bytes of storage space for I/O tables, configuration data, diagnostic data, and background message queues. Shared RAM can be accessed by either GENI or the host without loss of data. There is no need for software arbitration. Shared RAM looks like a pure RAM device to both systems.                                                                                                                               |

| Shared RAM<br>Address<br>Comparator | The Shared RAM Address Comparator causes a 64180 microprocessor interrupt when the host's Write line is true and the current Shared RAM address matches a specific interrupt (command) byte address. The interrupt is latched until the 64810's Read line is true and the current Shared RAM address matches the specific interrupt (Command) byte address. Thus, an interrupt occurs when the host writes to the command byte and is cleared when the 64180 reads the command byte. |

|                                     | This circuit is implemented in a single array logic device (EPLD) which allows the address of the interrupt bytes to be reprogrammed during redevelopment, and provides the capability for latching and clearing the interrupt. The EPLD arbitrates Shared RAM memory requests on a byte-by-byte basis and allows the host and bus controller equal access to any byte of Shared RAM without loss of data.                                                                           |

# **Motherboard Requirements**

The motherboard must provide the following minimum support:

- +5V power connection with appropriate ground connections.

- Powerup Reset pulse to the GENI board.

- Female 10-pin and 40-pin connectors for signal and power signals to GENI. Recommended mating connectors are available from AMP, Berg, Cannon, and Augat.

- Terminal block and optional D subminiature connector to the bus.

- HHM connector (D subminiature connector) with HHM Present signal.

### Mounting the GENI Board

The GENI board is designed to be mounted to the motherboard, using spacers, via its four corner holes. These holes accept plastic PCB supports (Richo Plastics or equivalent), or screws or standoffs.

DO NOT

- Mount the board where airflow across the board is obstructed.

- Mount the board nearer than 1/8'' (.125") to any other boards or rack components.

- Use adhesives or conformal coatings on any part of the board.

# **Power Supply Requirements**

p - 1

The GENI board requires a 5 volt DC source for logic power. Supply voltage should not vary more than 10% above or below nominal (below 4.5 VDC or above 5.5 VDC).

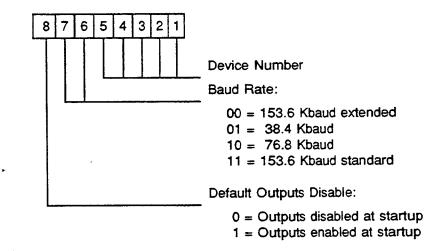

# **GENI DIP Switches**

The GENI board's DIP switches must be set before installing the GENI bus controller into the host device. The switch settings determine: the baud rate, the status of the outputs disable bytes during initialization, and the Device Number of the GENI board.

### **DIP Switch Assignments**

**Baud Rate**

Device Number Each device connected to the Genius bus must have a unique Device Number assigned. This number represents the module's "bus address". The default Device Number set with the DIP switches on the GENI module is 31.

Each Genius communications bus can serve up to 32 devices, which are identified by Device Numbers from 0 to 31. A module's Device Number represents its place in the communications sequence on the bus.

By convention, certain numbers are associated with particular types of devices. For example, Device Number 0 is normally used for a Genius Hand-held Monitor. The Series 90-70 PLC and the Series Six PLC use Device Numbers 30 and 31 for bus controllers in a backup (redundancy) type of system. Be sure that the Device Number assigned to the GENI bus controller is both unique and appropriate for the system.

Outputs Disabling Outputs means preventing the transmission of outputs to all devices on the bus when the GENI bus controller is powered up. This prevents incorrect operation of the outputs at powerup. The default setting is for outputs to be enabled (DIP switch 8 is set to 1). To disable outputs, set switch 8 to 0.

### Changing the DIP Switch Settings

GENI reads these switch settings at powerup; if any switch setting is changed, it will be ignored until the next time GENI is powered up. An exception to this is that the Device Number may be changed if there is a Device Number conflict.

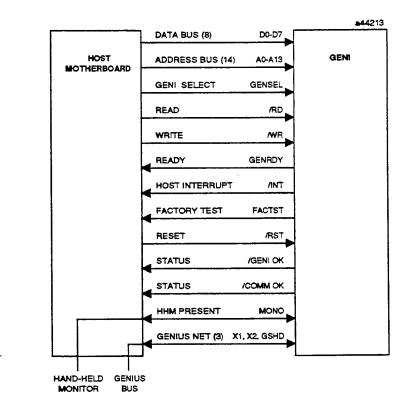

Signal connection between GENI and the motherboard is provided by via a 40-pin male connector for logic signals and a 10-pin male connector for Genius bus signals.

The GENI board's interface signals are directly compatible with those of the IBM PC backplane. Hosts with significant variances from the IBM PC backplane may require motherboard translation circuitry.

### **Bus Loads/Drive Capability**

All input lines to the GENI present no more than one standard LSTTL load to the host interface connector. All output lines from the GENI are capable of driving 10 standard LSTTL loads. These lines, with the exception of the /INT and /GENI OK lines are tri-state outputs. The /INT line is an open-collector output that can be wired-ORed to a single interrupt input. The /GENI OK and /COMM OK lines are low-true open-collector type outputs with built-in current-limiting to 10mA suitable for driving LEDs directly.

### 2-1

# Motherboard Wiring Requirements

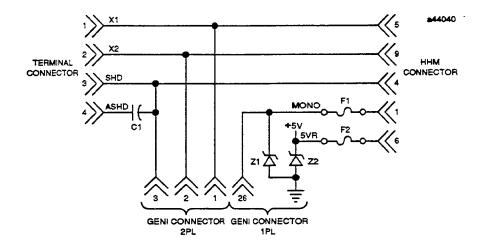

X1, X2, SHD, and AUXSHD must be 1/16 inch from all other signals on the motherboard. MONO and 5VR must be 1/16 inch from all other signals on the motherboard up to the high voltage suppressors, at which point, they may be grouped with the other motherboard 5 volt signals.

X1, X2, and GSHD must be connected to a terminal connector on the motherboard.

The GSHD input, which connects to the bus shield, should be connected to earth ground on the motherboard.

Five volt power and logic grounds should be brought into the GENI board on both sides of the 40-pin connector. These grounds must be at the same potential at both ends of the connector so ground loop currents will not flow in the GENI board.

### Signal Conditioning

The MONO line should be protected from the accidental application of 120 VAC by adding over-voltage protection devices on the motherboard. These devices should shunt to ground any excess currents developed from high voltage devices applied to either pin 1 or pin 6 of the HHM connector. Recommended devices are transient suppressors with a breakdown voltage of 7.5 volts.

- 1. 1N6268A Motorola and other vendors

- 2. TZV7.5A Semicon

The capacitor ("c" in the illustration above) is recommended to shunt any AC noise present on the bus shield. It should be a 0.1 microfarad ceramic 100 volt, 20% capacitor.

### **Faceplate Markings**

If a faceplate is used for the combined motherboard/daughterboard (referred to in this book as the GENI bus controller), it should provide the following names for the signals on the external bus connector:

| X1     | SERIAL 1   |

|--------|------------|

| X2     | SERIAL 2   |

| SHD    | SHIELD IN  |

| AUXSGD | SHIELD OUT |

### Hand-held Monitor Connector

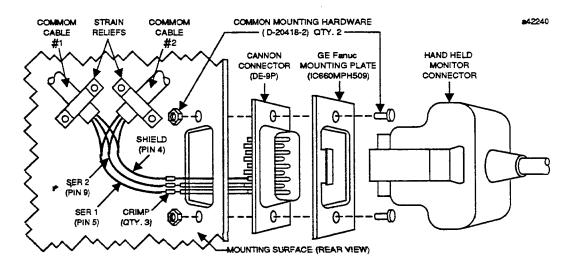

The Hand-held Monitor connector should be a DE-9P subminiature male connector capable of accepting two 4-40 threaded screws. Since the DE-9P connector does not provide a mechanical locking mechanism to secure the clip at the end of the HHM's cable, a mounting plate (order part number IC660MPH509) should be used to prevent the HHM cable from falling out of the connector. This dress plate has a metal catch that allows the HHM connector clip to hook onto the D connector. The dress plate is mounted on the front of the D connector and held in place by two locking screws (Cannon D20418-2). The unused pins on the D connector should remain unconnected in order to maintain isolation between the X1, X2, SHD lines, and the MONO and 5VR lines.

### **Bus Cable Selection**

The type of bus cable used will depend upon the application requirements. The Genius I/O System User's Manual gives guidelines for bus cable selection.

# **10 Volt Connector Signals**

The 10-pin connector provides the following Genius bus signals:

| PIN | FUNCTION |

|-----|----------|

| 1   | X1       |

| 2   | X2       |

| 3   | GSHD     |

| 4   | NC       |

| 5   | NC       |

| 6   | NC       |

| 7   | NC       |

| 8   | NC       |

| 9   | NC       |

| 10  | NC       |

X1, X2, and GSHD are the serial bus connections; they must be connected to a terminal connector on the host motherboard.

X1 - X2 are differential signals that carry Genius bus data.

GSHD is connected to the serial bus shield. This signal should be connected to earth ground on the motherboard.

# **5** Volt Connector Signals

The 40-pin connector provides the following 5-volt signals:

| PIN    | FUNCTION | PIN | FUNCTION |

|--------|----------|-----|----------|

| 4 ·    | GND      | 21  | A13      |

| 2      | +5V      | 22  | +5V      |

| 2<br>3 | NC       | 23  | /RD      |

| 4      | /GENIOK  | 24  | /WR      |

| 5      | /INT     | 25  | /GENSEL  |

| 6      | /RST     | 26  | MONO     |

| 7      | FACTST   | 27  | /GENRDY  |

| 8      | A0       | 28  | /COMM OK |

| 9      | A1       | 29  | NC       |

| 10     | A2       | 30  | GND (0V) |

| 11     | A3       | 31  | D3       |

| 12     | A4       | 32  | D2       |

| 13     | A5       | 33  | D4       |

| 14     | A6       | 34  | D1       |

| 15     | A7       | 35  | D5       |

| 16     | A8       | 36  | D0       |

| 17     | A9       | 37  | D6       |

| 18     | A10      | 38  | D7       |

| 19     | A11      | 39  | +5V      |

| 20     | A12      | 40  | GND      |

# Hardware Interface

### GFK-0073

Signals on the 40-pin connector are described in the following table.

| Signal Type        | Signal Name | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

|--------------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Data Signals       | D0-D7       | The eight data lines are bi-directional. They are used to transfer data in the GENI board's Shared RAM to/from an 8-bit microprocessor-type data bus.<br>These lines enter the high-impedance state when /RST is low or /GENSEL is high. Tristate output.                                                                                                                                                                                                                                                                      |  |  |

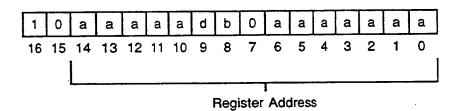

| Address<br>Signals | A0-A13      | Fourteen consecutive address lines which designate an address in Shared RAM to be written or read.                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| Control Signals    | /WR         | The Write strobe input to the GENI indicates that data on D0-D7 is valid and should be written from the host interface bus to Shared RAM.                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

|                    | /RD         | Read strobe line; The ReaD input to the GENI is used during a host CPU read cycle. It enables data transfer from Shared RAM to the host interface bus.                                                                                                                                                                                                                                                                                                                                                                         |  |  |

|                    | /RST        | ReSeT initializes the GENI board when held low. It must be held low during<br>powerup and for a minimum of 20 milliseconds after all power supplies are in<br>tolerance. All GENI output signals are held inactive during reset.                                                                                                                                                                                                                                                                                               |  |  |

|                    | /GENSEL     | GENi SELect is use by the host to request access to Shared RAM. All output signals from GENI are held inactive and data cannot be written into Shared RAM when this signal is high.                                                                                                                                                                                                                                                                                                                                            |  |  |

|                    | /GENRDY     | GENi ReaDY is an output from the GENI to the host motherboard, which tells<br>the host to complete its memory access cycle. It is functionally identical to a<br>'WAIT' signal from a slow memory device. The host system should use this<br>signal to introduce WAIT states if necessary during a GENI Shared RAM<br>access. /GENRDY falls low until the low to high transition of /RD or /WR. A<br>high to low transition of /GENRDY means that the host can stop inserting wait<br>states (ending its read or write cycle). |  |  |

| Interrupt Signal   | /INT        | INT is an open-collector output that tells the host an event occurred whenever it goes low (it pulses low for 5.44 microseconds). Provision must be made for the host to remember that this pulse occurred. Conditions that may cause an interrupt can be selected and monitored through the Shared RAM interface.                                                                                                                                                                                                             |  |  |

| Status Signals     | MONO        | When the HHM MONitOr (MONO) signal is high, a Hand-held Monitor is attached to the HHM connector on the motherboard.                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

|                    | /GENI OK    | Reflects the GENI OK LED output. Low when GENI is running normally.<br>High when a hardware error has been detected. This line is internally<br>current-limited to 10mA. It can directly drive an LED or be used as a logic<br>signal.                                                                                                                                                                                                                                                                                         |  |  |

|                    | СОММ ОК     | A low /COMM OK output indicates no communications errors on the bus.<br>COMM OK is current limited and can directly drive an LED or can be used as<br>a logic signal.                                                                                                                                                                                                                                                                                                                                                          |  |  |

| 5 Volt             |             | 5 volt +/-10% power supply input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| 0 volt             |             | Logic ground input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

ċ

.'

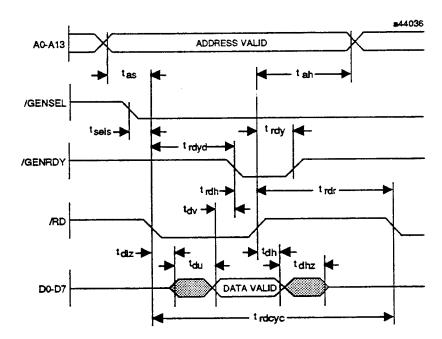

# Timing for Shared RAM Read Cycle

|     | Item                           | Minimum nS | Maximum nS |

|-----|--------------------------------|------------|------------|

|     | Read Cycle Time (trdcyc)       | 615        | -          |

|     | Address Setup Time (tas)       | 0          | -          |

|     | Address Hold Time (tah)        | 0          | -          |

|     | GENI Select Setup Time (tsels) | 0          | -          |

|     | GENI Ready Delay (trdyd)       | 479        | 937        |

|     | Ready Hold After Read (trdy)   | 16         | 31         |

| * * | Read Hold After Ready (trdh)   | 0          | -          |

|     | Read Recovery Time (trdr)      | 136        | -          |

|     | Data Time to Low Z (tdlz)      | 2          | 668        |

|     | Data Undefined Time (tdu)      | -          | 178        |

|     | Data Valid Before Ready (tdv)  | 96         | -          |

|     | Data Hold Time (tdh)           | 2          | 28         |

|     | Data Time to High Z (tdhz)     | 2          | 28         |

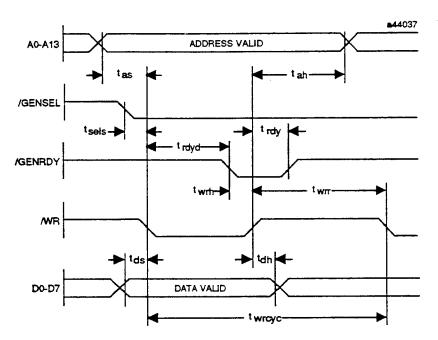

# Timing for Shared RAM Write Cycle

| Item Name                      | Minimum nS | Maximum nS |

|--------------------------------|------------|------------|

| Write Cycle Time (twrcyc)      | 615        | -          |

| Address Setup Time (tas)       | 0          | -          |

| Address Hold Time (tah)        | 0          | -          |

| GENI Select Setup Time (tsels) | 0          |            |

| GENI Ready Delay (trdyd)       | 479        | 937        |

| Ready Hold After Write (trdy)  | 16         | 31         |

| Write Hold After Ready (twrh)  | 0          | -          |

| Write Recovery Time (twrr)     | 136        | -          |

| Data Setup Time (tds)          | 0          | -          |

| Data Hold Time (tdh)           | 0          | -          |

Ľ,

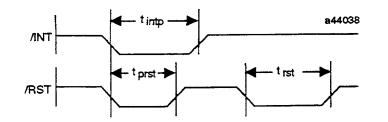

# **Interrupt and Reset Timing**

| Item                        | Minimum | Maximum |

|-----------------------------|---------|---------|

| /INT Pulse Width (tintp)    | 5.44µS  | -       |

| Powerup /RST Pulse (tprst)  | 2000mS  | -       |

| Operating /RST Pulse (trst) | 10µS    | -       |

### **Reset Restrictions**

After the rising edge of /RST, do not enable interrupts or read/write to Shared RAM for 500 microseconds. This time is required for hardware and software initialization on the GENI board.

One false interrupt occurs within this time period. Reading or writing to Shared RAM during this time may cause the watchdog timer to time out.

The GENI OK flag is invalid during this period. In addition, the /GENRDY line may remain high indefinitely after /GENSEL goes low.

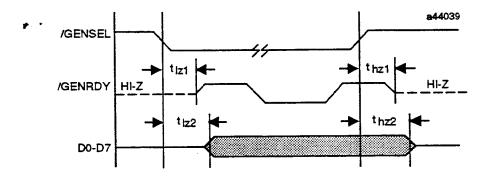

# **GENI Ready/Data Select Timing**

| Item                               | Minimum nS | Maximum nS |

|------------------------------------|------------|------------|

| Select to Low Z /GENRDY (tlz1)     | 2          | 30         |

| /Select to Low Z Data (tlz2)       | 2          | 668        |

| /Deselect to High Z /GENRDY (thz1) | 2          | 31         |

| Deselect to High Z Data (thz2)     | 4          | 32         |

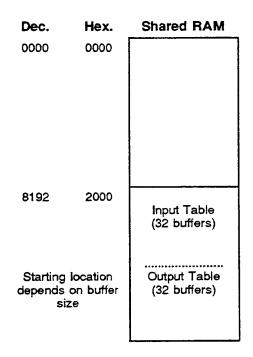

GENI's Shared RAM memory handles all data transfer between GENI and the host. A memory map is shown below.

| Location<br>dec. hex. | Content                             | Size In<br>Bytes |

|-----------------------|-------------------------------------|------------------|

| 0000 0000             | Request Queue                       | (2176)           |

|                       |                                     |                  |

| 2176 0880             | Request Queue Head Pointer*         | (1)              |

| 2177 0881             | Request Queue Tail Pointer          | - (1)            |

| 2178 0882             | GENI Setup Table                    | (16)             |

| 2194 0892             | GENI Status Table                   | (16)             |

| 2210 08A2             | Interrupt Status Table              | (16)             |

| 2226 08B2             | Interrupt Disable Table             | (16)             |

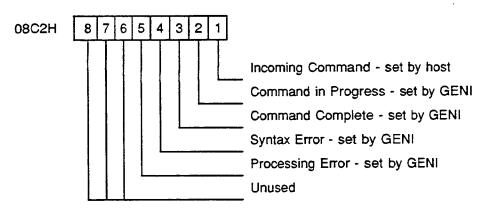

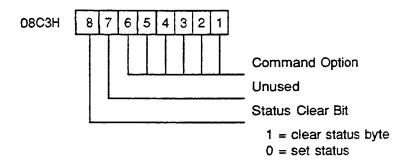

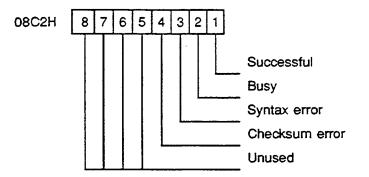

| 2242 08C2             | Command Block*                      | (16)             |

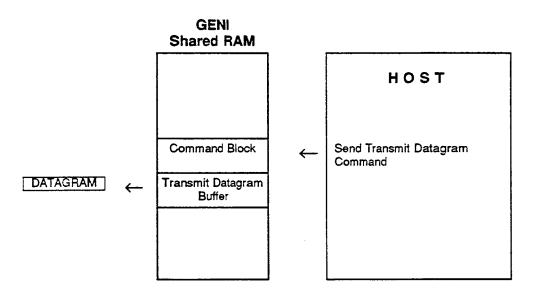

| 2258 08D2             | Transmit Datagram Buffer            | (240)            |

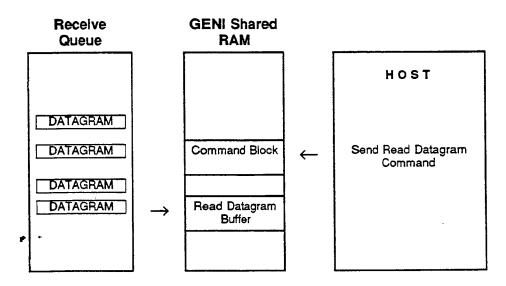

| 2498 09C2             | Read Datagram Buffer                | (134)            |

| 2632 0A48             | VO Table Lockout Request *          | (1)              |

| 2633 0A49             | VO Table Lockout State              | (1)              |

| 2634 OA4A             | Reserved                            | <b>(5045</b> )   |

| 7680 1E00             | Device Configuration Table          | (256)            |

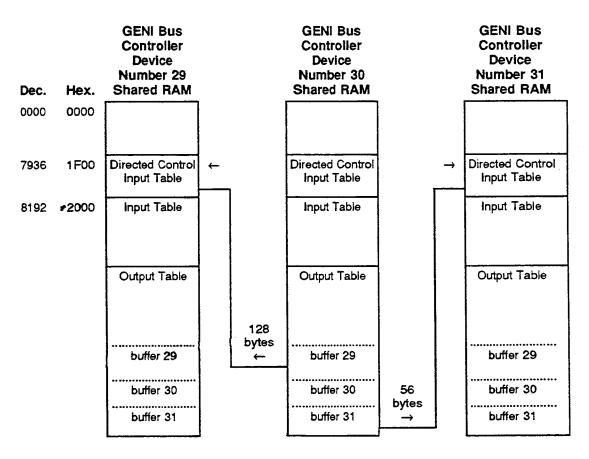

| 7936 1F00             | Directed Control Input Table        | (128)            |

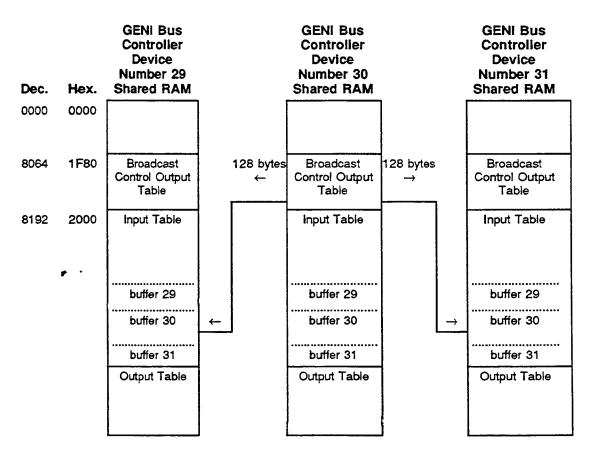

| 8064 1F80             | Broadcast Control Output Table      | (128)            |

| 8192 2000             | Device I/O Table                    | (8192)           |

| 16383 3FFF            | • Host write causes interrupt to GI | ENI              |

**Request Queue:** Queue for incoming Read Levice, Write Device, and Write Point datagrams to the host.

Request Queue Head Pointer: Number of the Request Queue buffer currently being read.

Request Queue Tail Pointer: Indicates the most recent entry in the Request Queue.

**GENI Setup Table:** Characteristics of GENI and the bus.

GENI Status Table: Diagnostics for GENI bus controller and the bus.

Interrupt Status Table: Current status of interrupts to host.

Interrupt Disable Table: Used to enable/disable host interrupts.

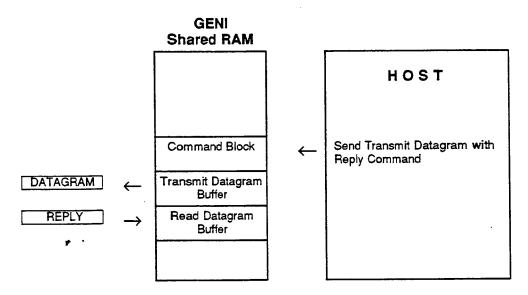

Command Block: Used by host to send Read Datagram, Transmit Datagram, Transmit Datagram with Reply, and Configuration Change commands to GENI.

Transmit Datagram Buffer: Temporary location for sending datagrams.

**Read Datagram Buffer:** Location where host may read incoming datagrams.

I/O Table Lockout Request/Relinquish: Used to set or release GENI lockout of I/O Tables.

I/O Table Lockout State: Actual lockout state.

**Reserved Area:** The host should NOT read or write in this area.

Device Configuration Table: Location of device ID, status, and setup information.

Directed Control Input Table: Location for receiving Directed Control Data.

Broadcast Control Output Table: Buffer for sending Global Data.

Device I/O Table: Contains all device inputs and outputs, and incoming Global Data.

# 3-1

.

# Shared RAM Structure Variables

The host can access various elements of Shared RAM by assigning them variable names. For example, the Shared RAM variables listed below might be defined for a C language interface to GENI. The chapters that follow list additional example variable names for use with specific areas of Shared RAM.

| typede | f             |                             |

|--------|---------------|-----------------------------|

| struct |               |                             |

|        | REQUEST Q     | <pre>request_q[16];</pre>   |

|        | unsigned char | head idx;                   |

|        | unsigned char | tail_idx;                   |

|        | SETUP GENI    | setup;                      |

|        | GENI_STATUS   | status;                     |

|        | unsigned char | <pre>int_status[16];</pre>  |

|        | unsigned char | <pre>int_disable[16];</pre> |

|        | COMMAND       | cmmd_block;                 |

|        | unsigned char | outdata[240];               |

|        | unsigned char | indata[134];                |

|        | unsigned char | lockout;                    |

|        | unsigned char | <pre>lockout_state;</pre>   |

|        | unsigned char | hostclr;                    |

|        | unsigned char | <pre>spare[5045];</pre>     |

|        | DEV_CONFIG    | <pre>devices[32];</pre>     |

|        | unsigned char | <pre>geni_dcd[128];</pre>   |

|        | unsigned char | <pre>geni_bcd[128];</pre>   |

|        | unsigned char | <pre>iotables[8192];</pre>  |

#### }SRI;

This example defines one variable for the device I/O tables. Separate variables could be defined for the Input Table and the Output Table. The size of the Input Table and Output Table depends on the I/O buffer length that has been selected for the application.

\* \*

# **Interface Suggestions**

### **GENI** Setup

Use the GENI Setup Table to read or change:

- A. Global Data length (for Global Data sent by GENI).

- B. Directed Control Data length (for Directed Control Data received by GENI).

- C. Reference Address

- D. I/O buffer length

To change the GENI Setup Table, place the new data in the Setup Table, then send GENI a Configuration Change command in the Command Block.

See chapter 4 for information about the GENI Setup Table.

### **GENI** Status

Use the GENI Status Table to monitor:

- A. GENI Revision Number

- B. GENI OK status

- C. GENI hardware status

- D. HHM Present status

- E. total bus error count

- F. I/O scan time

See chapter 5 for information about the GENI Status Table.

### Interrupts

Use the Interrupt Status Table to monitor the Interrupt Summary byte, as well as individual interrupt status bytes:

- A. Request Queue entry

- B. GENI status change

- C. Device status change

- D. Outputs sent

- E. Command complete

- F. Receive Queue not empty

- G. I/O Table Lockout grant

Use the Interrupt Disable Table to enabled or disable one or more interrupts.

See chapter 6 for information about the Interrupt Tables.

### **Device Configuration**

Use the Device Configuration Table to read information about each device on the bus:

- A. its model number

- B. whether outputs from the host are enabled

- C. whether the device is present on the bus

- D. the device's Status Table or Reference Address

- E. its I/O data length

- F. its block I/O type

The host can change the outputs enable/disable flag for each device.

See chapter 7 for information about the Device Configuration Table.

To read additional device configuration data, the host can use a Transmit Datagram with Reply command to send a Read Configuration datagram to the device. See chapter 10 for details.

To change device configuration data, the host can use a Transmit Datagram command to send a Write Configuration datagram to the device. See chapter 10.

### **Device Inputs and Outputs**

Use the Device I/O Table to read device inputs, or to send outputs. See chapter 8 for instructions.

To assure integrity of I/O data, Global Data, and Directed Control Inputs, set I/O Table Lockout. This will lock GENI out of the I/O tables while the host completes its access. See chapter 9 for information.

To change the length of the I/O Table buffers, use a Command Block to send a Configuration Change command to GENI, after changing the GENI Setup Table. See chapters 4 and 10 for information.

### Read or Write Datagrams

If GENI will send datagrams to other bus controllers, or receive datagrams from them, see chapter 10. It explains how to send commands to the GENI through the Command Block area of Shared RAM.

There are two exceptions to this:

- 1. Datagrams that require no host interaction: Read ID and Configuration Change datagrams from devices on the bus.

- 2. Datagrams that require direct access to host memory. These are explained in chapter 13.

### Automatic Data Transfer Between Hosts

- A. Use Global Data to automatically send up to 128 bytes of data to all other bus controllers on the bus. See chapter 11 for instructions.

- B. Use Directed Control Data to automatically send up to 128 bytes of data to one specific device on the bus. See chapter 12 for instructions.

- C. Monitor the Input Table to read Global Data or input data received from another device. See chapter 11.

- D. Monitor the Directed Control Inputs Table to read Directed Control Data received from another device. See chapter 12.

### Software Interface

GFK-0073

## Startup

When the GENI board Reset is released, it begins its startup procedure. During this time, GENI automatically performs the following diagnostic hardware tests:

- 1. EPROM checksum test

- 2. microprocessor test

- 3. MIT bus test

- 4. RAM test

If any error is found, GENI reports it in the GENI Status Table. It then attempts to go into a controlled lockup state. The host does not receive the GENI OK status, and the GENI OK light does not go on. If no error is found during the diagnostic tests, GENI initializes the contents of Shared RAM to the following defaults.

| Device Present Flag                   | 0                           |

|---------------------------------------|-----------------------------|

| Outputs Enable                        | setting based on DIP switch |

| Device Number                         | setting based on DIP switch |

| Baud Rate                             | setting based on DIP switch |

| I/O Table Lockout State               | 0                           |

| Broadcast Control Data(inputs) length | 0                           |

| Directed Control Data(outputs) length | 0                           |

| I/O Table Buffer Length               | 128 (80 hex)                |

| Reference Address                     | 0FFFF (hex)                 |

| All Interrupt Status                  | 0                           |

| All Interrupt Disable                 | 0                           |

| All GENI Status                       | 0                           |

| Receive Queue                         | empty                       |

| Transmit Datagram Buffer              | empty                       |

| Request Queue                         | empty                       |

| Command Status byte                   | Command Complete            |

|                                       |                             |

It also initializes the dual port RAM, the MIT, and other hardware or software related variables needed to begin steady-state operation.

DIP switch settings on the GENI board are read at powerup. This information is ignored at all other times. When the MIT is initialized, it is set with the Device Number and baud rate selected with the DIP switches.

During the powerup sequence, the host must not read or write to the Shared RAM for 1.7 seconds. After that time, the GENI OK flag should be on, indicating that the self-test has passed. The GENI will set this flag within 2 seconds of powerup. After the GENI OK flag is set, there is an additional 1.5 second delay. During this time, the host can change the GENI configuration.

GENI will not accept inputs from devices on the bus or send outputs until powerup has been completed successfully. When the board's MIT microprocessor is initialized, GENI is ready to begin transmitting on the bus.

ć

# **Steady State Operation**

After successful startup, GENI starts transmitting the bus token, and begins normal operation. GENI will immediately begin collecting input data from devices on the bus. It sends outputs from Shared RAM immediately unless the Outputs Disable DIP switch is set to Disable. If the switch is set to Disable, the host must enable outputs before GENI will send outputs from Shared RAM.

GEII's activities during normal operation are summarized below.

| Self-test                 | During steady-state operation, GENI continually executes self-tests. This testing includes<br>non-destructive private RAM test, EPROM checksum, and maintenance of an internal<br>heartbeat. If any fault occurs, it is reported through the GENI Status Table area of shared<br>RAM. Outputs are then disabled, and the GENI bus controller attempts to halt.                                        |

|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I/O Service               | GENI maintains a table of inputs received from the other devices on the bus. It also<br>maintains an information queue containing the Device Numbers of the devices that sent<br>input data. Each bus scan, GENI directs outputs from the host to those devices. It also<br>maintains a queue of device addresses to which output data has been sent.                                                 |

| I/O Table Lockout         | Upon request from the host, GENI will "lock out" the I/O table. During lockout, GENI will not access the Device I/O Tables, the Broadcast Control Output (Global Data) Table, or the Directed Control Input Table.                                                                                                                                                                                    |

| Host interrupts           | Seven conditions which may require immediate host attention can be monitored, and may cause the GENI to send an interrupt the host. Before sending the interrupt, GENI sets a byte corresponding to the detected condition in the Interrupt Status Table in Shared RAM. The host must clear the byte after servicing the interrupt.                                                                   |

| ÷ *                       | The host can disable any of the seven interrupt conditions by setting bytes in the Interrupt Disable Table area of Shared RAM. If one of the interrupt conditions occurs, GENI sets the appropriate byte in the Interrupt Status Table. If the corresponding disable flag is set, no interrupt to the host is generated. The host is still responsible for clearing the Interrupt Status Table bytes. |

| Datagram Service          | GENI maintains a queue of datagrams from other devices. It will also transmit datagrams from the host to devices on the bus.                                                                                                                                                                                                                                                                          |

| Maintain Bus Scan<br>Time | GENI maintains a minimum bus scan time of 3mS. GENI monitors actual bus scan time, and stores the current scan time in Shared RAM, where it can be read by the host.                                                                                                                                                                                                                                  |

# **Device Login and Log-out**

Device login and log-out are two activities that occur automatically while the bus is in operation.

### **Device Login**

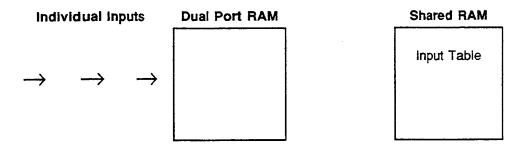

During normal operation, login activity occurs when a new device on the bus starts broadcasting input data. Whenever inputs are received from a device, GENI checks to determine that the device is "logged in" to the Configuration Table area of Shared RAM. If it is, the input data is accepted and placed in the Input Table. If the device is not logged in, the bus controller automatically goes through the login steps described below.

In a redundant system, heavy login activity occurs following a bus or controller switch.

The host should check the login status of a device before reading inputs from its buffer in the Input Table, to assure that the data is valid inputs.

During operation of the bus, if GENI receives input data from a previously unrecognized device, it automatically sends a Read ID message to the new device. If the device sends back a Read ID Reply message, GENI stores the configuration data contained in that message in the Device Configuration Table area of Shared RAM, in the buffer that corresponds to the new device's Device Number.

Next, GENI sets the Device Present flag for that device in the Device Configuration Table. It also sets the Device Status Change byte in the Interrupt Status Table. If the Device Change Interrupt or Interrupt Summary is NOT disabled, GENI also sends an interrupt to the host.

To enable sending outputs to the new device, the host must reset the Output Disable flag in the Device Configuration Table. When this is done, GENI automatically directs an Assign Controller message to the device. This instructs the device to send fault reports and configuration change messages to the GENI. GENI then starts sending the data from that device's area of the output table each bus scan.

### **Device Log-out**

GENI automatically logs out any device that was previously logged in, if it does not send new inputs for at least three consecutive bus scans. GENI stops sending outputs to the device. It also marks the device as "not present" and sets the Device Status Change byte in the Interrupt Status Table. If the Loss of Device or Interrupt Summary is NOT disabled, GENI also sends an interrupt to the host.

The device remains logged off until it begins broadcasting inputs again. At that time, GENI will execute the login steps described above.

.

.

. .

---

. . .

.

-

To read or change the GENI's configuration, use the GENI Setup Table, which begins at Shared RAM location 2178D/0882H. It contains the following information:

| Byte No.   | Description                   |  |

|------------|-------------------------------|--|

| byte 1     | GENI board DIP Switch Value*  |  |

| byte 2     | Reference Address (lsb)       |  |

| byte 3     | Reference Address (msb)       |  |

| byte 4     | Broadcast control data length |  |

| byte 5     | Directed control data Length  |  |

| byte 6     | I/O Table Buffer Length       |  |

| bytes 7-16 | Reserved                      |  |

\* Only byte the host may NOT change directly.

DIP Switch Value the first byte of the Setup Table contains the settings of the GENI board DIP switches.

Broadcast Controlspecifies how much Global Data the GENI will broadcast each bus scan. The range is 0Data Lengthto 128 bytes; the default is 0. GENI will automatically provide this value, and the<br/>Directed Control Data Length, to any device that sends it a Read ID Datagram.

Directed Controlspecifies how much data GENI will accept in the Directed Control Input Table each busData Lengthscan. The range is 0 to 128 bytes; the default is 0.

Reference Address this can be set by the host to desired value. Usually, it represents a logical reference that may correspond to the host memory location where the host stores I/O data from GENI. The GENI doesn't use the Reference Address itself. Rather, it passes the information to any device that requests it. The address should be set to a byte boundary. The default is OFFFF hex. For values compatible with the Series Six PLC, see the PLC Bus Controller User's Manual.

### 4-1

I/O Buffer Length the length of each buffer in the device I/O Tables. The default buffer length is 128 bytes. Shortening the buffer length (all buffers are the same length), shortens the entire I/O Table. The buffer length may be 1 to 128 bytes. The length selected must be long enough to accommodate any device's inputs and outputs (including Global Data and Directed Control Inputs data). GENI will not log in any device that sends or receives more data than will fit into its I/O Table buffer.

### **Example Variables**

The following Status Table variables might be defined for a C language interface to GENI.

```

typedef

struct {

unsigned char DipSwitch; /* GENI board DIP switch value */

unsigned int ST_addr; /* Reference Address */

unsigned char BCD_length; /* broadcast control data length */

unsigned char DCD_length; /* directed control data length */

unsigned char IOTable; /* length of each I/O table buffer */

unsigned char Reserved[10]; /* currently undefined */

```

} SETUP\_GENI;

## **Changing the Setup Table**

During the powerup sequence, the host must not read or write to the Shared RAM for 1.7 seconds. After that time, the GENI OK flag should be on, indicating that the self-test has passed. The GENI will set this flag within 2 seconds of powerup. After the GENI OK flag is set, there is an additional 1.5 second delay. During this time, the host can change the GENI configuration.

The host can change any item in the GENI Setup Table except the DIP switch value by sending the GENI a Change Configuration Command.

First, the host must first change the intended item(s) in the GENI Setup Table. Then, the host must send GENI a Configuration Change command, in the Command Block area of Shared RAM. See the chapter "GENI Commands" for more information.

To change any DIP switch value, it is necessary to reset the DIP switch, then cycle power to the GENI board or reset then release the reset. In the case of a Device Number conflict, the Device Number can be changed without cycling power or resetting the board.

# **Read ID Requests to GENI**

Another device on the bus may request setup information from GENI. It does that by sending GENI a Read ID datagram. GENI replies automatically, sending the contents of the GENI Setup Table in form of a Read ID Reply datagram. The reply is sent with high priority. This occurs automatically; it requires no host interaction.

Chapter 5 GENI Status

### GFK-0073

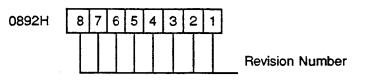

To read diagnostic information about GENI and about the bus, use the GENI Status Table. The GENI Status Table occupies 16 bytes of Shared RAM, starting at location 2194D/0892H. It contains the following information:

| Location  | Byte No.         | Description                         |

|-----------|------------------|-------------------------------------|

| 0892H     | 1                | GENI Revision Number                |

| 0893H     | 2                | GENI OK Status                      |

| 0894H     | 3                | GENI Hardware Status                |

| 0895H     | 4                | HHM Present                         |

| 0896H     | 5                | Serial Bus Error Count (lsb)        |

| 0897H     | 6                | Serial Bus Error Count (msb)        |

| 0898H     | 7                | I/O Scan Time in Milliseconds (lsb) |

| 0899H     | 8                | I/O Scan Time in Milliseconds (msb) |

| 089A-089F | 8 bytes reserved |                                     |

### **GENI Software Revision Number**

Shared RAM location 0892H contains the revision number of the GENI software.

The default is **OFFFF** hex.

### **GENI OK Status**

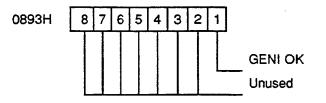

Shared RAM location 0893H indicates the status of the GENI board. GENI automatically sets this byte to "1" every 200 mS. The host can read this byte, then reset it. This would act as a continuous check (a 'heartbeat') on the normal operation of the GENI.

The default is 0FFFF hex.

5-1

### **GENI Hardware Status**

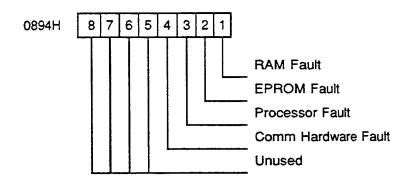

Byte 0894H indicates the status of the GENI hardware. The GENI runs self-tests periodically as part of its normal operation. If an error occurs during one of these self-tests, the GENI immediately stops all processing. Individual bits in this byte indicate the type of error that has occurred. If any of these bits is set and the host has the Status Change Interrupt enabled, the GENI OK bit (see "GENI OK Status", above) is cleared and an interrupt may be generated.

### Hand-held Monitor Connected to GENI Bus Controller

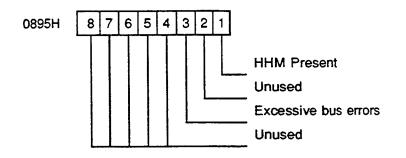

Bit 1 of byte 0895H (illustrated below) indicates that a Hand-held Monitor has been directly attached to the HHM connector on the motherboard.

### **Excessive Bus Errors**

Bit 3 of byte 0895H flags excessive bus errors (10 or more in a 10-second interval). This is not a fatal condition; however, it indicates a bus problem and may cause an interrupt to the host. The total bus error count is contained in the next two status bytes.

### **Bus Error Count**

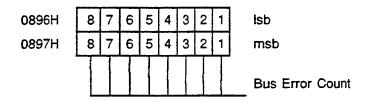

Bytes 0896 and 0897H form an integer count of the total bus errors. At powerup, this count is 0. If any bus errors occur, GENI increments this count. As errors occur over multiple bus scans, the total count increases to a maximum of 65535. If this total is reached, the count wraps back to 0.

### **Bus Scan Time**

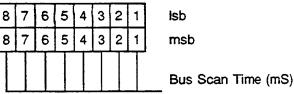

Bytes 0898 and 0898H of Shared RAM form an integer count of the bus scan time. This milliseconds value is updated each bus scan. It represents the amount of time between GENI's two previous turns on the bus. If GENI cannot access the bus, the value is set to 65535 (FFFFH). The host can monitor these locations to verify that GENI is communicating on the bus.

0898H 0899H

# **Example Variables**

The following Status Table variables might be defined for a C language interface to GENI.

```

typedef

struct

{

/* GENI revision number */

unsigned char Revision

unsigned char GENI_OK;

/* every 200mS, set to one */

/* overall fault byte */

unsigned char Fault;

/* HHM Present...excessive 1.o.*/

unsigned char Active;

/* bus error count */

unsigned int

Sberr;

Scan;

/* I/O scan time (mS) */

unsigned int

/* currently undefined */

unsigned char Reserved[8];

```

} GENI\_STATUS

ζ,

,

GENI automatically flags the occurrence of:

- a new datagram in the Request Queue

- a new datagram in the Receive Queue

- a change in GENI status

- a change in bus device status

- GENI passing the bus token

- a host request for I/O Table Lockout

In addition to maintaining a status table containing these flags, GENI will send an interrupt to the host for any interrupt condition, if enabled.

Two adjacent areas of Shared RAM are used to enable/disable interrupts from GENI to the host, and to monitor the current status of the interrupt flags.

#### **Interrupt Status Table**

The Interrupt Status Table begins at Shared RAM location 2210D/08A2H. It contains the current status of each interrupt flag.

#### **Disable Interrupt Table**

The Disable Interrupt Table begins at Shared RAM location 2226D/08B2H. It is used to enable or disable sending interrupts to the host for these conditions

### **Example Variables**

The following interrupt variables might be defined for a C language interface to GENI. The same variable names can be used for the Interrupt Status Table and the Disable Interrupt Table.

```

typedef unsigned char INTERRUPT[16];

/* not used */

/* summary byte for Interrupt Table */

#define I SUMMARY

0

#define I_REQUEST Q

/* Request Queue entry */

1

/* GENI status change */

#define I GENI STAT

2

3

/* device status change */

#define I DEV STAT

/* outputs sent */

#define I OUT SENT

4

/* command from host complete */

/* Receive Queue not empty */

#define I CCOMPLETE

5

6

#define I RECEIVE_Q

#define I_LOCKOGRANT 7

/* lockout request received */

```

### 6-1

## **Interrupt Table**

The least significant bits of bytes 08A2H through 08A9H contain the interrupt status flags. GENI sets these flags to indicate the status of interrupt conditions. The corresponding Interrupt Disable table (see next page) determines which of them will also cause GENI to send an interrupt to the host.

The host can monitor the Interrupt Status Table for changes in the interrupt status flags. The first byte of the table is a summary byte, which indicates whether any other interrupt flag is currently set.

The host must clear the interrupt flag after servicing an interrupt condition, even if the host interrupt is disabled.

| Location  | Interrupt Flag               | Description                                                                                                                                                                                                                                                                                                                                            |

|-----------|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 08A2H     | Interrupt Summary            | The host can monitor the lsb of the Interrupt Summary<br>byte to determine when an interrupt condition has<br>occurred. If this bit is 1, looking at the rest of the<br>interrupt flags will identify the specific interrupt<br>condition. The host must then clear the summary bit<br>(lsb of 08A2) and the individual interrupt bit that was<br>set. |

| 08A3H     | Request Queue Entry Flag     | Set if GENI has placed an incoming memory access<br>Datagram in the Request Queue.                                                                                                                                                                                                                                                                     |

| 08A4H     | GENI Status Change Flag      | Set if GENI Status Table byte 0894 indicates a GENI status change, or if byte 0895H, bit 3, indicates excessive bus errors.                                                                                                                                                                                                                            |

| 08A5H     | Device Status Change Flag    | Set if a device on the bus logs in, logs out, or changes<br>its configuration data.                                                                                                                                                                                                                                                                    |

| 08A6H     | Outputs Sent Flag            | Set each time the GENI bus controller passes the<br>implicit bus token to the next device. This indicates<br>that host outputs have been sent by the bus controller to<br>the devices on the bus. If needed, this interrupt status<br>indication can be used to synchronize the bus scan.                                                              |

| 08A7H     | Command Complete Flag        | Set when GENI has completed a task previously<br>commanded by the host in the Command Block.                                                                                                                                                                                                                                                           |

| 08A8H     | Receive Queue Not Empty Flag | Set if GENI has placed an incoming datagram in its<br>Receive Queue. The host can read it using a Read<br>Datagram command.                                                                                                                                                                                                                            |